可編程邏輯陣列(PLA)有什么用?

可編程邏輯陣列(Programmable Logic Array,PLA)是一種數字邏輯電路,具有可編程的邏輯功能。它在許多應用中具有廣泛的用途,包括但不限于以下幾個方面:

1. 邏輯功能實現:PLA可以根據用戶的需要進行編程,實現各種邏輯功能。通過編程,可以將多個邏輯門(如與門、或門、非門等)和觸發(fā)器組合在一起,構建復雜的數字邏輯電路。這樣,PLA可以靈活地實現各種邏輯功能,如加法器、計數器、寄存器等。

2. 邏輯修正和優(yōu)化:PLA允許在運行時對邏輯功能進行修改和優(yōu)化。通過重新編程PLA,可以輕松調整邏輯電路的功能或修復邏輯錯誤,而不需要重新設計和制造硬件。這種可編程性使得PLA在設計階段或產品更新階段具有很大的靈活性和便利性。

3. 邏輯實驗和原型驗證:PLA可用于模擬和驗證數字邏輯電路的設計。通過編程PLA,可以快速搭建原型電路,以驗證和檢驗設計的正確性和功能。PLA還可以在實驗室環(huán)境中用于教學和研究,幫助學生和研究者理解和掌握數字邏輯電路的原理和應用。

4. 邏輯單元集成:PLA在芯片設計中扮演重要角色,它可以將多個邏輯功能集成到一個芯片中,降低系統(tǒng)復雜性,提高集成度和性能。通過使用PLA,可以減少電路板上的組件數量、減小尺寸和功耗,并提高系統(tǒng)的可靠性和可維護性。

5. 靈活性和可重構性:PLA具有高度的靈活性和可重構性。它可以按照用戶的需求進行編程和配置,以適應不同的應用和需求。這使得PLA在產品開發(fā)和生產中具有較高的適應性和可定制化特性。

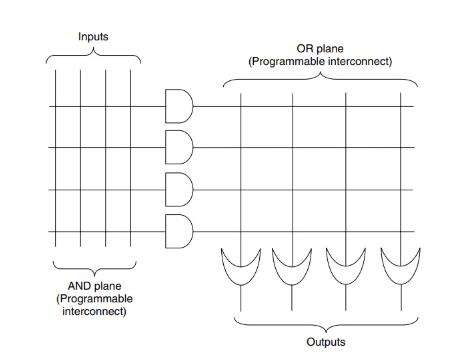

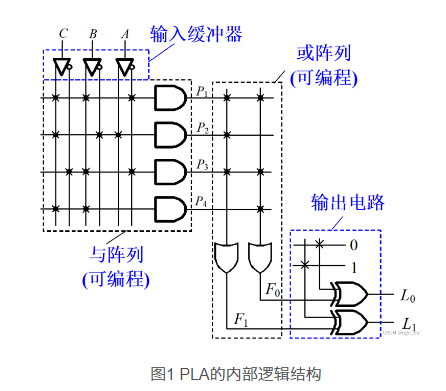

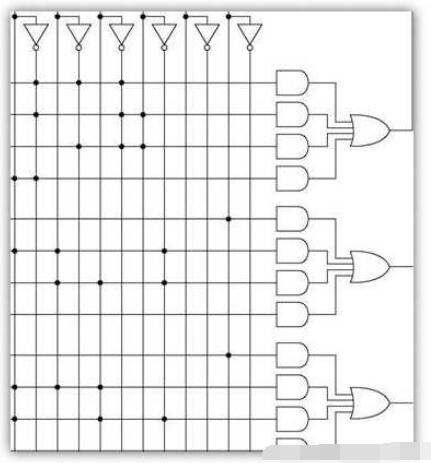

PLA由具有可編程互連的AND門平面和具有可編程互連的OR門平面組成,下面是一個簡單的四輸入四輸出PLA,帶有AND及OR門。

可編程邏輯陣列(PLA)

PLA由具有可編程互連的AND門平面和具有可編程互連的OR門平面組成,下面是一個簡單的四輸入四輸出PLA,帶有AND及OR門。

可編程邏輯陣列PLA的缺點

雖然可編程邏輯陣列(PLA)在許多應用中具有廣泛的用途和優(yōu)勢,但也存在一些缺點,包括:

1. 有限的可編程資源:PLA的可編程資源是有限的,包括可編程邏輯和觸發(fā)器的數量。這意味著在設計復雜的邏輯功能時,可能會受到資源的限制。當需要實現非常復雜的邏輯功能時,PLA可能無法提供足夠的資源來滿足需求。

2. 有限的靈活性:雖然PLA具有一定程度的靈活性,允許在運行時對邏輯功能進行修改和優(yōu)化,但這種靈活性仍然受到編程器或編程環(huán)境的限制。不同類型的PLA可能有不同的編程限制,例如只能進行某些特定類型的邏輯功能編程,不能隨意更改已編程的邏輯功能等。

3. 耗時的編程過程:PLA的編程過程相對比較復雜和耗時。需要使用特定的編程器或編程工具,以及了解編程語言和編程規(guī)則。對于大規(guī)模的PLA,在編程和配置所有邏輯功能之前,可能需要較長的時間進行設計、調試和驗證。

4. 難以調試和故障排除:由于PLA的邏輯功能是由編程決定的,當遇到邏輯錯誤時,調試和故障排除可能會比較困難。由于PLA內部是不可見的,很難直接檢查和驗證內部邏輯的正確性。因此,如果在PLA中有錯誤或故障,可能需要通過重新編程和重新設計來解決問題。

5. 成本高昂:與其他固定邏輯電路相比,PLA的成本較高。由于PLA具有可編程性和靈活性,需要較多的電路資源和設計工作。這使得PLA的制造和購買成本相對較高,不適用于一些低成本和簡單應用。

雖然存在一些缺點,但PLA仍然是數字邏輯電路設計中常用的工具之一,其優(yōu)勢在許多應用場景下仍然具有重要價值。對于特定的應用需求,需要權衡PLA的優(yōu)點和缺點,并根據具體情況選擇合適的設計工具和方法。

審核編輯:黃飛

-

芯片設計

+關注

關注

15文章

1028瀏覽量

55010 -

可編程邏輯

+關注

關注

7文章

517瀏覽量

44184 -

編程器

+關注

關注

9文章

398瀏覽量

42425 -

PLA

+關注

關注

0文章

38瀏覽量

17088 -

數字邏輯電路

+關注

關注

0文章

106瀏覽量

15876

發(fā)布評論請先 登錄

相關推薦

可編程邏輯陣列PLA內部邏輯結構示意

求大佬分享一種基于可編程邏輯陣列的RS232至RS422的串行口擴展電路

可編程系統(tǒng)芯片的設計構架

基于可編程邏輯陣列的RS232至RS422的串行口擴展電路

開關電容器現場可編程模擬陣列的頻域SPICE仿真

現場可編程門陣列的供電原理及應用

可編程陣列邏輯(Programmable Array Log

可編程邏輯陣列(PLA)簡介

可編程陣列邏輯的構造及運用

可編程邏輯器件測試方法

可編程邏輯陣列(PLA)有什么用?

可編程邏輯陣列(PLA)有什么用?

評論