數(shù)字減法器電路的基本原理

對(duì)于兩個(gè)二進(jìn)制數(shù) x 和 y,用“x-y”表示他們的二進(jìn)制差,其結(jié)果有如下四種情形:

(1)0-0=0;(2)1-0=1;(3)1-1=0;(4)10-1=1。

對(duì)于上述四種情形中的 “10-1=1”的特殊情形,也即是當(dāng) x=10(即十進(jìn)制的 2),y=1 時(shí),它們的二進(jìn)制差為 1,這表明在二進(jìn)制減法中,作差過程存在向前一位借位的情形。

串行進(jìn)位減法器電路

一個(gè) n 位串行進(jìn)位減法器是由 n 個(gè)全減器的借位位首尾相連、依次串聯(lián)在一起形成的,在串行進(jìn)位減法器中,其借位從最低有效位( Least Significant Bit,LSB)傳到其最高有效位(Most Significant Bit,MSB)需要很長的的時(shí)間(電路的延時(shí))。

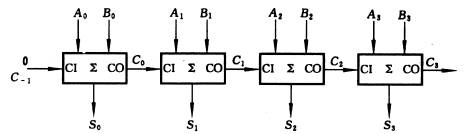

圖1 四位串行進(jìn)位減法器邏輯電路圖

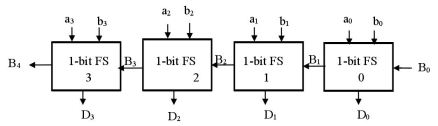

圖2 四位串行進(jìn)位減法器的符號(hào)

圖1、圖2分別是一個(gè)四位的串行進(jìn)位減法器邏輯電路圖和符號(hào),其中 a i 、bi和 Bi是輸入位,D i 、Bi+1是輸出位,且 Bi+1作為更高位的輸入位。

串行進(jìn)位減法器電路的主要優(yōu)點(diǎn)是:結(jié)構(gòu)簡(jiǎn)單、便于連接和 IC 版圖設(shè)計(jì)的實(shí)現(xiàn);但其缺點(diǎn)是:執(zhí)行運(yùn)算速度較慢。這是因?yàn)榇羞M(jìn)位減法器電路每一位的相減必須等到它前一位的計(jì)算結(jié)果,最高位相減必須要等到它前面的所有位都完成相減才能進(jìn)行。

由于全減器只有在它的輸入位有效時(shí)它的輸出結(jié)果才是有效的,最左端的電路是最后響應(yīng)的,這樣全減器的輸出結(jié)果才是正確的。

因此,串行進(jìn)位減法器電路總的延時(shí)取決于每一個(gè)全減器電路的信號(hào)傳輸延時(shí),而信號(hào)的傳輸延時(shí)又與邏輯門的工藝有關(guān),所以串行進(jìn)位減法器電路的時(shí)間延時(shí)和電路中邏輯門的工藝相關(guān)。

-

邏輯電路

+關(guān)注

關(guān)注

13文章

494瀏覽量

42709 -

二進(jìn)制

+關(guān)注

關(guān)注

2文章

796瀏覽量

41757 -

減法器

+關(guān)注

關(guān)注

1文章

26瀏覽量

16878 -

全減器

+關(guān)注

關(guān)注

0文章

4瀏覽量

4884

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)字電路中加法器和減法器邏輯圖分析

減法器電路與原理 減法器電路圖分享

8位減法器求解?

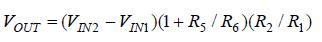

哪一個(gè)是減法器?負(fù)反饋在減法器電路中的原理?

串行進(jìn)位加法器

本的二進(jìn)制加法/減法器,本的二進(jìn)制加法/減法器原理

減法器電路

8位加法器和減法器設(shè)計(jì)實(shí)習(xí)報(bào)告

減法器電路設(shè)計(jì)方案匯總(五款模擬電路設(shè)計(jì)原理圖詳解)

串行進(jìn)位減法器電路設(shè)計(jì)

串行進(jìn)位減法器電路設(shè)計(jì)

評(píng)論