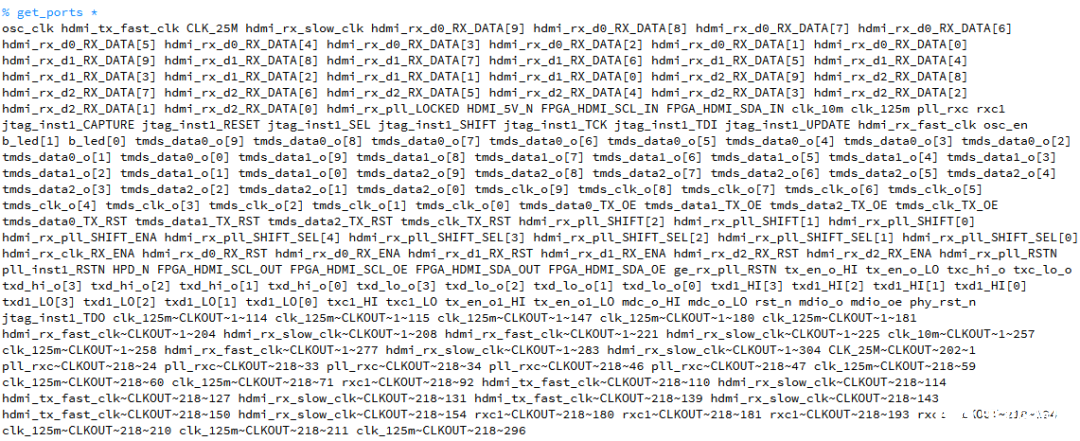

通過get_port命令查看接口。

get_ports *

以LVDS的輸入輸出為例

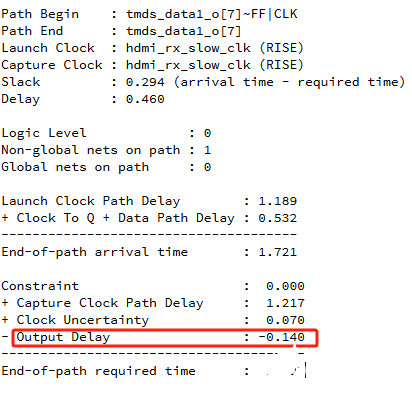

怎樣去查看outputdelay

set_output_delay -clock hdmi_rx_slow_clk -reference_pin [get_ports {hdmi_rx_slow_clk~CLKOUT~218~131}] -min -0.140 [get_ports {tmds_data0_o[*]}]在tcl command Console中輸入以下語句,可以查看到它的約束情況。

report_timing -through [get_pins {tmds_data1_o[*]~FF|Q}] -hold

Tmds_data1_o是一個LVDS的輸出接口,hold使用的是min 值,setup使用的是max值 。如果有多條路徑可以使用-npaths.

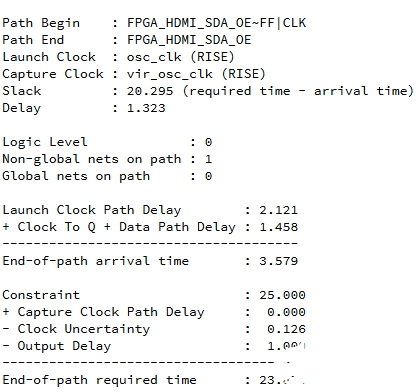

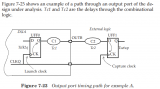

可以看到在約束中已經把Output Delay在Caputure Path中減去。當然我認為加在Launch Path Delay中也是可以的。

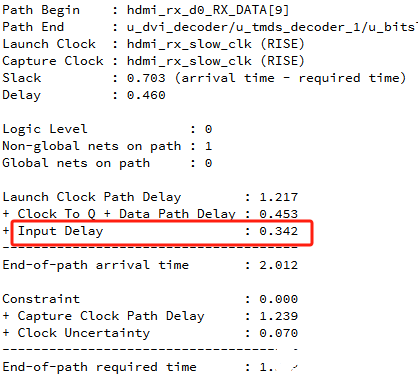

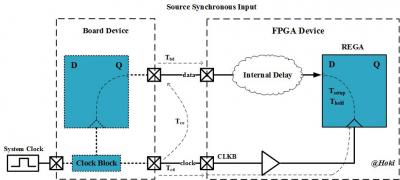

怎樣去查看input delay是否生效

set_input_delay -clock hdmi_rx_slow_clk -reference_pin [get_ports {hdmi_rx_slow_clk~CLKOUT~1~283}] -max 0.512 [get_ports {hdmi_rx_d0_RX_DATA[*]}]set_input_delay -clock hdmi_rx_slow_clk -reference_pin [get_ports {hdmi_rx_slow_clk~CLKOUT~1~283}] -min 0.342 [get_ports {hdmi_rx_d0_RX_DATA[*]}]set_input_delay -clock hdmi_rx_slow_clk -reference_pin [get_ports {hdmi_rx_slow_clk~CLKOUT~1~208}] -max 0.512 [get_ports {hdmi_rx_d1_RX_DATA[*]}]set_input_delay -clock hdmi_rx_slow_clk -reference_pin [get_ports {hdmi_rx_slow_clk~CLKOUT~1~208}] -min 0.342 [get_ports {hdmi_rx_d1_RX_DATA[*]}]set_input_delay -clock hdmi_rx_slow_clk -reference_pin [get_ports {hdmi_rx_slow_clk~CLKOUT~1~225}] -max 0.512 [get_ports {hdmi_rx_d2_RX_DATA[*]}]set_input_delay -clock hdmi_rx_slow_clk -reference_pin [get_ports {hdmi_rx_slow_clk~CLKOUT~1~225}] -min 0.342 [get_ports {hdmi_rx_d2_RX_DATA[*]}]

在tcl command Console中輸入以下語句,可以查看到它的約束情況。 report_timing -from [get_ports {hdmi_rx_d0_RX_DATA[*]}] -hold hdmi_rx_d0_RX_DATA[*]是一個lvds的輸入接口,hold使用的是min 值,setup使用的是max值 。如果有多條路徑可以使用-npaths.

可以看到在約束中已經把Input Delay在Launch Path中加上。

對于單端

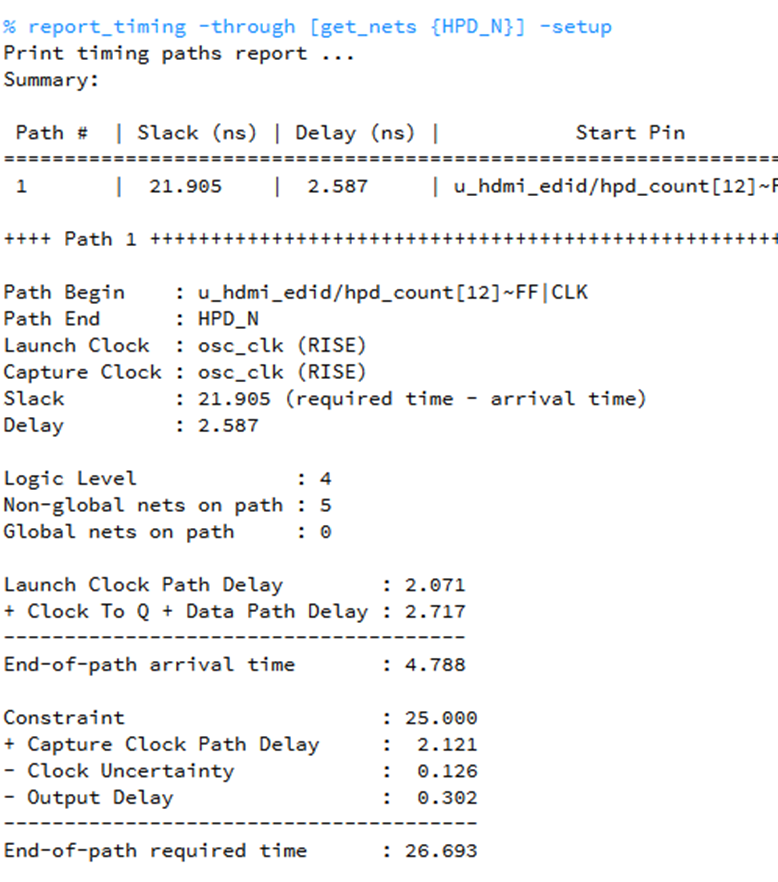

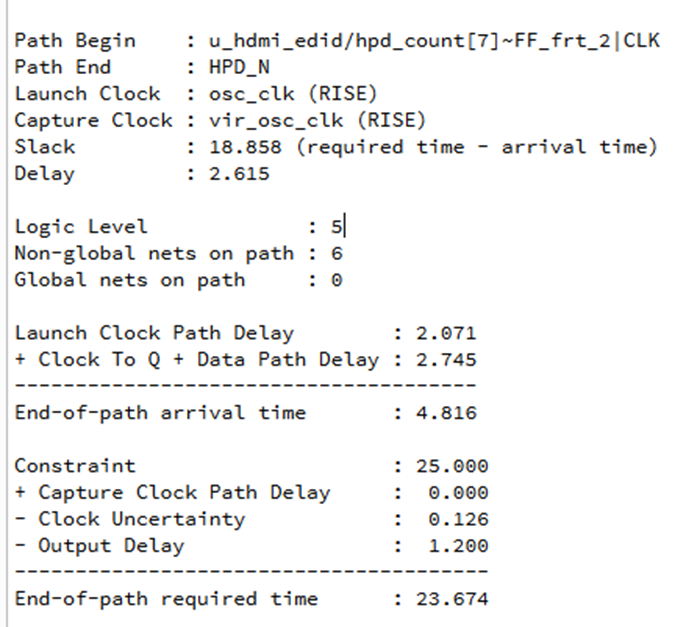

當HPD_N是同步IO時。

這里使用的時鐘是osc_clk

HPD_N是一個單端非同步輸出信號

create_clock -period 25 [get_ports {osc_clk}]

create_clock -period 25 -name vir_osc_clk

set_output_delay -clock vir_osc_clk -max 1.2 [get_ports {HPD_N}] set_output_delay -clock vir_osc_clk -min 1.0 [get_ports {HPD_N}] 在tcl command Console中輸入以下語句,可以查看到它的約束情況。

report_timing -through [get_nets {HPD_N}]

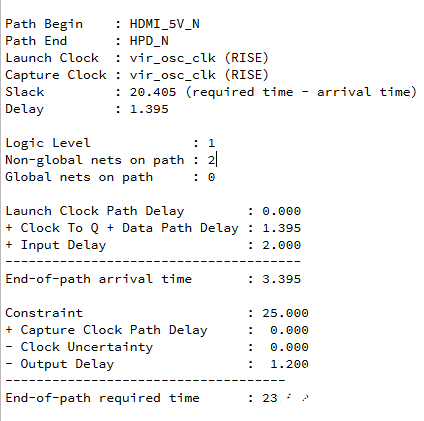

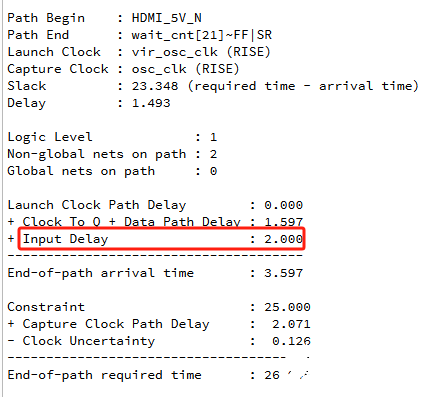

從時序報告中我們可以看到launch clock path delay是2.071,它的值是GBUF的延時,而capture clock path delay是0,說明參考點是在GBUF之前 。 HDMI_5V_N是單端輸入信號 添加約束

從時序報告中我們可以看到launch clock path delay是2.071,它的值是GBUF的延時,而capture clock path delay是0,說明參考點是在GBUF之前 。 HDMI_5V_N是單端輸入信號 添加約束

set_input_delay -clock vir_osc_clk -max 2.0 [get_ports {HDMI_5V_N}]set_input_delay -clock vir_osc_clk -min 1.8 [get_ports {HDMI_5V_N}]

通過以下指令來打印信息

report_timing -from [get_ports {HDMI_5V_N}]

使用npaths可以打印出多條路徑。

程序上實現如下:

assign hdmi_rx_hpd_n = ~hdmi_rx_5v_n ? 1'b0 : rx_hpd;

第二條

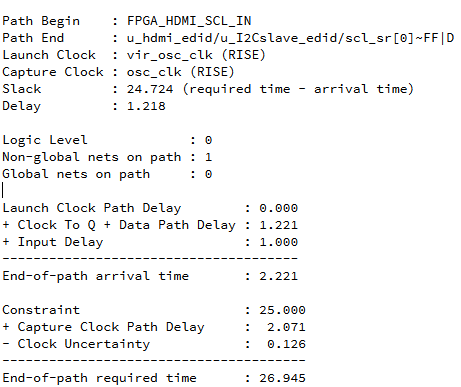

三態信號

report_timing -from [get_ports {FPGA_HDMI_SCL_IN}]

report_timing -to [get_nets {FPGA_HDMI_SDA_OE}]

審核編輯 黃宇

-

接口

+關注

關注

33文章

8691瀏覽量

151912 -

Output

+關注

關注

0文章

31瀏覽量

10535 -

Delay

+關注

關注

0文章

10瀏覽量

10908

發布評論請先 登錄

相關推薦

FPGA靜態時序分析——IO口時序(Input Delay /output Delay)

IC中inout port需要同時設置input_delay和output_delay嗎?

input_delay應該設置為多少?

Input and Output Capacitor Sel

AD9514: 1.6 GHz Clock Distribution IC, Dividers, Delay Adjust, Three Output Data Sheet

詳解FPGA的時序input delay約束

set_output_delay的本質是什么?淺談set_ouput_delay時序

MAX14906: Quad-Channel Industrial Digital Output, Digital Input Data Sheet MAX14906: Quad-Channel Industrial Digital Output, Digital Input D

怎樣查看input/output delay是否生效

怎樣查看input/output delay是否生效

評論