你想寫出可以跑出700M以上的代碼嗎,直逼FPGA內部PLL的極限。

你想寫出時序裕量足夠的代碼嗎,讓你的代碼不會出現時序違例。

你想在時序違例時能輕松應對嗎?讓代碼輕松越過時序這道門檻。

這篇文章就是一步步向你解釋,如何理解代碼中的時序,以及如何解決代碼中的時序違例問題。

之前的文章中提到過,工程中ISP算法模塊輕松跑到了762.5M的頻率,整個ISP鏈路沒有優化的情況下跑到400M的時鐘頻率(xilinx的us+系列)。

這篇文章將逐步解開HDL代碼中的時序之謎,并且讓你輕松應對FPGA中的時序問題。我將從實際工程的ISP算法模塊出發,從設計到時序違例的查找,一步步提高代碼的時序性能。

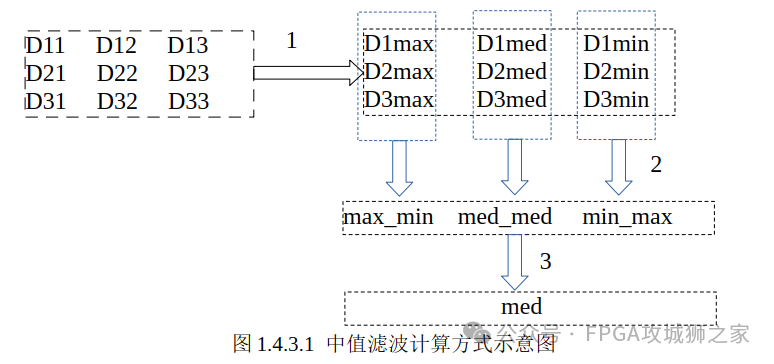

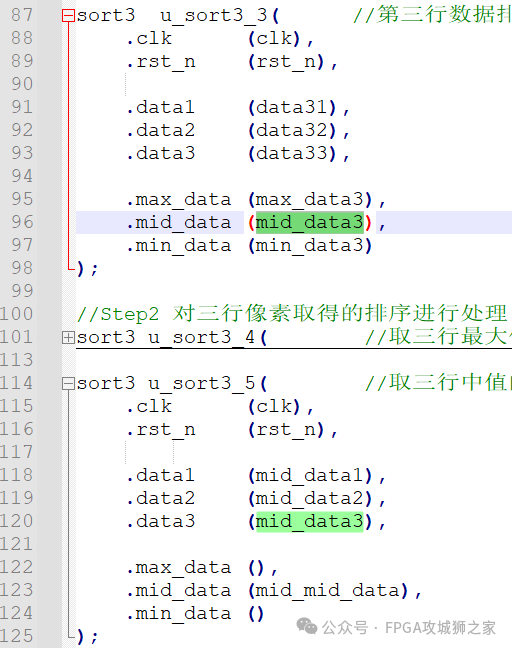

在第一個ISP模塊DPC中,我使用了一個在3x3的矩陣中查找中值的模塊,也就是大家常用的中值濾波器。是不是很多人都設計過,先不著急覺得是否簡單,而是看如何把算法移植和時序的思想灌入到這個模塊之中。

首先假設你已經得到了一個3x3的矩陣,簡單看看設計思想:

在3x3 窗口中獲取9 個數據,對9 這個數據值進行排序,排序步驟如下

A)窗內的每行數據找到最大值、中間值和最小值;

B)把三列的最小值相比較,取其中的最大值;

C)把三列的最大值相比較,取其中的最小值;

D)把三列的中間值相比較,再取一次中間值;

E) 再把B,C,D 中得到的三個值再排序,獲取中值。

有了設計思想就有了靈魂,剩下的是如何構建一個有血有肉的軀體了。經過思考不難發現,9個數的中值濾波變成了3次在3個數中找最大值,最小值,中值。

第一次:執行步驟A。

第二次:執行步驟B,C,D .

第三次:執行E 。

第一次三行D1,D2,D3并行,第二次三列Dxmax,Dxmed,Dxmin并行,第三次在剩下的三個數里面找到中值,運算完畢。所以9個數據的中值查找的設計,變成了一個只需要解決三個數據里面找到max,med,min的設計。

是不是覺得這太簡單了。別急,聽我繼續分析:

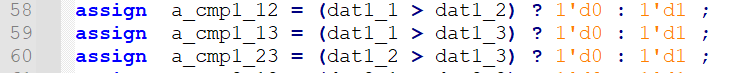

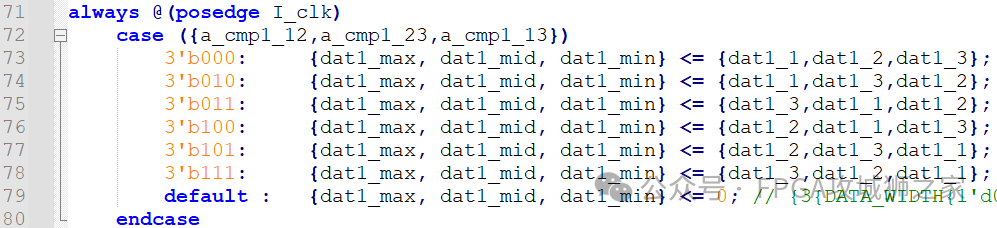

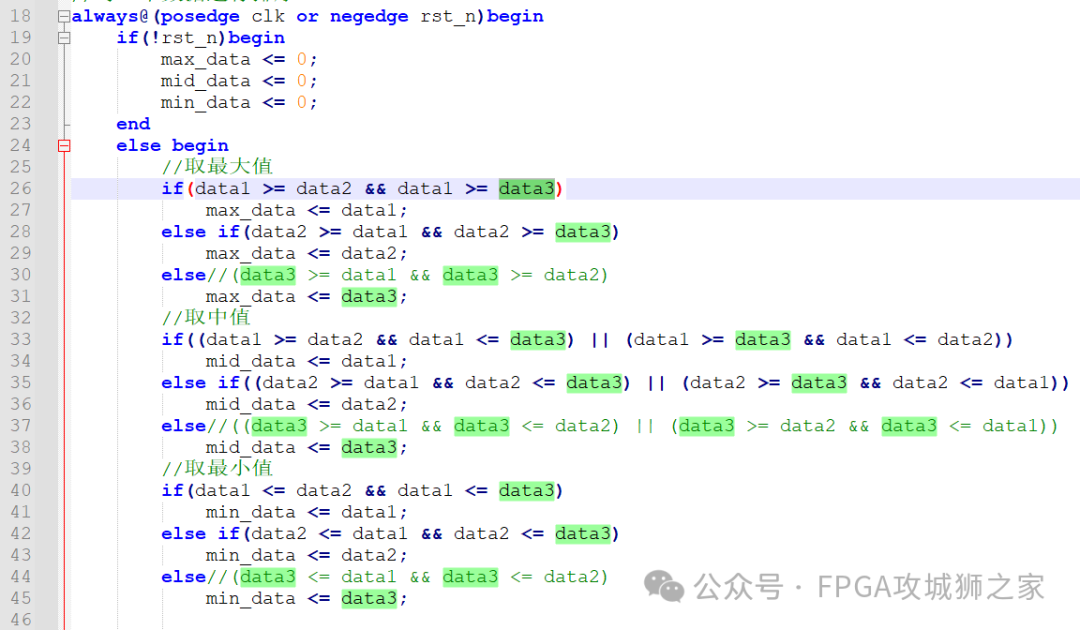

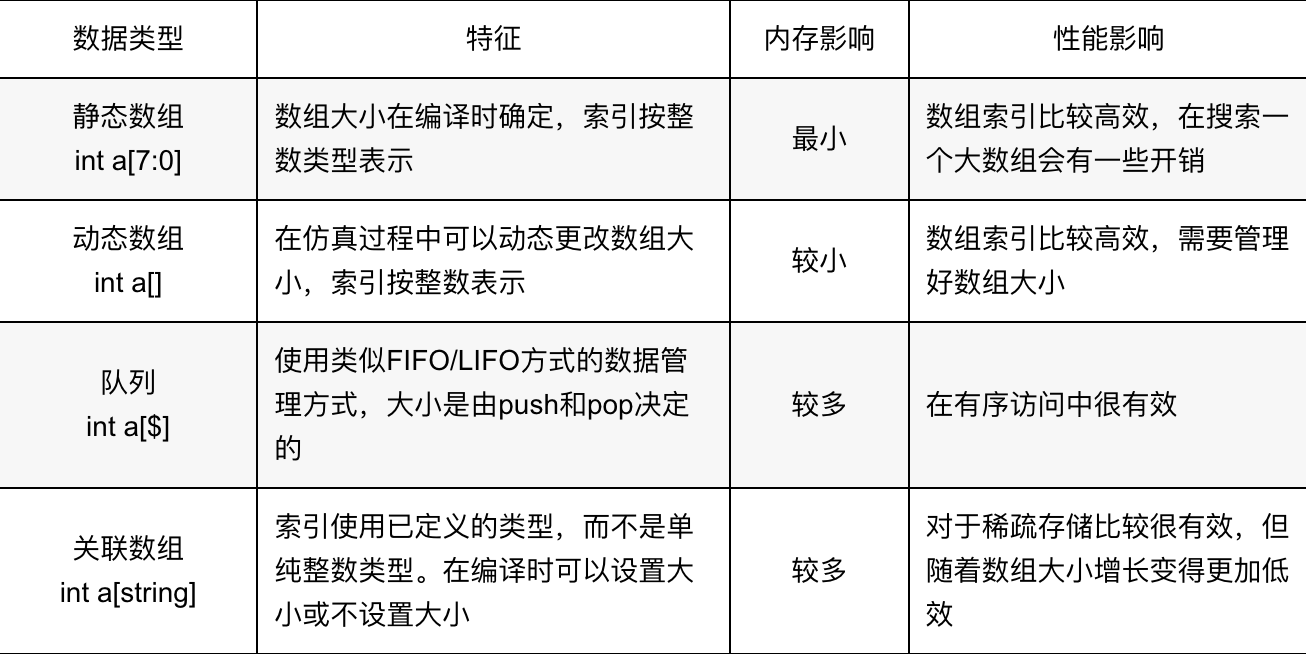

既然是在三個數據里面排序,那就需要兩兩比較,于是就是需要比較3次。A 與B ,B與C,A與C。現在假設A

好,此時另一個誤區可能就要出現了。因為flag可能為0也可能為1,那么你得到了三個flag,一共有多少種情況呢?可能有人不假思索地回答8種,因為3bit數據,2^3= 8 ,所以就是8 種。其實不是,用概率與統計的知識,三個數據的排序應該是有C31* C21 * C11 = 6 種。真值表如下

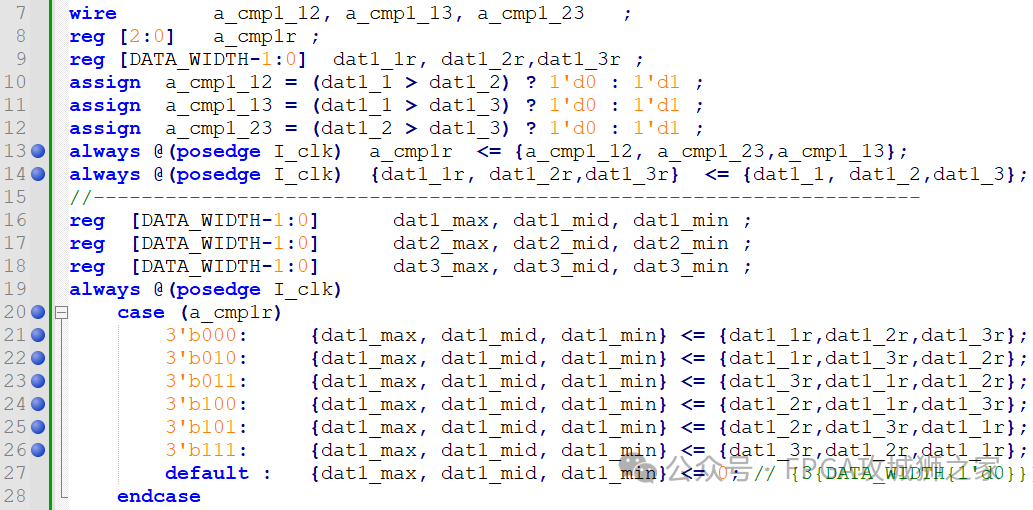

算法分析完畢,剩下的就是代碼設計了。首先你需要進行三次比較。

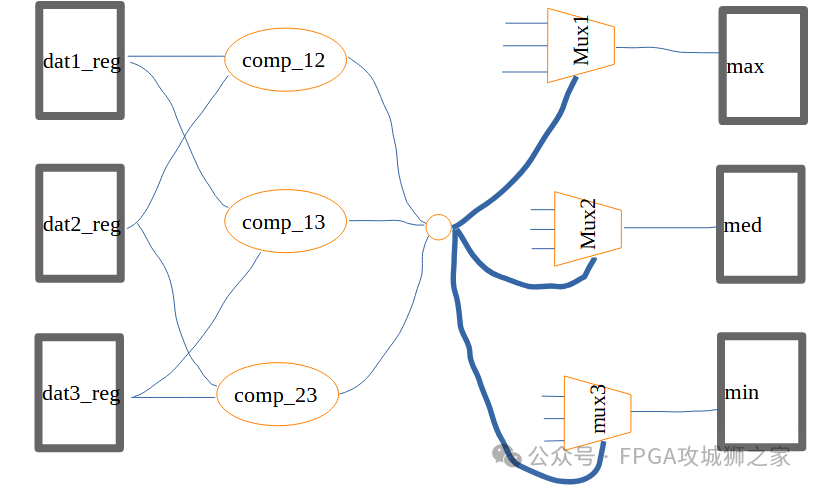

針對上述代碼,畫出對應的數字電路示意圖,(mux的三個輸入端省略了datx_reg)

我假設FPGA內部按照上圖所示的方式進行布局布線,那么最長數據路徑應該是dat2_reg→comp_12 → mux3. (或者說是dat2_reg→ comp_23 → mux1)這條路徑也就被稱之為最長路徑或者關鍵路徑。時序分析工具干的事情就是,分析這條最長路徑(當然其他路徑也分析)上的時序是否滿足條件。

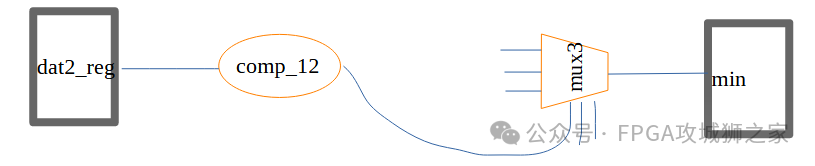

單獨把這條路徑摳出來,它就是這樣子的。于是,STA靜態時序分析的模型就出來了,計算reg到reg之間的延遲,兩個reg之間,經歷了一個比較器和一個多路選擇器這兩個組合邏輯。

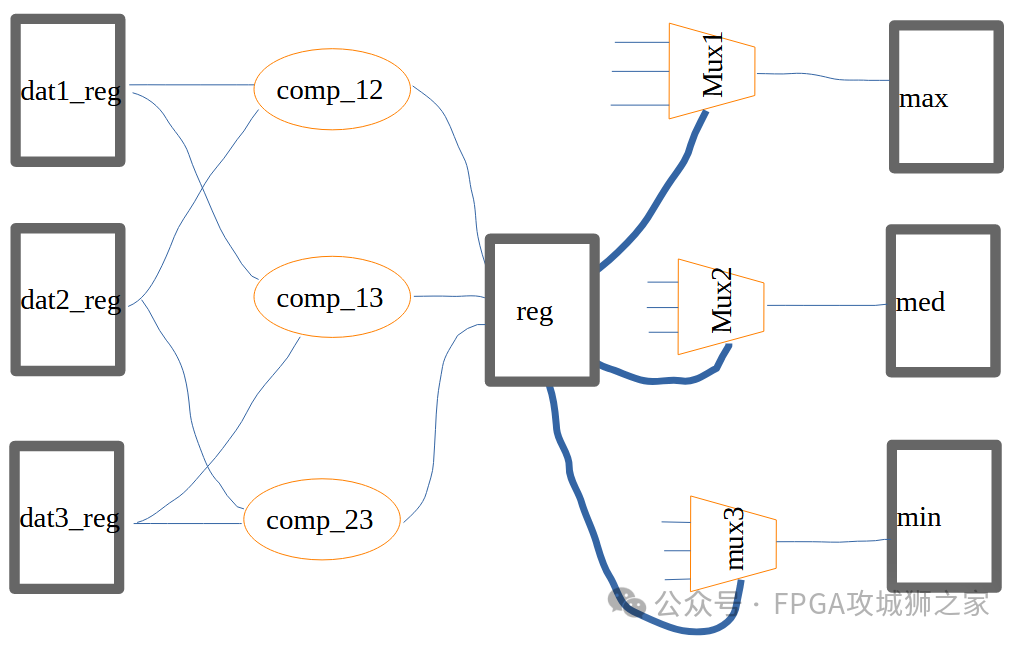

如果上述的路徑因為走線(linelatency)延遲,或者是因為邏輯延遲(logiclatency)過大導致了時序違例,那么我們就應該在兩個組合邏輯之間插入reg。從電路上,應該如下圖所示。

那么從代碼的角度,應該這樣修改,就可以達到上圖的效果:

好了,有了這個參考模板,再去看其他的中值濾波代碼,你就知道要從哪里去優化了。

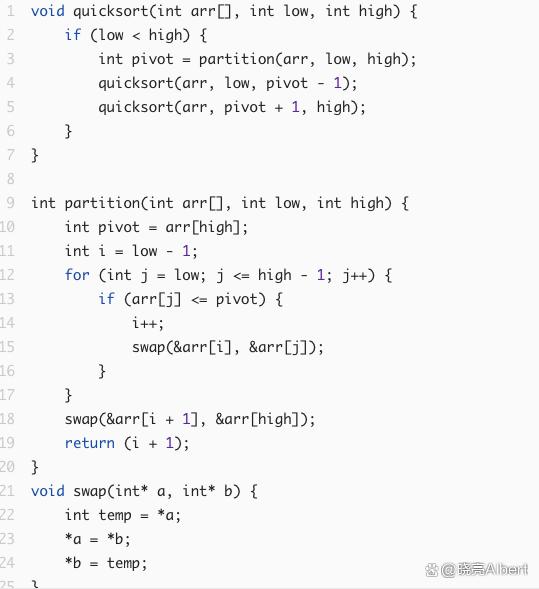

為了讓大家更好的理解時序,我在網上找了兩個用相同的算法思路設計的開源的代碼。看他們的設計方法

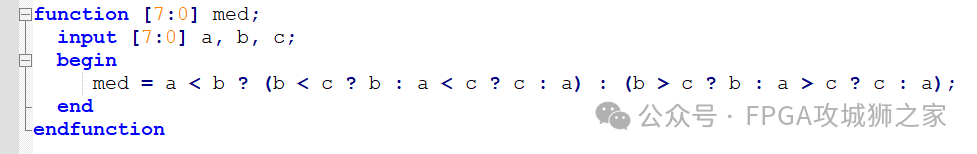

三方代碼 1

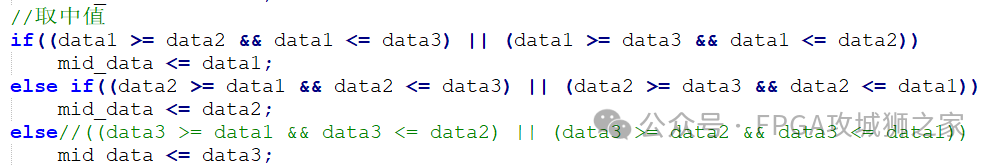

三方代碼 2

可以看到數據比較的時候,邏輯明顯有冗余,EDA工具不一定能自動優化。

然后我將兩個三方的代碼,以及我自己的代碼放入同一工程中進行編譯,故意加大時鐘頻率,讓它們出現時序違例,從而找出關鍵路徑。

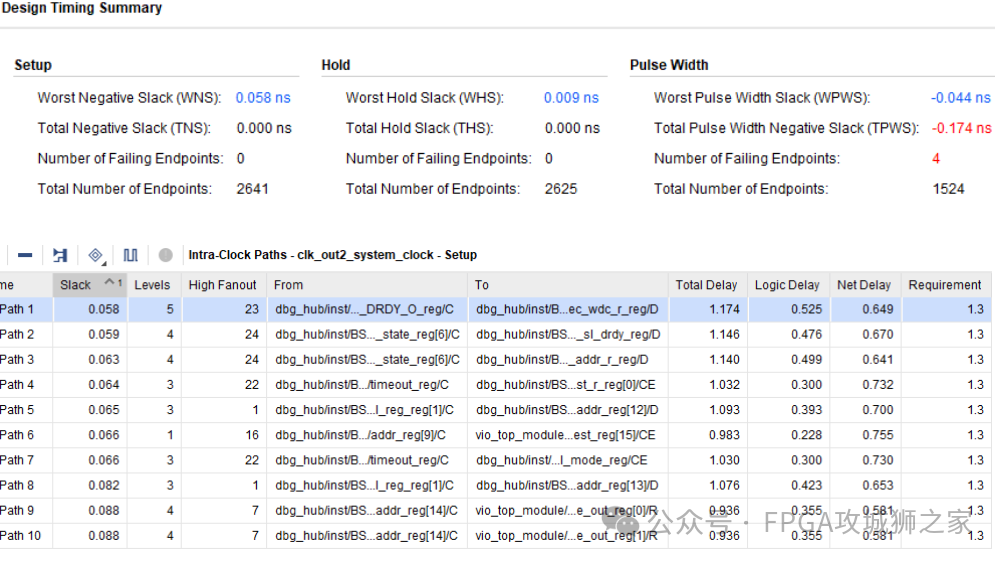

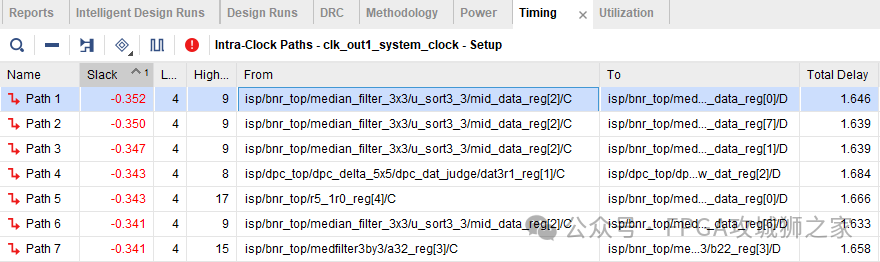

三方的兩個模塊我例化成 median_filter_3x3 ,和 medfilter3by3 ,用vivado2022.1進行編譯。得到時序違例報告

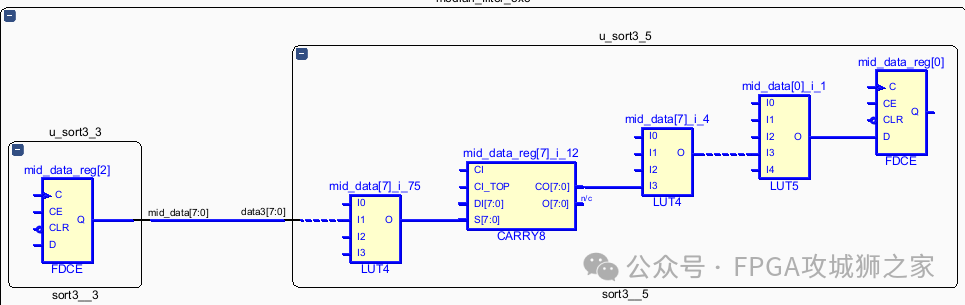

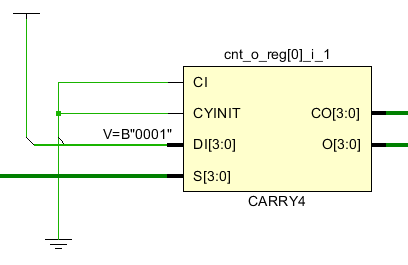

再進一步分析關聯路徑1,得到了如下圖所示的路徑示意圖

可以看到在兩個 reg之間有4個邏輯塊,然后再去代碼中找到相應的位置。然后再追究到代碼內部。

可以看到,代碼中多次出現重復性的數據比較,這都是數據優化的方向。具體的位置就是 33-37行,最后vivado推測出第37行,需要經過4級組合邏輯才能將dat3 賦值給 mid_dat 。

A

B

A

0

0

0

max=A,min = C

0

0

1

不存在

0

1

0

max=A,min = B

0

1

1

max=C,min = B

1

0

0

max=B,min = C

1

0

1

max=B,min = A

1

1

0

不存在

1

1

1

max=C,min = A

審核編輯:劉清

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605996 -

濾波器

+關注

關注

161文章

7860瀏覽量

178928 -

比較器

+關注

關注

14文章

1658瀏覽量

107428 -

HDL

+關注

關注

8文章

328瀏覽量

47468 -

PLL電路

+關注

關注

0文章

92瀏覽量

6473

原文標題:基于FPGA的 ISP代碼精講1 —— 如何寫出時序最優的HDL代碼

文章出處:【微信號:gh_99a29eb83412,微信公眾號:FPGA攻城獅之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何寫出可以讓人理解的代碼(以verilog語言為例)?

如何寫出高效并且簡潔易于閱讀的單片機C語言代碼呢?

如何寫DA轉化代碼

C語言如何寫出高效代碼呢?

如何寫出穩定的單片機代碼

如何寫出時序最優的HDL代碼?如何寫出時序裕量足夠的代碼?

如何寫出時序最優的HDL代碼?如何寫出時序裕量足夠的代碼?

評論