FPGA芯片主要使用的編程語言包括Verilog HDL和VHDL。這兩種語言都是硬件描述語言,用于描述數字系統的結構和行為。

Verilog HDL:應用最為廣泛的硬件描述語言。它主要用于描述邏輯電路圖、邏輯表達等,也應用于算法級、門級到開關級的多種數字系統建模。Verilog HDL的使用相對嚴謹,可用于各種層次的邏輯設計,數字系統的邏輯綜合,仿真驗證和時序分析等。

VHDL:是一種用于電路設計的高級語言,主要應用在數字電路的領域。VHDL的硬件描述語言以及其描述風格都和高級計算機語言較為相似,但學習起來可能相對困難一些。

此外,SystemVerilog也是一種FPGA編程中使用的語言,它是建立在Verilog語言基礎之上的,結合了硬件描述語言(HDL)與現代的高層級驗證語言(HVL),成為下一代硬件設計和驗證的語言。

盡管有些計算機編程語言如C/C++、Java、Python等在軟件設計中常用,但FPGA編程語言屬于硬件編程語言,因此在使用FPGA編程語言時不能照搬軟件設計思路。

總的來說,FPGA的編程語言主要是為了描述和定義硬件的行為和結構,以滿足特定的設計需求。具體選擇哪種語言,通常取決于設計者的偏好、項目的需求以及目標FPGA的特性。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605973 -

芯片

+關注

關注

456文章

51166瀏覽量

427205 -

編程語言

+關注

關注

10文章

1950瀏覽量

34979

發布評論請先 登錄

相關推薦

FPGA編程語言的設計

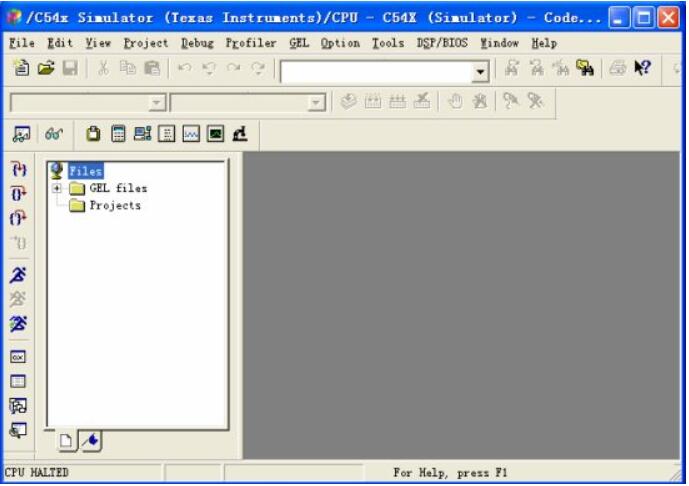

dsp編程用什么語言_dsp編程如何實現的

fpga芯片用什么編程語言

fpga芯片用什么編程語言

評論