FPGA驗證和UVM驗證在芯片設計和驗證過程中都扮演著重要的角色,但它們之間存在明顯的區別。

FPGA驗證主要指的是利用FPGA(現場可編程門陣列)芯片進行硬件設計和驗證的過程。FPGA作為一種可編程邏輯器件,能夠允許用戶通過編程配置其內部邏輯結構,從而快速實現并驗證特定的硬件功能。在FPGA驗證中,設計者通常會將待驗證的硬件設計映射到FPGA上,通過實際運行來驗證設計的正確性和性能。這種驗證方式具有高度的靈活性和可定制性,能夠快速適應設計變更,并且在實際硬件環境中進行測試,可以更接近實際運行狀況。

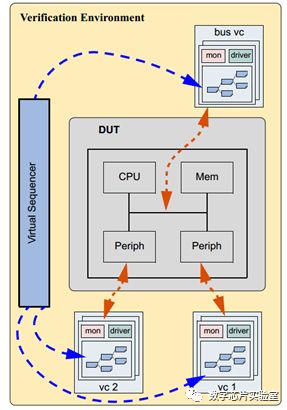

相比之下,UVM(Universal Verification Methodology)驗證則是一種基于軟件仿真的驗證方法。UVM是一種通用的驗證方法論,它提供了一套標準化的驗證組件和接口,使得驗證工作更加規范化、高效化。在UVM驗證中,驗證人員會使用高級編程語言(如SystemVerilog)編寫測試用例和驗證環境,通過仿真器對設計進行模擬運行,以檢查設計的正確性和潛在問題。UVM驗證具有高度的可重復性和可擴展性,能夠支持大規模的驗證工作,并且可以在設計早期階段就進行驗證,有助于提前發現潛在問題。

因此,FPGA驗證和UVM驗證的主要區別在于驗證方式和應用場景。FPGA驗證更側重于在實際硬件環境中進行測試和驗證,能夠更接近真實運行情況;而UVM驗證則更側重于通過軟件仿真進行驗證,具有更高的靈活性和可擴展性。在實際應用中,設計者通常會結合使用這兩種驗證方法,以充分利用各自的優勢,提高驗證工作的效率和準確性。

總之,FPGA驗證和UVM驗證都是芯片設計和驗證過程中不可或缺的環節。它們各有特點,相互補充,共同確保芯片設計的正確性和可靠性。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605970 -

芯片設計

+關注

關注

15文章

1028瀏覽量

55004 -

UVM

+關注

關注

0文章

182瀏覽量

19227

發布評論請先 登錄

相關推薦

IC驗證"為什么要學習UVM呢"

IC驗證"UVM驗證平臺"組成(三)

IC驗證"一個簡單的UVM驗證平臺"是如何搭建的(六)

IC驗證"UVM驗證平臺加入factory機制"(六)

IC驗證“UVM驗證平臺加入objection機制和virtual interface機制“(七)

數字IC驗證之“UVM”基本概述、芯片驗證和驗證計劃(1)連載中...

數字IC驗證之“什么是UVM”“UVM的特點”“UVM提供哪些資源”(2)連載中...

UVM驗證平臺執行硬件加速

MathWorks通過Universal Verification Methodology (UVM)支持加快 FPGA和ASIC驗證速度

ASIC芯片設計之UVM驗證

數字IC驗證之UVM概述

fpga驗證和uvm驗證的區別

fpga驗證和uvm驗證的區別

評論