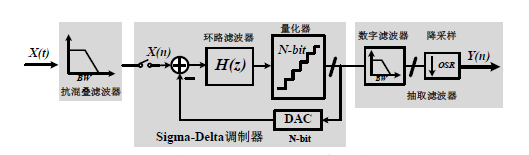

Δ技術可以用來實現 ΣΔADC 和 ΣΔDAC ,是高精度、低噪聲 ADC/DAC 的主流技術。要理解 ΣΔADC 和 ΣΔDAC ,需要按照以下順序來學習:

離散ΣΔ調制器 → ΣΔDAC

離散ΣΔ調制器 → 模擬ΣΔ調制器 → ΣΔADC

本文詳細講解離散ΣΔ調制器。閱讀后,你就能分析、設計 ΣΔDAC 。

本文會先為讀者建立足夠的知識鋪墊;然后從直觀理解和建模分析的角度講解離散ΣΔ調制器的原理,包括一階ΣΔ調制器和高階ΣΔ調制器;最后用 Python 編寫和評估一階、二階、三階離散ΣΔ調制器的性能。

本文涉及離散信號處理的知識,需要讀者熟悉z變換的一些概念(除非只關注結論)。

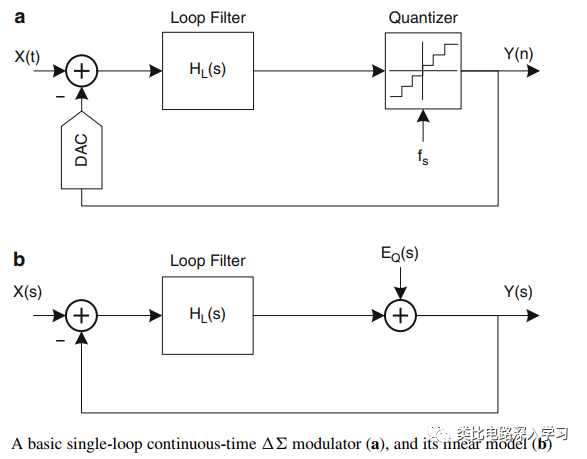

如果要進一步理解 ΣΔADC ,還需要閱讀 (下) 篇,理解模擬ΣΔ調制器:

ΣΔ(Sigma-Delta)技術詳解(下):模擬ΣΔ調制器73 贊同 · 12 評論文章

目錄

Ⅰ 基礎元件介紹

Ⅱ ADC的信噪比

Ⅲ ADC過采樣技術

Ⅳ 二值調制器

Ⅴ PWM調制器

Ⅵ 離散Δ調制器

Ⅶ 離散一階ΣΔ調制器

Ⅷ 離散高階ΣΔ調制器

Ⅸ 離散二階、三階ΣΔ調制器

Ⅹ 各種離散二值調制器的實現和評估

Ⅺ 總結

附:一階、二階、三階ΣΔ調制器的Python實現

Ⅰ 基礎元件介紹

本節介紹幾個離散信號處理中常見的元件,如表1。它們可以用計算機算法實現,也可以用數字電路(比如FPGA)來實現。例如,比例器、加法器、減法器可以用組合邏輯來實現,延遲器可以用D觸發器來實現。

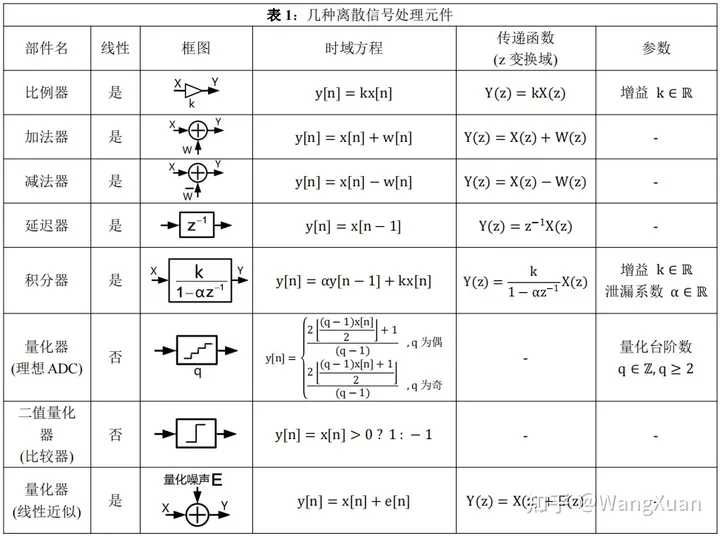

表1中的幾種線性元件不必多說。這里我們需要介紹一下這里唯一的非線性元件——量化器。我們知道,對連續信號 x(t) 以采樣周期 Ts=1/fs 采樣就能得到離散信號 x[n] :

x[1]=x(Ts),x[2]=x(2Ts),...,x[n]=x(nTs)

把連續信號采樣為離散信號……把連續信號采樣為離散信號(1)

而再對離散信號的幅度進行量化就能得到數字信號。量化器能把取任意實數的輸入信號 x[n] 轉化為取有限的 q 個實數的輸出信號 y[n] 。

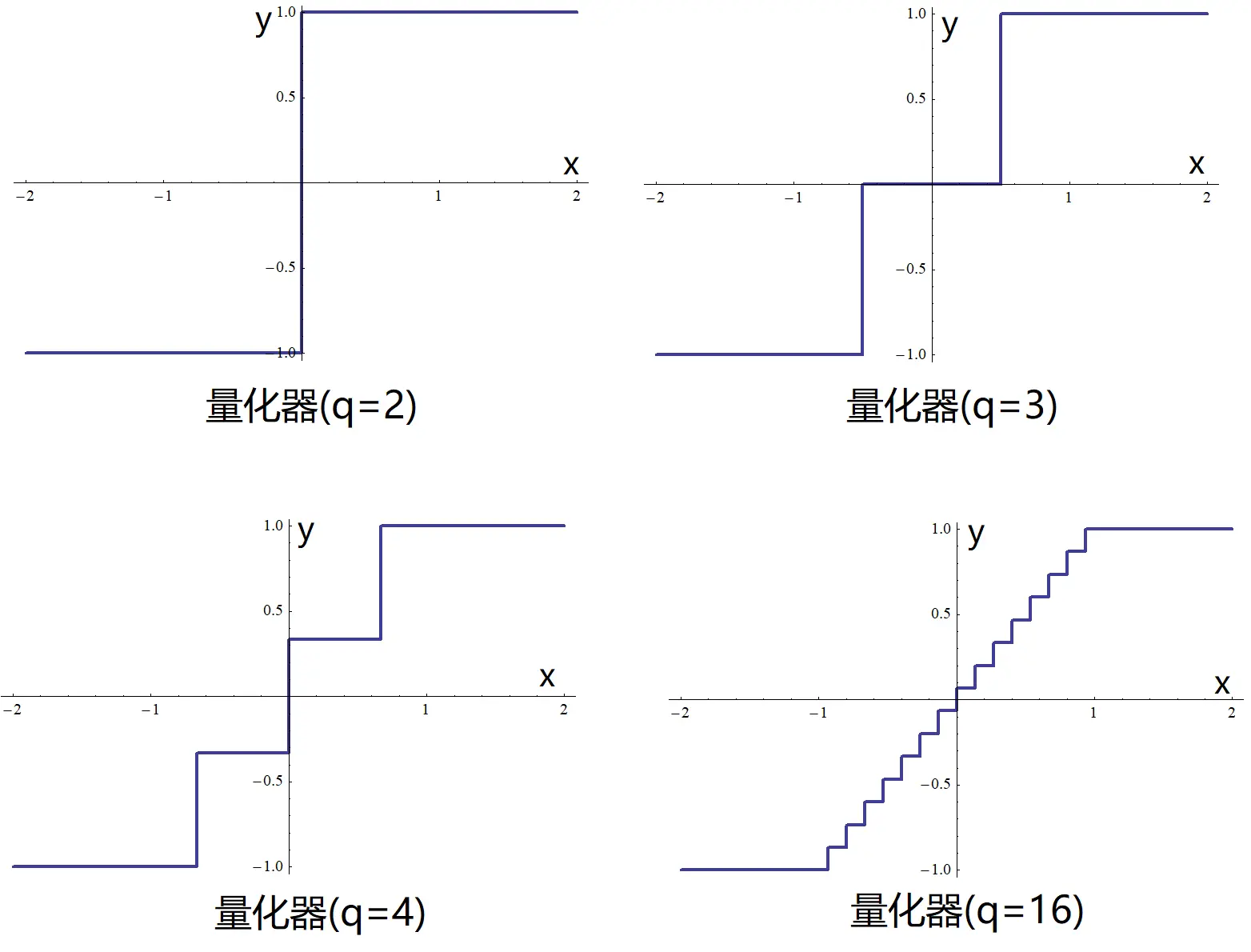

對于 q=2,3,4,16 的量化器,我們繪制它的輸入 x[n] 和輸出 y[n] 之間函數圖如圖1。可以看出q是函數圖中的“臺階數”。

圖1:量化器的函數圖。其中x軸是量化器的輸入,y軸是量化器的輸出。

量化器能把取值無限的離散信號轉化為取值有限的數字信號,因此也稱為理想ADC。比如,理想 10-bit ADC 就是 q=210=1024 的量化器。

之所以要理解量化器,是因為典型的離散ΣΔ調制器里面會用到一個二值量化器,它是 q=2 的量化器,它對于正數輸出+1,對于負數輸出-1,可以用比較器來實現。

量化器是非線性元件。眾所周知,非線性元件比較難以進行分析。所幸我們很多時候可以把量化器近似為線性元件:

量化器線性近似y[n]=x[n]+e[n]……量化器線性近似(2)

其中量化噪聲:

e[n]=y[n]?x[n]

這看似是個沒什么用的循環定義,不過有時候 e[n] 能近似為與 x[n] 無關的白噪聲,此時用線性近似 (2) 就能簡化分析。

另外,即使當 x[n] 超出范圍 [?1.0,+1.0] 時, y[n] 也會限制在 [?1.0,+1.0] 內,體現出限位器的特性。此時我們說量化器超量程了,此時量化噪聲 e[n] 會很大,在設計時要特別注意避免量化器的超量程。

Ⅱ ADC的信噪比

信噪比 (SNR) 是指系統輸入的信號功率與系統引入的噪聲功率之比,是衡量系統優劣的重要參數,越大越好。

下面我們來分析理想ADC(量化器)的 SNR 。它的噪聲全部來自量化噪聲 e[n] 。由圖1可知,相鄰兩個量化值之間相差:

δ=2/(q?1)

理想的相鄰兩個量化值之差的計算公式……理想ADC的相鄰兩個量化值之差δ的計算公式

在平均情況下,信號均勻分布在相鄰兩個量化值之間,根據均勻分布的方差,可以得出噪聲 e[n] 的功率為:

e2ˉ=δ212=13(q?1)2

理想的平均噪聲功率……理想ADC的平均噪聲功率(4)

我們向理想ADC輸入一個滿量程的正弦信號:

x[n]=sin(ωt+?)

該正弦信號的幅度為 [?1.0,+1.0] ,我們可以算出它的平均功率為:

Psin=limN→∞∑n=0Nx[n]2N=0.5

當該正弦信號 x[n] 通過理想 ADC 時,會疊加量化噪聲 (4) ,得到 SNR :

SNRsin=Psine2ˉ=0.513(q?1)2=32(q?1)2

理想信噪比……理想ADC信噪比

在工程中,我們習慣用分貝 (dB) 來表示 SNR :

SNRsin=10log10?(32(q?1)2)(dB)

=10log10?(32)+10log10?((q?1)2)(dB)

≈1.76+20log10?(q?1)(dB)

理想信噪比……理想ADC信噪比(5)

已知 N-bit 理想 ADC 的 q=2N ,代入公式(5)可以得到 N-bit 理想 ADC 的信噪比:

理想信噪比SNRsin≈1.76+6.02N(dB)……理想ADC信噪比(6)

實際ADC的噪聲來源不止是量化噪聲,還有電路引起的熱噪聲等,因此實際 N-bit 的 ADC 的 SNR 一定小于(6)。

為了評估實際ADC的優劣,我們往往在實驗中用滿量程正弦波輸入實際ADC,測出SNR,然后代入(6)反向計算出N,稱為ADC的有效位(ENOB)。ENOB代表了該ADC在測量滿量程正弦波時,SNR相當于多少bit的理想ADC。

注意:ENOB并不能代表ADC輸入直流時的分辨率,只能代表交流性能,而ADC的直流分辨率位數可能大于或小于它的ENOB。這部分內容不做贅述。

用公式(6)計算理想ADC的SNR前,一定要檢查兩個條件是否滿足:

條件①:ADC未超量程。否則 y[n] 和 x[n] 之差就會很大,量化噪聲 e[n] 就不能視作均勻分布于相鄰量化值之間,則公式(4)不成立,無法推導出公式(6) 。

條件②:輸入信號 x[n] 的幅度要遠大于相鄰兩個量化值之差 δ 。否則量化噪聲 e[n] 同樣不能視作均勻分布于相鄰量化值之間,公式(4)不成立,無法推導出公式(6) 。

注意:對于位數 N 很小的ADC, q 會很小,δ 會很大,條件②很容易被違反。其中二值量化器( N=1,q=2,δ=2 )是一個極端,完全無法套用公式(6)來計算SNR,其SNR會比公式(6)算出來的 7.78 dB 小很多。

Ⅲ ADC過采樣技術

設我們有一個采樣率為 fs 的ADC,然后輸入給該 ADC 一個帶寬為 fB 的模擬信號。眾所周知,ADC 的理論帶寬是奈奎斯特帶寬 fs/2 ,也即我們要滿足 fs/2>fB ,才能保證高頻部分不會混疊到低頻。

除了要保證 fs/2>fB 外,我們還可以使用 ADC過采樣技術來提高SNR。方法是:

選取采樣率更快的 ADC (更大的 fs ),讓 fs/2 遠大于fB ;

然后在 ADC 后加一個帶寬為 fB 數字低通濾波器。

考慮到 ADC 的量化噪聲和熱噪聲往往是白噪聲,均勻分布于奈奎斯特帶寬 [0,fs/2) 內。加了數字低通濾波器后, f∈[0,fB) 內的信號和噪聲被保留, f∈[fB,fs/2) 內的噪聲被濾掉。因此噪聲會降低到原來的 fs/(2fB) ,SNR 會提升 fs/(2fB) 倍:

過采樣原始SNR過采樣=SNR原始×fs2fB

在分貝標度上我們可以得到:

過采樣原始SNR過采樣=10log10?(SNR原始×fs2fB)(dB)

原始=SNR原始+10log10?fs2fB(dB)

過采樣技術帶來的信噪比提升……ADC過采樣技術帶來的信噪比提升(7)

這就是ADC的過采樣技術。其中我們稱 fs/(2fB) 為過采樣比。

公式(7)告訴我們,采樣率 fs 每提升10倍,SNR 就提升 10dB;采樣率 fs 每提升4倍,SNR 就提升 6.02dB,也即 ENOB 提升 1bit。

注意公式(7)成立的兩個條件:

條件①:使用的低通濾波器足夠理想,也即通帶和阻帶間增益足夠陡,阻帶的增益足夠小;

條件②:ADC 的噪聲近似白噪聲。

如果ADC的噪聲偏紅(更多地分布于低頻),由于低通濾波器無法濾掉這些低頻噪聲,則過采樣技術就收效甚微,無法獲得公式(7)那么多的SNR提升。

反之,若噪聲偏藍(更多地分布于高頻),過采樣技術就能獲得比公式(7)還好的SNR提升,本文要介紹的ΣΔADC 就用了該思路。

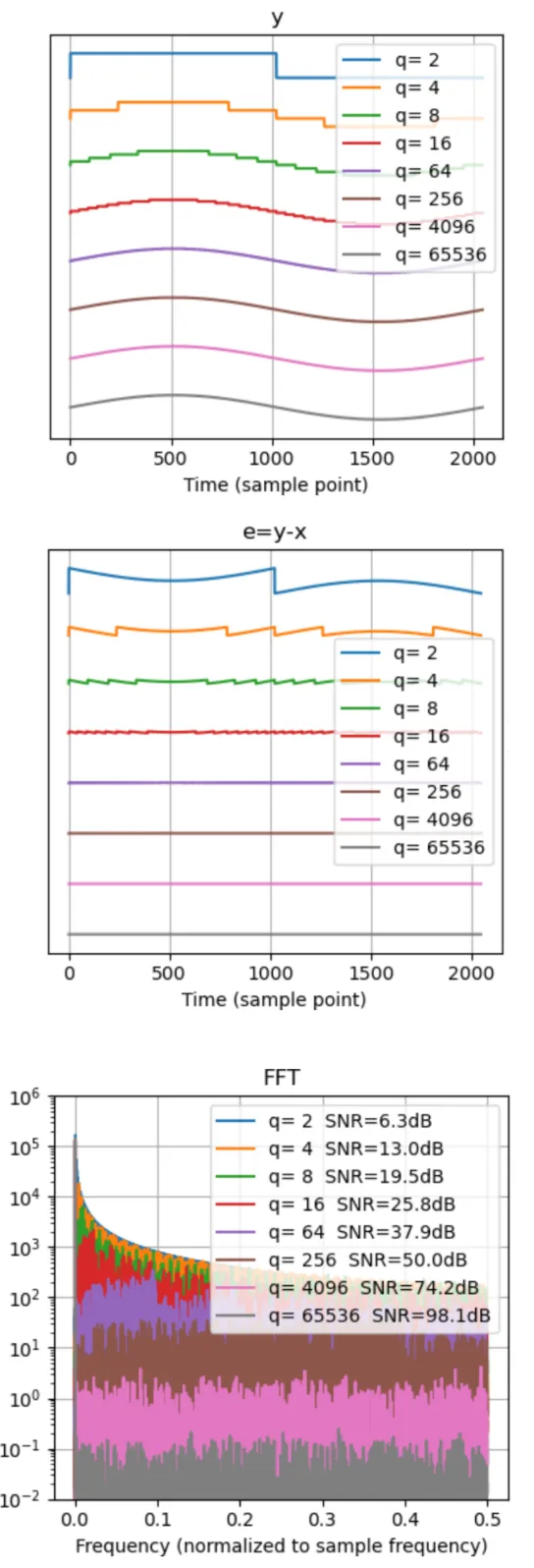

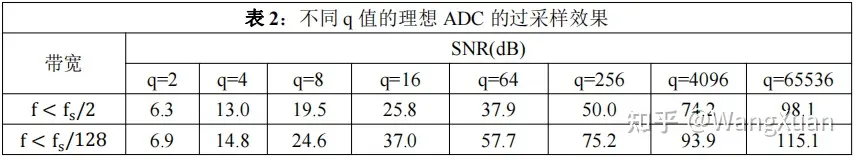

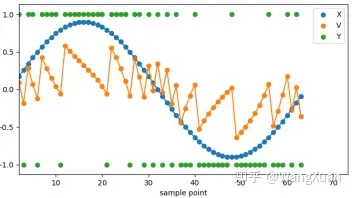

作為引子,我們看看對理想 ADC 使用過采樣技術達到的效果如何。我們把滿幅正弦波 x[n]=sin?(2πn/2048) 輸入不同 q 值的量化器,得到輸出 y[n] 如圖2(上)、量化噪聲 e[n] 如圖2(中)、y[n] 的 262144 個樣點的頻譜如圖2(下),并計算 SNR 展示在表2 第一行。

然后我們用過采樣技術,在頻譜上截取帶寬 f表2 第二行(相當于使用了理想低通濾波器)。根據公式(7)知,這樣可讓 SNR 提升 18dB,然而從表2 知,當 q 很小時,過采樣技術帶來的 SNR 提升遠不及 18dB。這是因為從圖2(中)可知,當量化不夠“細膩”,也就是 δ 不顯著小于 x[n] 的幅度時,量化噪聲 e[n] 與 x[n] 呈強相關,不能被近似為白噪聲,而是偏紅,導致過采樣技術收效甚微。

圖2:滿幅正弦波輸入理想ADC得到的時域輸出(上);量化噪聲(中);輸出的頻譜(下)

Ⅳ 二值調制器

二值調制器并不是一個元件,而是泛指一類能把輸入信號轉化為二值信號的元件。在本文中,二值信號是指取值僅為 -1.0 或 +1.0 的離散信號,也可以視為1bit數字信號。

衡量二值調制器的性能的方法是看它輸出的二值信號是否能在頻譜上盡量多的保留其輸入信號的信息。具體來說,我們對輸入信號和輸出信號分別做離散傅里葉變換(FFT),看它們的頻譜在一定帶寬內是否相似,越相似越好。

上一節介紹的二值量化器就是一種二值調制器,但它的性能并不好,因為其引入的量化噪聲 e[n] 主要分布于低頻(偏紅),和信號混在同一帶寬內,用低通濾波器并不能把大多數 e[n] 濾掉。

后文我們會看到幾種性能更好的二值調制器(PWM調制器、Δ調制器、ΣΔ調制器)。它們引入的噪聲 e[n] 呈現白色或藍色,用低通濾波器濾掉大多數高頻噪聲后,可以獲得較高的 SNR 。

二值調制器分為兩種:

離散二值調制器:輸入離散信號,輸出二值離散信號 (1bit數字信號) ,可用數字電路或計算機算法來實現。本文后文要講的PWM調制器、離散Δ調制器、離散ΣΔ調制器都屬于離散二值調制器。

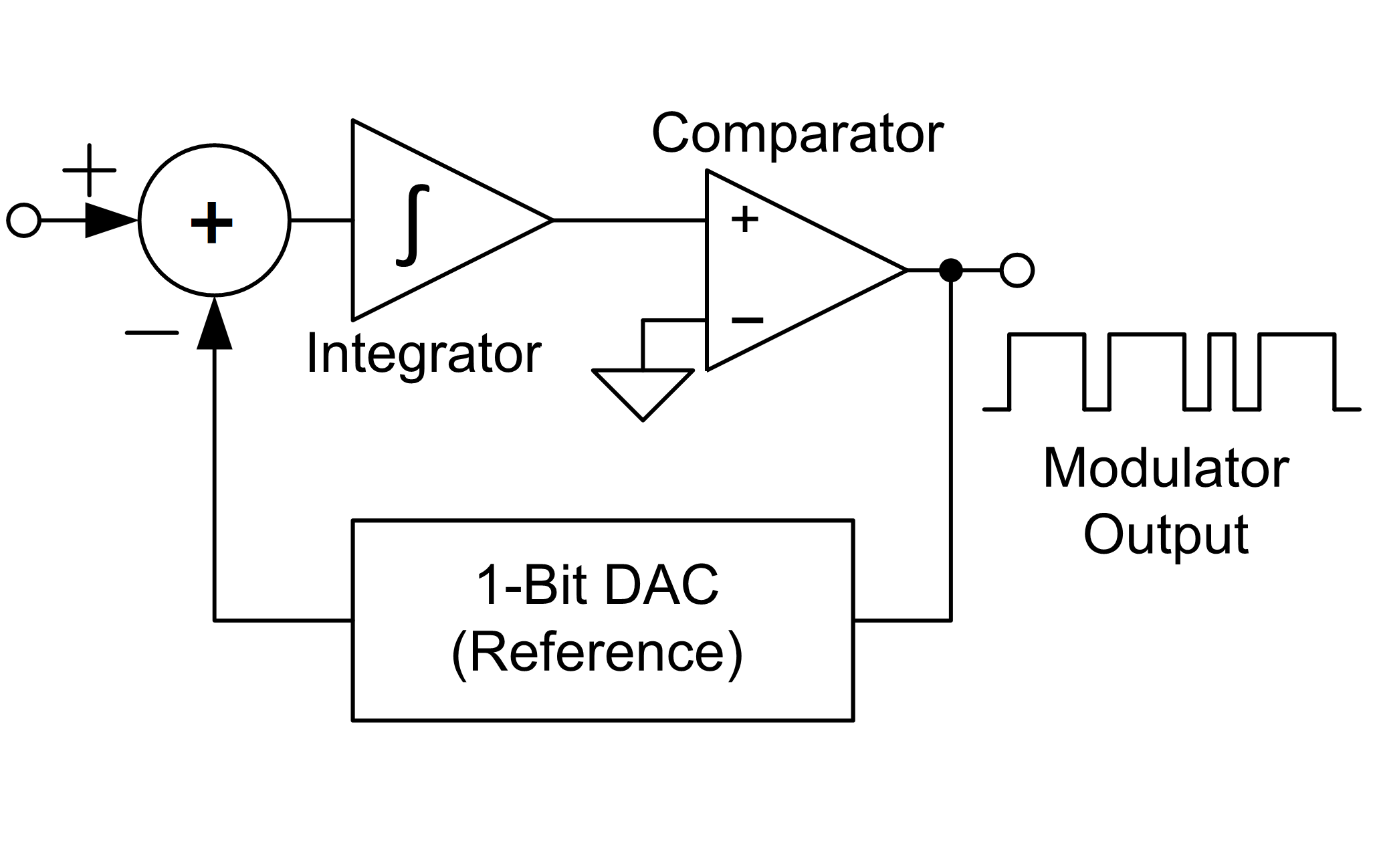

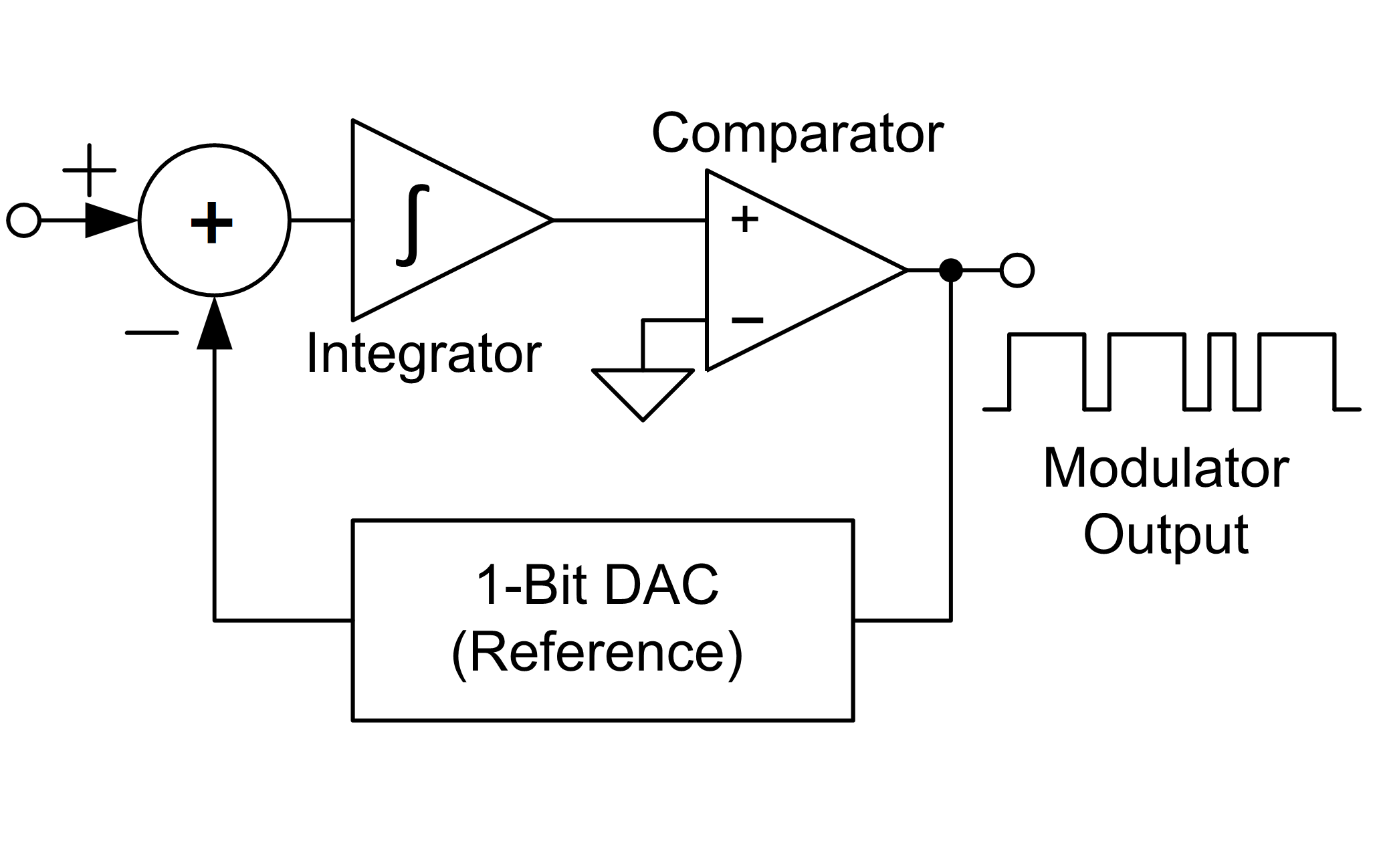

模擬二值調制器:輸入連續信號,輸出二值離散信號 (1bit數字信號) ,可用模數混合電路來實現。(下)篇文章中要講的模擬ΣΔ調制器就屬于模擬二值調制器。

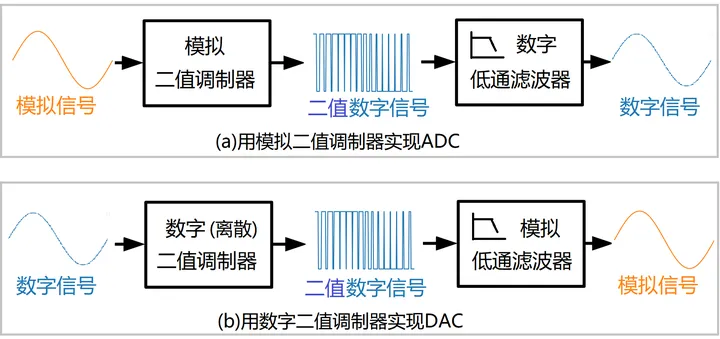

如圖3,模擬二值調制器可以用來實現ADC,離散二值化調制器可以用來實現DAC。后級都加了低通濾波器用來濾除二值信號中我們不關心的高頻噪聲,來盡量還原原始信號。

圖3:用二值調制器實現ADC和DAC

顯然,二值調制器的性能是這種 ADC 和 DAC 關鍵,因為如果二值調制器性能差,產生的二值信號在我們關心的低頻帶寬內混雜了過多的噪聲,那么即使低通濾波器再理想,也無法濾掉這種噪聲。

這也是為什么后文要花大篇幅來分析 離散ΣΔ調制器 ,掌握了離散ΣΔ調制器的分析方法,我們才能設計出 SNR 足夠高的 ΣΔDAC 。

相反,圖3中的低通濾波器設計相對簡單,只要滿足通帶和阻帶間增益足夠陡,阻帶的增益足夠小,它就能從二值信號中盡量濾掉我們不想要的高頻噪聲,保留低頻信號。濾波器的設計是《信號與系統》和《數字信號處理》中的基礎知識,而且 MatLab、Python 中有成熟的濾波器設計工具,因此本文不做贅述。

Ⅴ PWM調制器

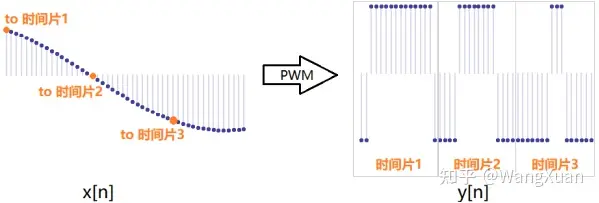

PWM調制器是一種最直觀的二值調制器。PWM調制器用直觀的“占空比”法來產生二值信號 y[n] 。如圖4,它把相鄰 m 個樣點視作一個時間片,在時間片內放置 r 個 +1 和 (m?r) 個 -1 ,因此該時間片內的均值是:

yˉ=1×r+(?1)×(m?r)m=2rm?1

其中 r 是占空比, 1m 是PWM頻率。它們都是算法或數字電路中可以改變的參數。通常我們保持 m 固定,通過改變 r 來讓 yˉ=x ,也即讓輸出信號在時間片內的均值等于輸入信號:

yˉ=x

?2rm?1=x

?rm=x+12

圖4:PWM調制

Ⅵ 離散Δ調制器

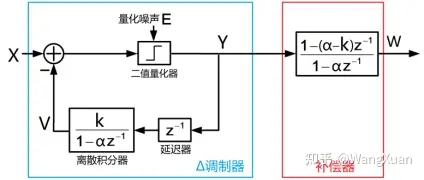

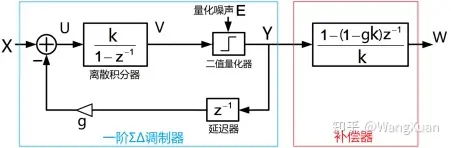

Δ調制器是另一種二值調制器,是ΣΔ調制器的前身。圖6是離散Δ調制器的系統框圖,其中Δ調制器只是左半部分,它輸出二值信號y[n]。右半部分是一個補償器,它輸出的w[n]不是二值信號。該補償器的參數需要根據積分器的參數來設計。在現實應用中積分器和補償器是不同的實現,比如模擬Δ調制器中的積分器是模擬積分器,而補償器是數字電路實現。

圖6:離散Δ調制器的系統框圖

圖7:Δ調制器在輸入正弦波時的現象

在后文中,約定小寫字母 (x[n], v[n], y[n]) 代表時域離散信號,大寫字母 (X, V, Y) 代表對應的 z 變換后的信號。

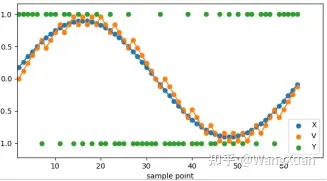

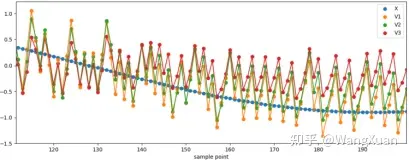

我們先進行直觀理解:設 x[n] 是正弦信號,得到各個信號的波形圖如圖7。可以看到 v[n] 在試圖跟隨 x[n],這是因為當 x[n]>v[n] 時,二值量化器會輸出 y[n]=+1,而因為 v[n+1]=αv[n]+ky[n] ,只要 α 不是太小,就能讓 v[n+1]>v[n] ,也就是讓 v[n]增大。同理當 x[n]

有了直觀理解后,進行理論分析,首先我們知道時域關系:

v[n+1]=αv[n]+ky[n]……(8)

考慮到 y[n]只取+1 和-1,所以 v[n]能達到的最高的變化率與 v[n] 的取值有關,為:

|Δv|max=min((α?1)v,(1?α)v)+k……(9)

而滿幅正弦波 x[n]=sin?(2πnf/fs) 的變化率隨著 x[n] 的取值而變化,關系為:

|Δx|max=2πffscos?(arcsin?x)……(10)

為了讓 v[n] 能跟隨 x[n],必須保證 |Δv|max>|Δx|max ,即:

min((α?1)x,(1?α)x)+k>2πffscos?(arcsin?x)……(11)

解(11)得Δ調制器必須滿足約束:

k2?(1?α)2>(2πffs)2

調制器能成功跟隨的條件……Δ調制器能成功跟隨的條件(12)

下面我們推導Δ調制器在 z 變換域的傳遞函數,注意我們把二值量化器進行了線性近似,E 是它的量化噪聲。 另外,以下公式中的大寫字母都是 z 變換域的復變函數,比如 Y 應寫做 Y(z),這里省略了(z)。

Y=X+E?kz?11?αz?1Y

?Y=1?αz?11?(α?k)z?1(X+E)

調制器的傳遞函數……Δ調制器的傳遞函數(14)

(14)的傳遞函數有一個極點 z=α?k ,要讓系統穩定,令極點在單位圓內:

調制器穩定的條件?1<α?k<1???……Δ調制器穩定的條件(15)

從前文的直觀敘述我們知道,二值信號 y[n] 包含 v[n] 的增加/減小信息,當 x[n] 是直流時,v[n] 在 x[n]上下跳躍,此時 y[n]在+1, -1 間交替,并不包含直流信息。這一點我們也可以從傳遞函數(14)來理解,在直流(z → 1)時,由于α一般接近于 1,導致 Y 非常小,說明直接使用 y[n] 作為輸出就會丟失 x[n] 的直流部分,因此對Δ調制器來說,加入圖6所示的補償器是必須的,該補償器的傳遞函數為 1?(α?k)z?11?αz?1 ,具有積分的效果,可以從 y[n] 中恢復出 x[n] 的直流信息。經補償后,(14)前面的因子被消掉:

調制器補償后的傳遞函數W=X+E……Δ調制器補償后的傳遞函數(16)

習慣上,把傳遞函數表示成:

W=HxX+HeE

其中 Hx 稱為信號傳遞函數; He 稱為噪聲傳遞函數。

我們發現,經補償后 Hx=He=1 ,這似乎意味著只要滿足約束條件(12)(15)就能隨意配置參數α和k,實則不然,因為二值量化器的非線性,實踐中會觀察到 α=1 時量化噪聲 e[n] 近似白噪聲,而 e[n] 越小,e[n]越分布于低頻。因此實踐中往往令 α=1 ,再在(12)(15)的約束下配置一個盡量小的 k 。在模擬Δ調制器設計中,由于一些現實問題,比如運放開環增益并不是無窮大,導致積分器緩慢泄漏,即 α 是一個略小于 1 的值(比如 0.99)都是完全能容忍的。不過 α 不能過小,否則會導致低頻噪聲很大。

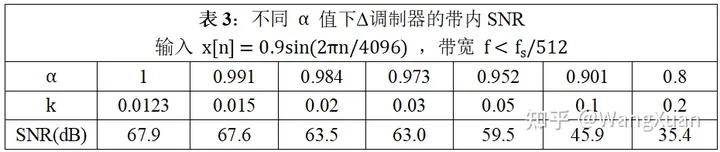

為了驗證以上結論,我們在(12)(15)的約束下設計出七種 α, k 的組合如表3。我們編寫代碼仿真,將正弦波 x[n]=0.9sin(2πn/4096) 輸入這些Δ調制器,計算出帶寬 f表3。可以看出在 α>0.97 時 SNR 都還不錯,但隨著 α 繼續減小,SNR會持續惡化。

加補償的Δ調制器的傳遞函數為 W=X+E 。考慮到當 α 接近 1 時,E 為白噪聲,過采樣技術帶來的 SNR 提升滿足公式(7),即每過采樣 4 倍,SNR 提升 6.02dB 。注意:Δ調制器與 1-bit ADC 的區別就在于 1-bit ADC 的量化噪聲 E 不是白噪聲,導致過采樣技術失效;而Δ調制器不會使過采樣技術失效。

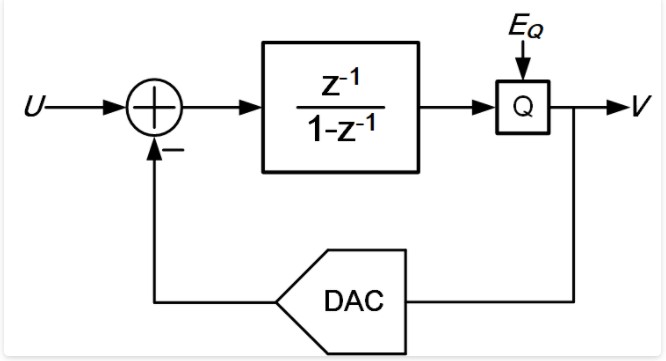

Ⅶ 離散一階ΣΔ調制器

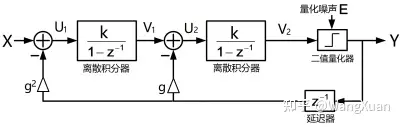

對Δ調制器稍作修改就能得到一階ΣΔ調制器如圖8,它后面也有一個補償器(但不是必須的)。為了方便分析,設積分器無泄漏(α = 1)。實際使用中與Δ調制器同樣, α 不能與 1 相差過大,否則影響性能。另外,相比于Δ調制器,反饋回路中多了一個增益 g ,因此ΣΔ調制器有兩個參數:k, g 。

圖8:離散一階ΣΔ調制器的系統框圖

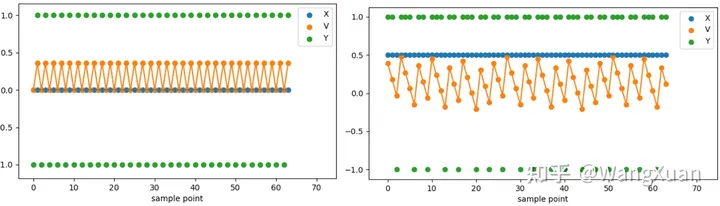

我們依然先進行直觀理解:設 k=0.3, g=1.2 ,分別考察輸入 x[n] 為以下情況時的現象:

直流輸入 x[n]=0 ,如圖9(左),當 y[n]=?1 時 u[n]=g ,由于積分器的存在導致 v[n] 上升, 導致二值量化器下次會輸出 y[n+1]=1 。反之,當 y[n]=1 時會讓 v[n] 下降,導致 y[n+1]=?1 。 總之, y[n] 會在+1 和-1 上反復跳躍。

直流輸入 x[n]=0.5 ,如圖9(右) ,當 y[n]=?1 時 u[n]=0.5+g ,引起的 v[n] 的上升量為 v[n+1]?v[n]=k(g+0.5) ;同理當 y[n]=1 時引起的 v[n] 的下降量為 ?v[n+1]+v[n]=k(g?0.5) 。 這說明每次 v[n] 上升的更多而下降的更少,最終的效果是 v[n] 在 0 附近跳躍,但需要更多的上升步數 和更小的下降步數,導致 y[n]=1 的情況更多,y[n]=?1 的情況更少。

直流輸入 x[n]=0.001 ,v[n] 每次的上升量為 k(g+0.001) ;下降量為 k(g?0.001) , 盡管上升量和下降量相差很小,但畢竟有微小區別,這使得在足夠長的時間內 y[n]=1 的情況略多, y[n]=?1 的情況略少。這說明理論上一階ΣΔ調制器有無限精確的直流分辨率!這是Δ調制器不具備的。 不過這依賴于足夠多的樣點以及后級數據處理手段。

正弦輸入 x[n]=0.9sin?(2πn/64) ,如圖10,可以看到當 x[n] 較大時 y[n]=1 的情況更多;當 x[n] 較小時 y[n]=?1 的情況更多。

圖9:一階ΣΔ調制器在輸入 x[n]=0 (左) 和 x[n]=0.5 (右) 時的現象

圖10:一階ΣΔ調制器在輸入正弦波時的現象

下面我們根據圖8推導ΣΔ調制器的傳遞函數,注意二值量化器被進行了線性近似,E 是它的量化噪聲:

Y=E+V

?Y=E+k1?z?1U

?Y=E+k1?z?1(X?gz?1Y)

?Y=kX+(1?z?1)E1?(1?gk)z?1

一階調制器的傳遞函數……一階ΣΔ調制器的傳遞函數(17)

(17)有一個極點 z=1?gk ,要讓系統穩定,令極點在單位圓內:

一階調制器穩定的必要條件0

我們也可以在ΣΔ調制器后加入補償器。這樣可以消掉(17)的分母:

W=1?(1?gk)z?1kY

?W=1?(1?gk)z?1k×kX+(1?z?1)E1?(1?gk)z?1

?W=X+(1?z?1)kE

一階調制器補償后的傳遞函數……一階ΣΔ調制器補償后的傳遞函數(18)

實踐中 gk 并不會設的太小,因此(17)中的分母 (1?(1?gk)z?1)?1 幾乎不影響低頻( z→1 )的相移和增益的平坦性,因此ΣΔ調制器的補償器不是必須的,通常我們省略掉補償器,而不像Δ調制器必須進行補償。

現在假設我們不加補償,也即直接使用圖8中的 Y 作為輸出。根據(17),我們可以得出ΣΔ調制器的信號增益和噪聲增益:

Hx=k1?(1?gk)z?1

He=(1?z?1)1?(1?gk)z?1

調制器的信號傳遞函數和噪聲傳遞函數……ΣΔ調制器的信號傳遞函數Hx和噪聲傳遞函數He(19)

考慮到我們只關注低頻,也即 z 在單位圓上接近 z=1 的位置,此時噪聲傳遞函數 He 趨近于一 階無窮小,這說明如果我們關心的信號 x[n] 分布于低頻,則 ΣΔ 調制器只會引入很小的噪聲,SNR很高。

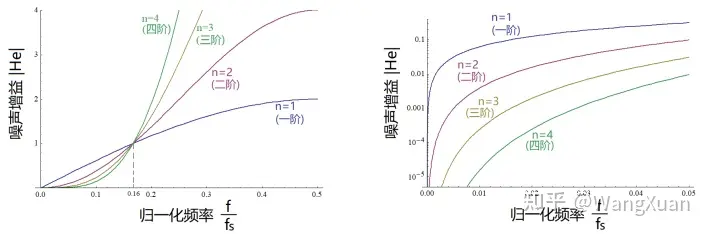

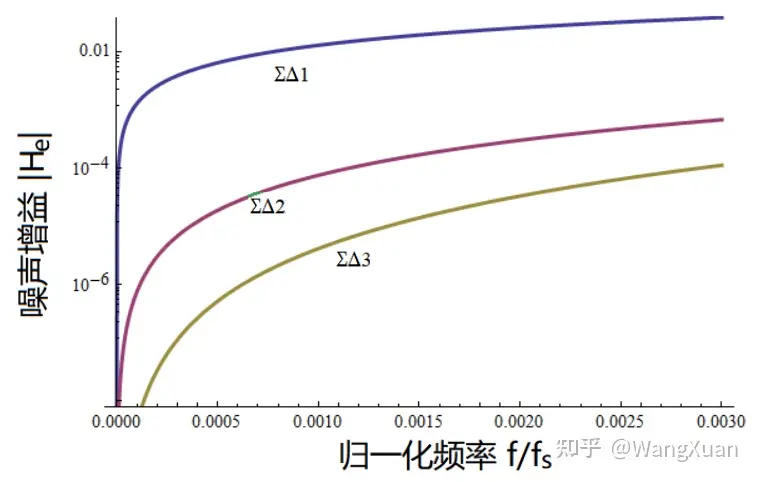

為了直觀說明這個特點,我們使用《信號與系統》中學過的頻率響應法來畫出ΣΔ調制器的噪聲頻譜 (噪聲幅頻特性曲線)。具體方法是:把 z=exp?(j2πf/fs) (z 取單位圓上的點)代入(19),繪制 |He| 的函數圖,得到如圖13中的藍線,可以看出 |He| 隨著 f 的減小而減小,這說明:如果圖8中的二值量化器量化噪聲 E 是白噪聲,則ΣΔ調制器輸出的噪聲偏藍。因此只要我們關注的頻率足夠低,帶內噪聲就會很小,得到的 SNR 也會非常高。

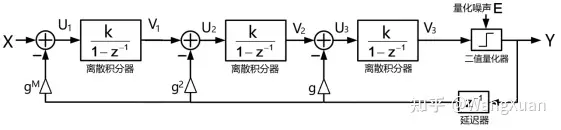

Ⅷ 離散高階ΣΔ調制器

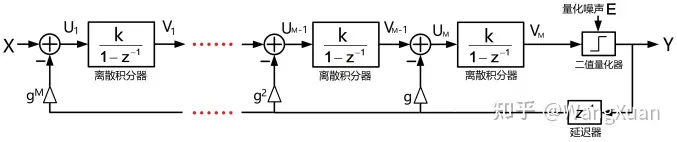

將一階ΣΔ調制器中的減法-積分器結構復制M份就能得到M階直連型ΣΔ調制器如圖12。推導其傳遞函數:

Y=E+k1?z?1(?gz?1+k1?z?1(?g2z?1+k1?z?1(...k1?z?1(?gMz?1Y+X))))

?Y=z?1?(1?gk)(gk)M+1z?1?(1?gk)(1?z?1)M+1(kMX+(1?z?1)ME)

階直連型調制器的傳遞函數……M階直連型ΣΔ調制器的傳遞函數(20)

圖12:離散M階ΣΔ調制器的系統框圖

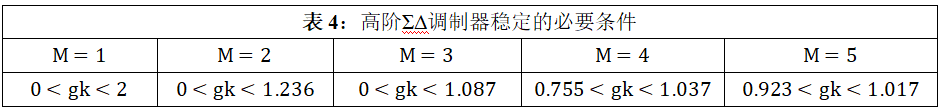

現在考察該傳遞函數(20)的穩定性,也就是看左邊的因子項的極點是否都在單位圓內。我們利用數值計算得到一階到五階的穩定條件如表4。注意這是線性系統的穩定條件!由于因為量化器的非線性,該系統還存在非線性失穩的可能,因此表4只是系統穩定的必要條件。

然后考察幅頻特性,若我們補償掉(20)中左邊的因子,得到信號傳遞函數 Hx=kM ,噪聲傳遞函數 He=(1?z?1)M 。顯然 He 在 z=1 處有n重零點,這意味著當頻率很小( f<圖13。可以看出在帶寬 f<0.16fs 內,階數越高,帶內噪聲一定越小。

圖13:理想ΣΔ調制器的理論噪聲增益:奈奎斯特帶寬內的線性坐標(左);低頻內的對數坐標(右)

這看似是個非常好的結論,意味著我們只要按圖12的結構堆疊階數,理論上就能在我們關心的低頻帶寬內得到無限低的噪聲。然而,在階數 M>3 時,量化器的非線性往往會產生非線性失穩:我們可以把量化器看作一個增益元件,當量化器的輸入 vM[n] 越大時,增益反而越小,因為系統構成環路,增益過小會導致環路失穩。除了非線性失穩問題,高階情況下各積分器的輸出 vi[n] 的范圍往往不易控制,若不精心設置系統,很可能導致 vi[n] 遠超出范圍 [-1,+1] ,在實際電路實現中,可能超出器件的線性工作區。

所幸我們有很多辦法來規避這些問題,讓高階ΣΔ調制器變得可行:

配置圖12中的增益參數 。比如增加 g 來讓環路有足夠的增益;減小 k 來控制 vi[n] 的范圍。實際上各個積分器的增益 k 可取不同值,反饋路徑的增益 g 也可取不同值,來達到更優的結果。本文只考慮它們都相同的情況。

在圖12的基礎上增加新的信號通路(比如前向通路)來達到同樣的目的。

拋棄圖12的積分器高階級聯結構,而是使用多個低階ΣΔ調制器級聯來等效出高階的效果。

方法2和3更復雜且效果好,被廣泛用在當今的ΣΔADC集成芯片中。下文我們僅僅簡單地用方法1來讓二階和三階ΣΔ調制器變得可行。

Ⅸ 離散二階、三階ΣΔ調制器

根據圖12,二階ΣΔ調制器的系統框圖如圖14;三階ΣΔ調制器的系統框圖如圖15。

圖14:離散二階ΣΔ調制器的系統框圖

圖15:離散三階ΣΔ調制器的系統框圖

根據公式(12)得出,二階ΣΔ調制器的傳遞函數:

Y=k2X+(1?z?1)2E1?(1?gk)(2+gk?z?1)z?1……(21)

以及三階ΣΔ調制器的傳遞函數:

Y=k3X+(1?z?1)31?(1?gk)(3+2gk+g2k2?(3+gk)z?1+z?2)z?1……(22)

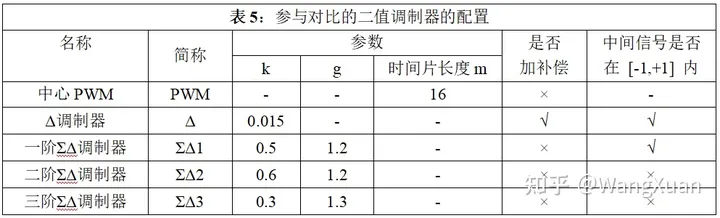

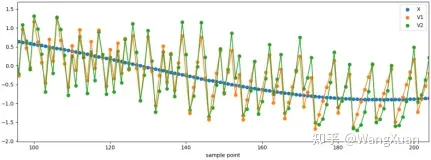

如表5,筆者用代碼仿真的方法確定了能夠穩定,且效果較好的二階ΣΔ調制器的參數 (M=2, k=0.6, g=1.2),以及較好的三階ΣΔ調制器的參數 (M=3, k=0.3, g=1.3)。為了幫助直觀理解,我們用該二階和三階ΣΔ調制器繪制了一段時域波形如圖16和圖17 。

圖16:二階ΣΔ調制器在輸入正弦波時的現象

圖17:三階ΣΔ調制器在輸入正弦波時的現象

然后我們考察這些配置下的噪聲傳遞函數。把我們選擇的一階ΣΔ調制器的參數 (M=1, k=0.45, g=1.2) 、二階ΣΔ調制器的參數(M=2, k=0.6, g=1.2) 、三階ΣΔ調制器的參數(M=3, k=0.3, g=1.3) 分別代入 (17)、 (21) 和 (22) 并繪制噪聲傳遞的幅頻曲線 |He| ,如圖18 ,可以看出,階數越高,噪聲增益越低。

圖18:本文的實驗使用的幾種ΣΔ調制器配置(見表5)的理論噪聲增益

Ⅹ 各種離散二值調制器的實現和評估

本節對幾種離散二值調制器進行評估。我們用 Python 3 實現了上文中的二值調制器(部分代碼見附錄),并找到幾種效果不錯的配置如表5。

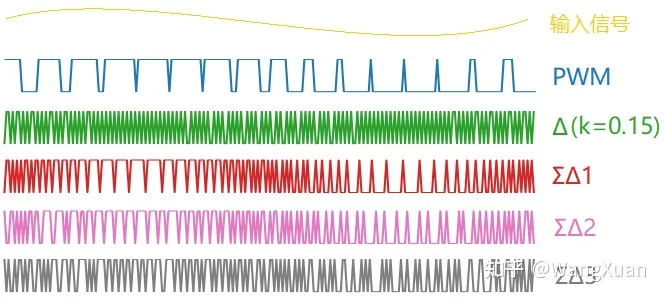

直觀起見,取輸入信號 x[n]=0.9sin(2πn/256) ,繪制各調制器的輸出如圖19,樣點的數量為256。可以看出:除了Δ調制器外,其余的調制器均體現出 x[n] 越大則輸出的均值越大的規律。而Δ調制器要經補償后才能看出這個規律。

圖19:輸入為 x[n]=0.9sin(2πn/256) 時各個調制器產生的輸出

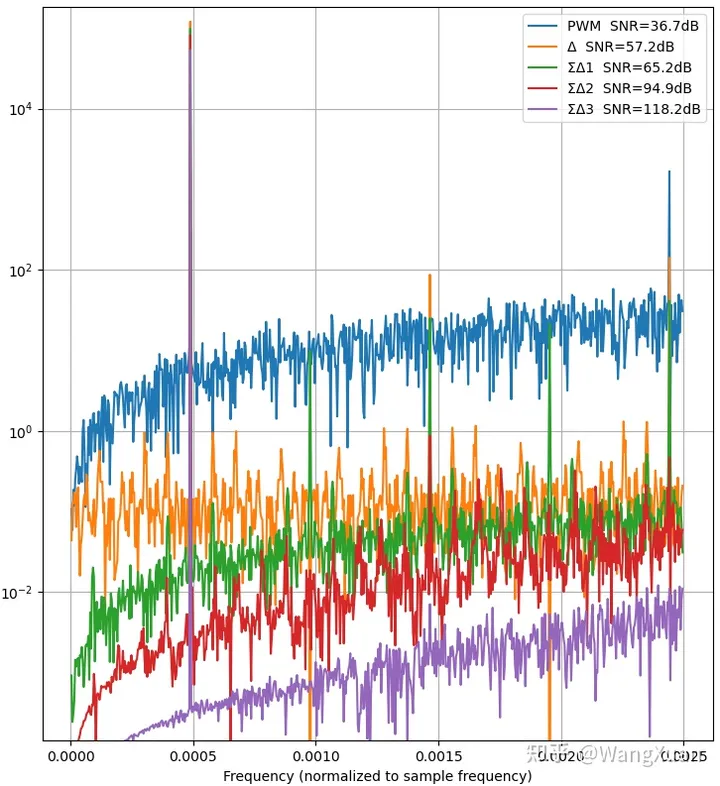

然后取輸入 x[n]=0.9sin?(2πn/2048) 繪制 218 個點的頻譜如圖20 。可以看出不同的調制器有不同的底噪,Δ調制器好于PWM調制器;ΣΔ調制器好于Δ調制器;高階ΣΔ調制器好于低階ΣΔ調制器。另外,Δ調制器的底噪呈現白色,而所有ΣΔ調制器的底噪都呈現出頻率越低,噪聲越小的現象,這符合之前的理論分析。

圖20:輸入為 x[n]=0.9sin(2πn/2048) 時各個調制器輸出的信號的頻譜(2^18個點)

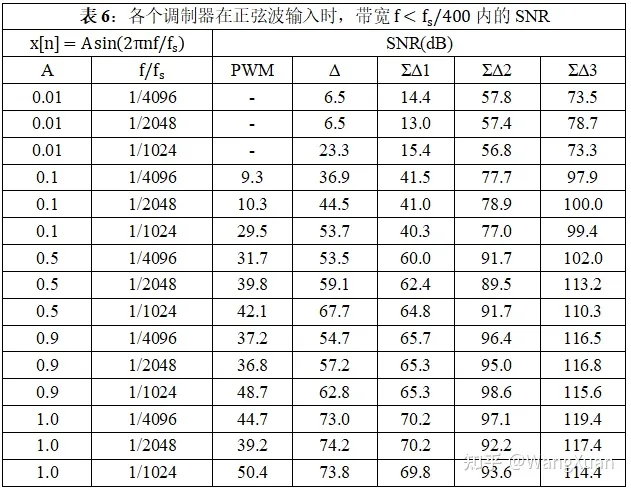

最后,取不同的正弦波幅度和頻率,用 220 個點的頻譜計算帶寬 f表6。注意:在計算頻譜和SNR時,為了防止頻譜泄漏,時間窗口都截取 x[n] 的完整周期,且窗口長度是周期長度的2的次冪倍。

Ⅺ 總結

本文帶讀者“入門”了ΣΔ技術,內容包括:

理想ADC的信噪比計算。

ADC過采樣技術;以及其在量化階數q較小時的局限性——量化噪聲不再是白噪聲,導致過采樣技術收效甚微。

離散二值調制器、模擬二值調制器的基本概念;以及如何用前者實現DAC,用后者實現ADC。

最直觀的二值調制器——PWM調制器。

ΣΔ調制器的前身——Δ調制器,分析出其量化噪聲呈白噪聲,從而讓過采樣技術生效。

一階離散ΣΔ調制器,分析出其量化噪聲偏藍,從而讓過采樣技術獲得奇效。

高階離散ΣΔ調制器:從z變換的角度解釋階數高的好處,也指出了高階面臨的穩定性問題。

比較了離散PWM調制器、Δ調制器、離散一二三階ΣΔ調制器的信噪比。

離散ΣΔ調制器可以實現ΣΔDAC。如果對ΣΔADC的基礎——模擬ΣΔ調制器感興趣,請閱讀(下)篇:

ΣΔ(Sigma-Delta)技術詳解(下):模擬ΣΔ調制器73 贊同 · 12 評論文章

附:一階、二階、三階ΣΔ調制器的Python實現

# -*- coding:utf-8 -*- # python3 # 離散ΣΔ調制器(一階、二階、三階) import numpy as np import matplotlib.pyplot as plt # 運行參數 -------------------------------------------------------------------------------- MARGIN = 16384 # 初始丟棄點數 TIME = 1048576 # 有效點數 PERIOD_X = 2048 # 正弦周期 AMP_X = 0.9 # 正弦幅度 BAND_RATIO = 0.5/240 # 過采樣比 MODULATORS = [ # 參與評估的調制器配置,格式: [ 名稱 , 階數 , k , g ] ------------ ['ΣΔ1' , 1 , 0.5 , 1.2 ] , ['ΣΔ2' , 2 , 0.6 , 1.2 ] , ['ΣΔ3' , 3 , 0.3 , 1.3 ] , ] def sigma_delta_mod(X, M, k, g): # ΣΔ 調制函數 --------------------------------------- Y = np.zeros(len(X)) # 輸出信號 V = np.zeros([M, len(X)]) # 中間信號 for t in range(len(X)): # 遍歷時間 V[0][t] = V[0][t-1] + k*(X[t] - Y[t-1]*g**M ) # 積分操作 for m in range(1, M): # 遍歷階數 V[m][t] = V[m][t-1] + k*(V[m-1][t] - Y[t-1]*g**(M-m)) # 積分操作 Y[t] = 1.0 if V[M-1][t] > 0 else -1.0 # 量化操作 return Y if __name__ == '__main__': # 主程序 -------------------------------------------- X = np.sin(np.arange(MARGIN+TIME)*2*np.pi/PERIOD_X) * AMP_X # 構造正弦波 for (label, M, k, g) in MODULATORS: Y = sigma_delta_mod(X, M, k, g) # 調制 Y = Y[MARGIN:] # 丟棄邊界 FFT_A = np.abs(np.fft.fft(Y))[1:int(TIME*BAND_RATIO)] + 10e-8 # 計算頻譜 FFT_F = np.arange(1,int(TIME*BAND_RATIO)) / TIME # 計算頻譜橫軸 peak = np.argmax(FFT_A) # 計算峰值 snr = 1.0/(sum(FFT_A**2)/sum(FFT_A[peak-4:peak+4]**2)-1.0) # 計算SNR plt.plot(FFT_F, FFT_A, label=label ) print('%s SNR=%.1fdB' % (label, 10*np.log10(snr) ) ) plt.xlabel('Frequency (normalized to sample frequency)') plt.yscale('log') plt.legend() plt.grid(True)

審核編輯 黃宇

-

dac

+關注

關注

43文章

2309瀏覽量

191562 -

調制器

+關注

關注

3文章

842瀏覽量

45325

發布評論請先 登錄

相關推薦

量化噪聲和DAC非線性在Sigma-Delta調制器環路中表現的不同

對于1位量化的Sigma-delta調制器來說,As和SNR和DR分別是什么關系?

Sigma-Delta調制器非理想特性建模

一種低功耗Sigma-Delta調制器的設計

AD7720:帶90 dB動態范圍的CMOS Sigma-Delta調制器數據表

AD9267:10 MHz帶寬、640 MSPS雙連續時間Sigma-Delta調制器初步數據表

剖析Sigma-Delta ADC原理

ΣΔ(Sigma-Delta)技術詳解(上):離散ΣΔ調制器

ΣΔ(Sigma-Delta)技術詳解(上):離散ΣΔ調制器

評論