半導(dǎo)體制造技術(shù)是現(xiàn)代電子科技領(lǐng)域中的一項(xiàng)核心技術(shù),對于計(jì)算機(jī)、通信、消費(fèi)電子等眾多產(chǎn)業(yè)的發(fā)展具有至關(guān)重要的影響。隨著科技的不斷進(jìn)步,半導(dǎo)體制造技術(shù)也在不斷發(fā)展,不斷突破著制造的極限。其中,半導(dǎo)體制造技術(shù)的節(jié)點(diǎn)是這一進(jìn)程中的關(guān)鍵環(huán)節(jié),下面將對半導(dǎo)體制造技術(shù)的節(jié)點(diǎn)進(jìn)行詳細(xì)闡述。

一、什么是半導(dǎo)體制造技術(shù)節(jié)點(diǎn)

半導(dǎo)體制造技術(shù)節(jié)點(diǎn),簡稱節(jié)點(diǎn),是指在半導(dǎo)體制造過程中,用來衡量集成電路中晶體管門極寬度的標(biāo)準(zhǔn)。節(jié)點(diǎn)的大小直接影響到芯片的集成度、性能、功耗以及制造成本。隨著技術(shù)的發(fā)展,節(jié)點(diǎn)的尺寸不斷縮小,使得單個(gè)芯片上可以集成的晶體管數(shù)量呈指數(shù)級(jí)增長,從而推動(dòng)了半導(dǎo)體產(chǎn)業(yè)的飛速發(fā)展。

二、半導(dǎo)體制造技術(shù)節(jié)點(diǎn)的發(fā)展歷程

半導(dǎo)體制造技術(shù)節(jié)點(diǎn)的發(fā)展經(jīng)歷了從微米級(jí)到納米級(jí)的跨越。早期的半導(dǎo)體制造技術(shù)節(jié)點(diǎn)以微米(μm)為單位,如1.0μm、0.8μm等。隨著技術(shù)的不斷進(jìn)步,節(jié)點(diǎn)尺寸逐漸縮小,進(jìn)入了納米(nm)時(shí)代。目前,業(yè)界領(lǐng)先的半導(dǎo)體制造企業(yè)已經(jīng)推出了7nm、5nm甚至更先進(jìn)的節(jié)點(diǎn)技術(shù)。

每個(gè)節(jié)點(diǎn)的突破都意味著半導(dǎo)體制造技術(shù)的一個(gè)巨大飛躍。節(jié)點(diǎn)的縮小不僅提高了芯片的集成度,還帶來了更高的性能、更低的功耗和更小的體積。這使得半導(dǎo)體產(chǎn)品能夠更好地滿足日益增長的市場需求,推動(dòng)電子產(chǎn)業(yè)的持續(xù)創(chuàng)新。

三、半導(dǎo)體制造技術(shù)節(jié)點(diǎn)的挑戰(zhàn)與解決方案

隨著節(jié)點(diǎn)的不斷縮小,半導(dǎo)體制造技術(shù)面臨著越來越多的挑戰(zhàn)。首先,物理極限的制約使得節(jié)點(diǎn)的進(jìn)一步縮小變得越來越困難。當(dāng)節(jié)點(diǎn)尺寸接近原子級(jí)別時(shí),量子效應(yīng)等物理現(xiàn)象將對芯片性能產(chǎn)生顯著影響,這要求制造工藝具備更高的精度和穩(wěn)定性。

其次,制造成本的上升也是制約節(jié)點(diǎn)發(fā)展的重要因素。隨著節(jié)點(diǎn)的縮小,制造過程中所需的設(shè)備、材料和工藝都變得更加復(fù)雜和昂貴。這使得半導(dǎo)體制造企業(yè)面臨著巨大的成本壓力,需要不斷探索新的制造成本控制方法。

針對這些挑戰(zhàn),業(yè)界采取了多種解決方案。一方面,通過引入新的材料和結(jié)構(gòu)來改善芯片的性能。例如,采用高遷移率材料作為溝道材料、采用三維堆疊結(jié)構(gòu)提高集成密度等。這些創(chuàng)新為節(jié)點(diǎn)的進(jìn)一步發(fā)展提供了可能。

另一方面,通過改進(jìn)制造工藝和設(shè)備來提高制造精度和降低成本。例如,采用極紫外光(EUV)光刻技術(shù)替代傳統(tǒng)的光學(xué)光刻技術(shù),可以提高光刻分辨率和減少制造成本;采用先進(jìn)的刻蝕和薄膜沉積技術(shù)可以實(shí)現(xiàn)更精細(xì)的結(jié)構(gòu)和更高的良率等。

四、半導(dǎo)體制造技術(shù)節(jié)點(diǎn)的未來展望

展望未來,半導(dǎo)體制造技術(shù)節(jié)點(diǎn)的發(fā)展將呈現(xiàn)以下趨勢:

節(jié)點(diǎn)尺寸將進(jìn)一步縮小。隨著技術(shù)的不斷進(jìn)步和市場需求的增長,節(jié)點(diǎn)的縮小仍將是半導(dǎo)體制造技術(shù)發(fā)展的主要方向。業(yè)界將繼續(xù)探索新的材料和結(jié)構(gòu),以突破物理極限的制約,實(shí)現(xiàn)更小、更快、更省電的芯片產(chǎn)品。

制造工藝將更加智能化和自動(dòng)化。隨著人工智能和大數(shù)據(jù)等技術(shù)的應(yīng)用,半導(dǎo)體制造工藝將實(shí)現(xiàn)更高程度的智能化和自動(dòng)化。這不僅可以提高制造效率和質(zhì)量,還可以降低制造成本和人力資源需求。

制造技術(shù)將更加注重環(huán)保和可持續(xù)發(fā)展。隨著環(huán)保意識(shí)的提高和法規(guī)的嚴(yán)格限制,半導(dǎo)體制造技術(shù)將越來越注重環(huán)保和可持續(xù)發(fā)展。業(yè)界將積極探索綠色制造技術(shù)和循環(huán)經(jīng)濟(jì)模式,降低制造過程中的環(huán)境污染和資源消耗。

五、結(jié)論

總之,半導(dǎo)體制造技術(shù)節(jié)點(diǎn)是衡量半導(dǎo)體制造水平的重要指標(biāo)之一。隨著節(jié)點(diǎn)的不斷縮小和技術(shù)的不斷創(chuàng)新,半導(dǎo)體產(chǎn)品將呈現(xiàn)出更高的性能、更低的功耗和更小的體積等優(yōu)勢。然而,節(jié)點(diǎn)的發(fā)展也面臨著物理極限、制造成本等挑戰(zhàn)。為了應(yīng)對這些挑戰(zhàn)并推動(dòng)半導(dǎo)體產(chǎn)業(yè)的持續(xù)發(fā)展,業(yè)界需要不斷探索新的材料、結(jié)構(gòu)和制造工藝,并注重環(huán)保和可持續(xù)發(fā)展。同時(shí),政府、企業(yè)和社會(huì)各界也應(yīng)加強(qiáng)合作和支持,共同推動(dòng)半導(dǎo)體制造技術(shù)的創(chuàng)新和進(jìn)步。

-

芯片

+關(guān)注

關(guān)注

456文章

51170瀏覽量

427227 -

材料

+關(guān)注

關(guān)注

3文章

1255瀏覽量

27409 -

半導(dǎo)體制造

+關(guān)注

關(guān)注

8文章

421瀏覽量

24140

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

半導(dǎo)體制造里的ALD工藝:比“精”更“精”!

鎵在半導(dǎo)體制造中的作用

【「大話芯片制造」閱讀體驗(yàn)】+ 半導(dǎo)體工廠建設(shè)要求

PCB雙面板 —— 小型電子產(chǎn)品的 “幕后英雄”

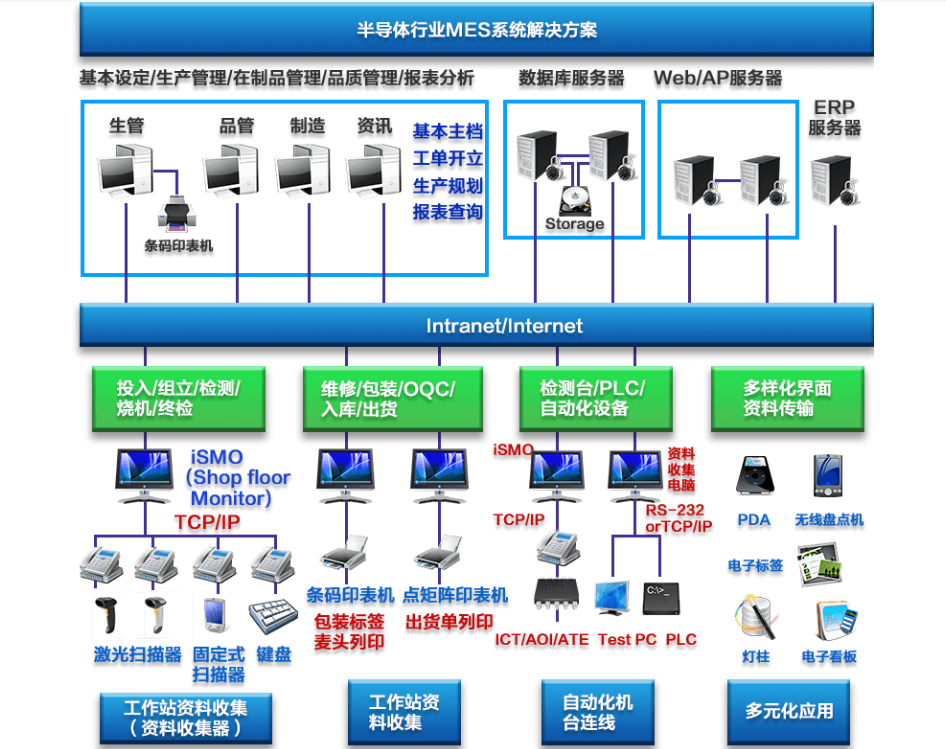

半導(dǎo)體制造行業(yè)MES系統(tǒng)解決方案

ESD靜電對半導(dǎo)體制造的影響

江西薩瑞微榮獲&quot;2024全國第三代半導(dǎo)體制造最佳新銳企業(yè)&quot;稱號(hào)

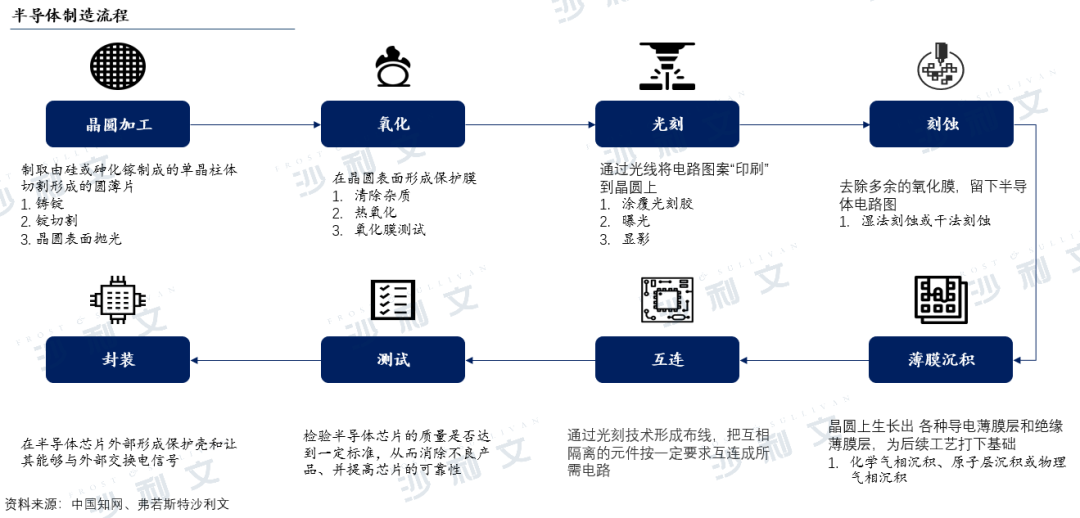

半導(dǎo)體制造過程解析

半導(dǎo)體制造設(shè)備革新:機(jī)床需求全面剖析

半導(dǎo)體制造設(shè)備對機(jī)床的苛刻要求與未來展望

西安電子科技大學(xué)馬曉華團(tuán)隊(duì):蹚出寬禁帶半導(dǎo)體技術(shù)創(chuàng)新之路

中國半導(dǎo)體產(chǎn)業(yè)的十大技術(shù)“瓶頸”解析

十大半導(dǎo)體技術(shù)將徹底改變電子制造

半導(dǎo)體制造技術(shù)節(jié)點(diǎn):電子科技飛速發(fā)展的幕后英雄

半導(dǎo)體制造技術(shù)節(jié)點(diǎn):電子科技飛速發(fā)展的幕后英雄

評(píng)論