DDIO用法

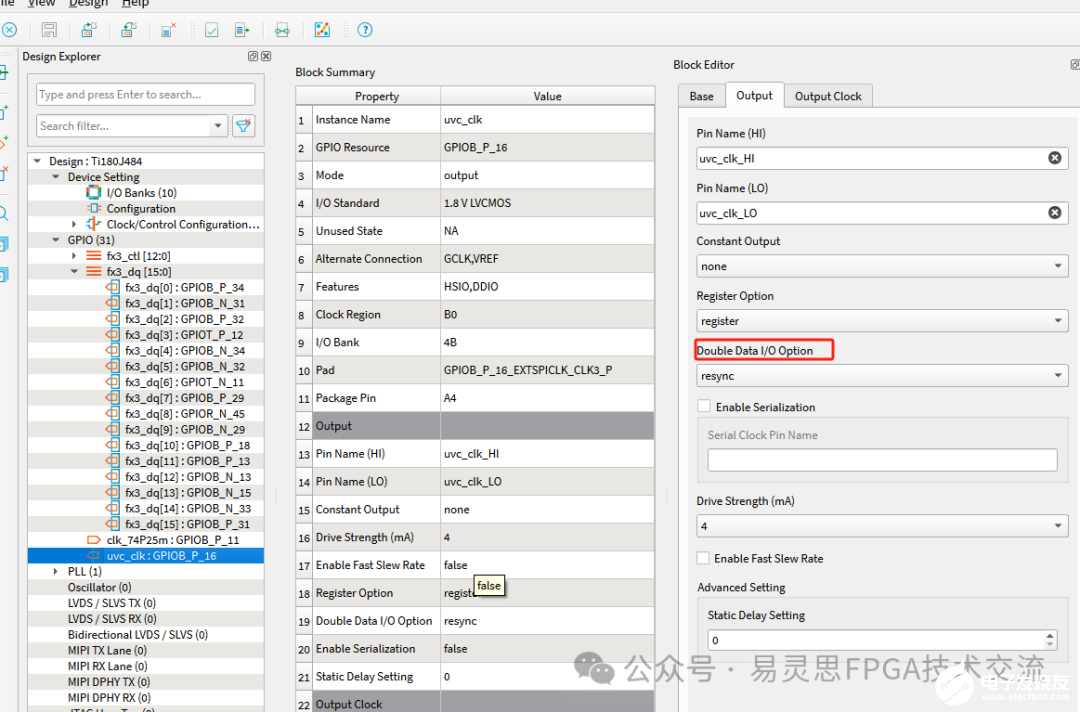

對于輸入輸出IO很多時(shí)候會用到DDIO的用法。對于DDIO,就是時(shí)鐘的雙沿采集或者發(fā)送數(shù)據(jù),所以必須要用到寄存器。它的設(shè)置也比較簡單,在intefaceDesigner中添加GPIO,并把register Option設(shè)置為register,另外要設(shè)置Double Data IO Option模式,分別為normal和resync。

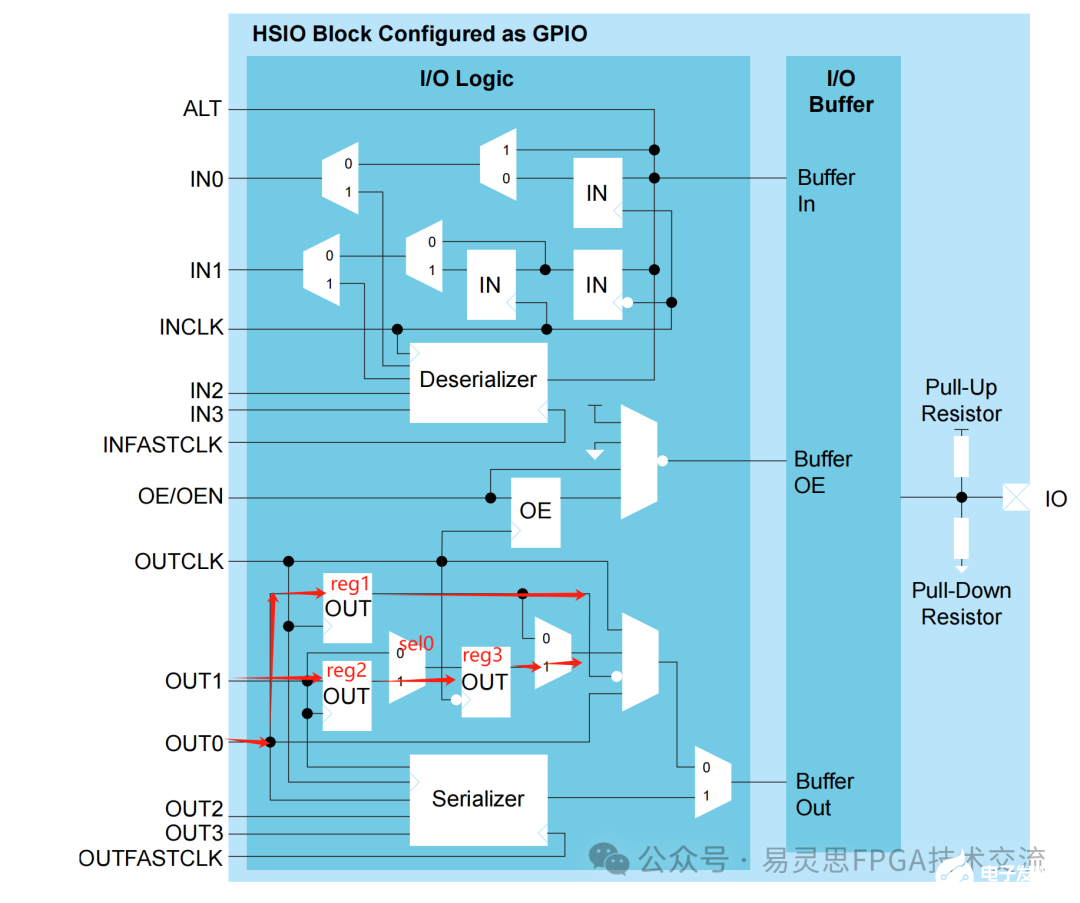

下圖是易靈思的GPIO的結(jié)構(gòu)。

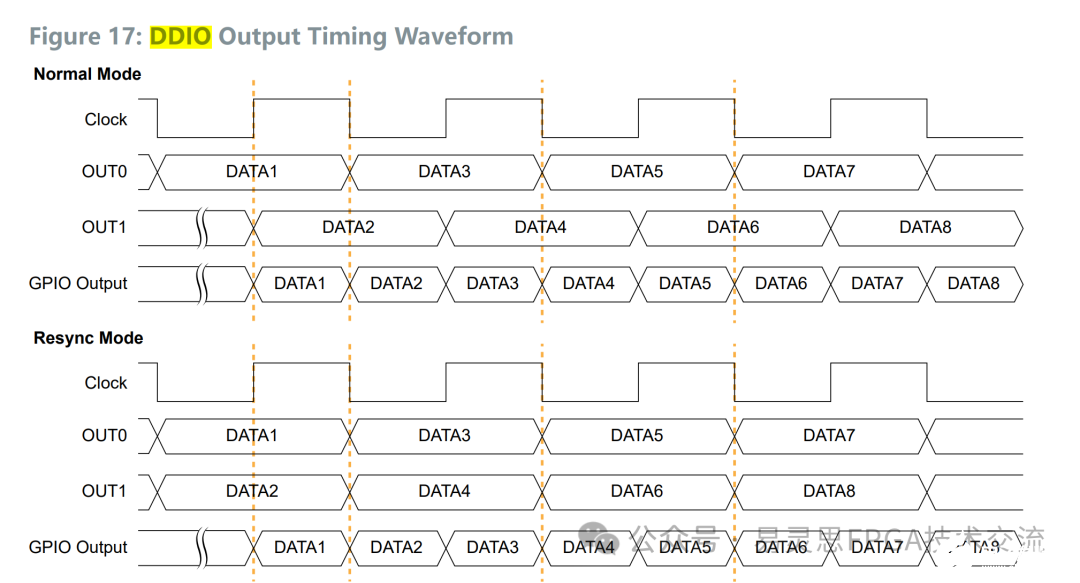

對應(yīng)上圖我們以O(shè)DDIO為例,分別標(biāo)出了reg1,reg2和reg3三個(gè)寄存 器。當(dāng)OUT0為上升沿的觸發(fā)信號,即HI,OUT1為下降沿的觸發(fā)信號,即LO。當(dāng)DDIO模式設(shè)置為Normal mode時(shí),OUT1經(jīng)過reg3輸出;當(dāng)設(shè)置為Resync mode時(shí)OUT1經(jīng)過了reg2和reg3,reg2用于對數(shù)據(jù)打一拍來對齊數(shù)據(jù),下面是數(shù)據(jù)的輸出波形。

我們只需要在top模塊中添加相應(yīng)信號即可以用于控制:

module DDIO_Test(...otuputoddio_HI,output oddio_LO,...);

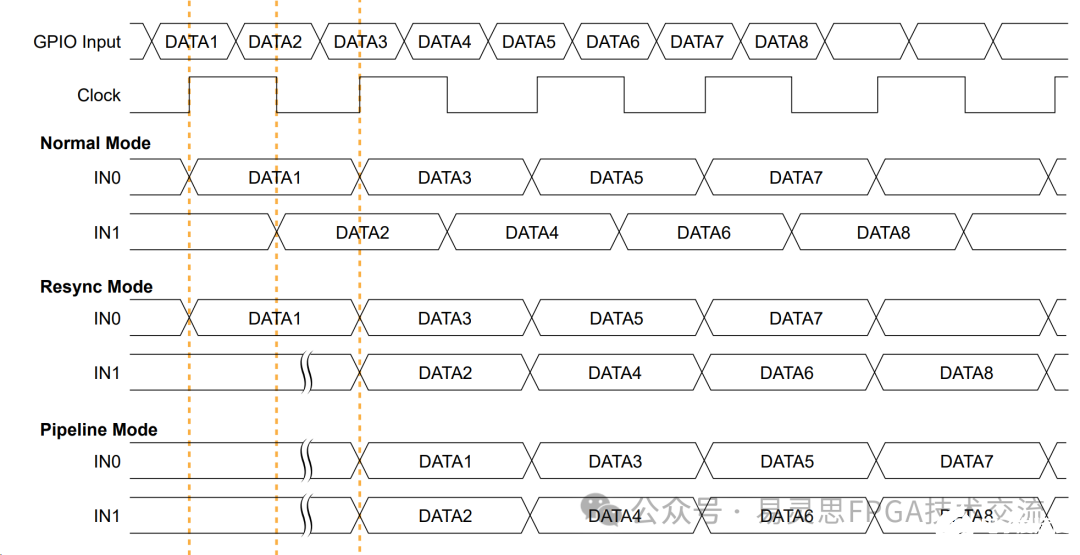

下圖為數(shù)據(jù)輸入時(shí)的波形,分別對應(yīng) Normal和Resync mode。

-

IO

+關(guān)注

關(guān)注

0文章

461瀏覽量

39372 -

GPIO

+關(guān)注

關(guān)注

16文章

1216瀏覽量

52379

發(fā)布評論請先 登錄

相關(guān)推薦

忽略基極電流,V1未知,如何知道Q1的發(fā)射極電阻?

常用時(shí)序約束使用說明-v1

Efinity FIFO IP仿真問題 -v1

DS-AN4V724-A CN V1 集成式霍爾電流傳感器-芯森電子

請問TLC352比較器的用法是否正確?

InterfaceDesinger 使用案例-v3

VisionFive v1下移植xv6,運(yùn)行到main.c時(shí)會出現(xiàn)莫名其妙錯誤為什么?

Efinity debugeri常見問題總結(jié)-v1

SC171開發(fā)套件V1 技術(shù)資料

CMSIS-RTOS V1與V2的區(qū)別是什么?

HK32M066B數(shù)據(jù)手冊V1

EG2183D高壓600V2A半橋驅(qū)動芯片數(shù)據(jù)手冊V1

AWTK 開源串口屏開發(fā)(10) - 告警信息的高級用法

大模型系列:Flash Attention V2整體運(yùn)作流程

InterfaceDesinger 使用案例-v1 -DDIO用法

InterfaceDesinger 使用案例-v1 -DDIO用法

評論