▼關(guān)注微信公眾號:硬件那點(diǎn)事兒▼

摩爾定律指出,在集成電路上可容納的晶體管數(shù)量大約每隔18-24個月就會翻一番,臺積電已經(jīng)開始試產(chǎn)2nm制程工藝了,這導(dǎo)致IC氧化物厚度和導(dǎo)線寬度變得更薄,對于ESD就更敏感了,所以IC廠商會將靜電放電(ESD)保護(hù)集成到芯片中,但是由于IC尺寸縮小和特征尺寸減小,內(nèi)置ESD保護(hù)裝置(如二極管、閂鎖晶體管和多晶硅電阻)可能無法處理較高的ESD能量,可能導(dǎo)致保護(hù)失效。這意味著內(nèi)部ESD保護(hù)的能力有限,可能不足以應(yīng)對某些高能量的ESD事件,仍需要額外的外部保護(hù)措施。

當(dāng)IC遭受外部ESD事件時,外部的ESD電容會吸收一部分能量,剩余的能量會由IC內(nèi)部的ESD防護(hù)模塊吸收,那么遇到這種情況我們該如何計算電容容值呢?下面我們就以集成了小信號TVS的IC為例,講解一下外部ESD電容容值的計算方法。

計算的思路是外部的ESD電容吸收之后剩余的ESD能量不會超過IC內(nèi)部的ESD防護(hù)模塊允許吸收的最大能量。W0=(Vesd0-Vcl)*Vcl*Cesd0

其中Vesd0表示規(guī)格書中IC允許承受的最大ESD電壓(比如下圖的5000V),可以在規(guī)格書中找到這個參數(shù),Vcl表示IC內(nèi)部ESD防護(hù)模塊的鉗位電壓(比如下圖的64V),Cesd0表示IC ESD測試的放電電容(比如下圖的100pF)。

2.添加外部ESD電容后,IC實(shí)際吸收的ESD能量W1如何計算?W1=(Vesd1-Vcl*(1+Cext/Cesd1))*Vcl*Cesd1

其中Vesd1表示產(chǎn)品實(shí)際測試的最大ESD電壓,比如8KV,Vcl表示IC內(nèi)部ESD防護(hù)模塊的鉗位電壓,Cext表示外部添加的ESD電容,Cesd1表示產(chǎn)品實(shí)際測試的ESD 放電電容(比如330pF)。

3.添加的外部ESD電容容值如何計算?

基于IC實(shí)際吸收的ESD能量W1要小于IC允許的最大ESD脈沖能量W0可以計算出外部電容的最小容值:

Cext_min=((Vesd1-Vcl)*Cesd1/Vcl)-W0/Vcl*Vcl

以接觸放電8KV,源電容330pF,放電電阻2kΩ,可以計算出Cext_min>33nF。

有問題歡迎在評論區(qū)留言交流哦!

有問題歡迎在評論區(qū)留言交流哦!

原文標(biāo)題:一種新的MLCC陶瓷電容用于電路靜電ESD保護(hù)的電容容值計算方法

文章出處:【微信公眾號:硬件那點(diǎn)事兒】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

相關(guān)推薦

)和皮法(pF)。 電容容值的表示 電容的容值通常直接標(biāo)注在電容器的外殼上,可能使用數(shù)字加字母的方式來表示。其中,數(shù)字部分表示

![的頭像]() 發(fā)表于

發(fā)表于 11-14 14:26

?2268次閱讀

貼片電容陶瓷電容MLCC(Multi-layer Ceramic Capacitors,多層陶瓷電容

![的頭像]() 發(fā)表于

發(fā)表于 09-30 09:33

?398次閱讀

陶瓷貼片電容的耐壓值是衡量其性能的重要指標(biāo)之一,它表示電容器可承受的最大電壓,超過該值可能會導(dǎo)致

![的頭像]() 發(fā)表于

發(fā)表于 09-25 15:09

?559次閱讀

限制電壓和電流來保護(hù)電子設(shè)備。以下是關(guān)于POWERclamp原理的介紹: ESD保護(hù)電路的基本概念 ESD

![的頭像]() 發(fā)表于

發(fā)表于 09-14 14:41

?2138次閱讀

原理 電橋測試的基本原理 電橋測試是一種基于電橋原理的測量方法。電橋由四個電阻或電容元件組成,形成一個閉合的電路。當(dāng)電橋平衡時,電橋兩端的電

![的頭像]() 發(fā)表于

發(fā)表于 07-26 10:09

?3323次閱讀

。 基本概念 2.1 電容 電容是一種能夠存儲電荷的元件,其單位是法拉(F)。電容的大小與兩個導(dǎo)體之間的距離、面積和介質(zhì)的介電常數(shù)有關(guān)。電容

![的頭像]() 發(fā)表于

發(fā)表于 07-17 14:41

?5992次閱讀

無功補(bǔ)償是電力系統(tǒng)中一種重要的技術(shù)手段,用于提高電網(wǎng)的功率因數(shù),降低線損,提高輸電效率,改善電能質(zhì)量。無功補(bǔ)償?shù)闹饕绞绞峭ㄟ^并聯(lián)電容器進(jìn)行補(bǔ)償。本文將介紹無功補(bǔ)償?shù)?b class='flag-5'>計算方法,包括補(bǔ)償

![的頭像]() 發(fā)表于

發(fā)表于 07-12 14:44

?1903次閱讀

電子發(fā)燒友網(wǎng)站提供《TPD4E101 4通道雙向低電容值靜電放電保護(hù)(ESD)器件數(shù)據(jù)表.pdf》資料免費(fèi)下載

發(fā)表于 07-10 09:45

?0次下載

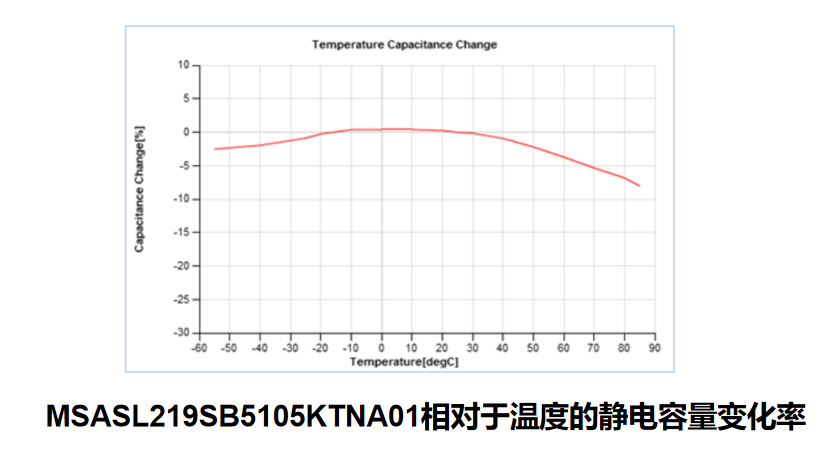

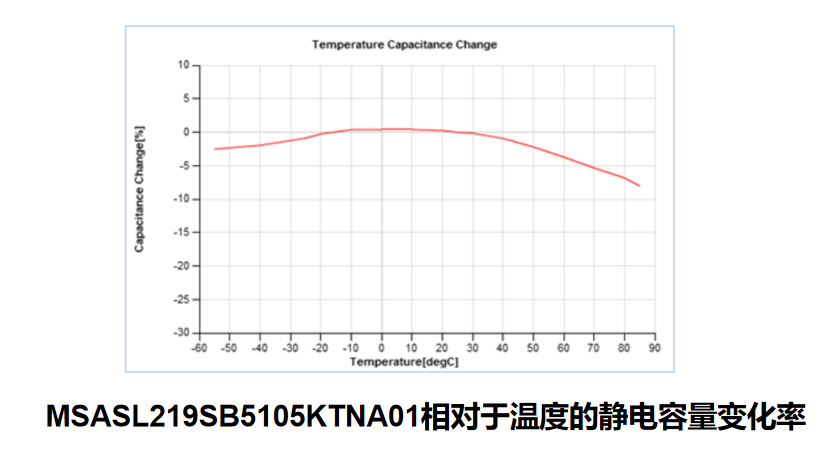

陶瓷電容器的靜電容量會因溫度而變化嗎? 電容器的靜電容量的溫度特性是什么? ? 陶瓷

![的頭像]() 發(fā)表于

發(fā)表于 06-24 06:17

?321次閱讀

達(dá)不到所標(biāo)稱的數(shù)值。 2、電容器老化問題 :電容器老化后,內(nèi)部絕緣材料可能會損壞,導(dǎo)致容量不足。老化現(xiàn)象在所有以鐵電系材料做介電質(zhì)的材料產(chǎn)品中均有發(fā)生,是一種自然的不可避免的現(xiàn)象。 3、構(gòu)造設(shè)計問題 :

![的頭像]() 發(fā)表于

發(fā)表于 06-14 14:52

?866次閱讀

高壓陶瓷電容,是一種能夠承受較高電壓的電容器。耐壓高是它的一個主要特點(diǎn)。高壓陶瓷

![的頭像]() 發(fā)表于

發(fā)表于 06-12 14:57

?1148次閱讀

國巨陶瓷貼片電容有哪些優(yōu)勢,YAGEO貼片電容(MLCC)是一種電容材質(zhì)。貼片

![的頭像]() 發(fā)表于

發(fā)表于 03-12 14:05

?1105次閱讀

陶瓷電容是高性能電子元件,具有大溫度系數(shù)、大比容量和良好耐潮濕性。多層陶瓷電容MLCC體積小,得益于其獨(dú)特的結(jié)構(gòu)和制造工藝,包括

![的頭像]() 發(fā)表于

發(fā)表于 03-04 09:21

?886次閱讀

管吧。ESD二極管,也被稱為靜電保護(hù)二極管,是一種用于保護(hù)電子元器件免受靜電放電(

![的頭像]() 發(fā)表于

發(fā)表于 02-22 08:02

?983次閱讀

Bypass電容的大小和計算方法 Bypass電容是一種常見的電子元件,用于繞過或降低電路中的噪

![的頭像]() 發(fā)表于

發(fā)表于 02-14 17:56

?4271次閱讀

有問題歡迎在評論區(qū)留言交流哦!

有問題歡迎在評論區(qū)留言交流哦!

一種新的MLCC陶瓷電容用于電路靜電ESD保護(hù)的電容容值計算方法

一種新的MLCC陶瓷電容用于電路靜電ESD保護(hù)的電容容值計算方法

評論