一、RS鎖存器的定義

RS鎖存器,全稱Reset-Set Latch,是一種具有兩個穩定狀態(雙穩態)的電路,能夠存儲一位二進制數據。這兩個穩定狀態分別對應著二進制數0和1,用于表示電路的兩種不同邏輯狀態。RS鎖存器通過接收外部輸入信號(Reset和Set)來控制其狀態的轉換,并在輸入信號消失后,保持已轉換的穩定狀態(在通電狀態下)。

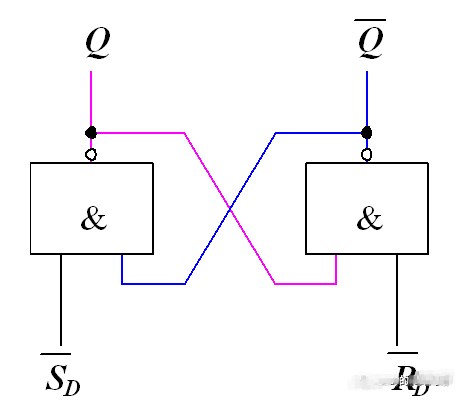

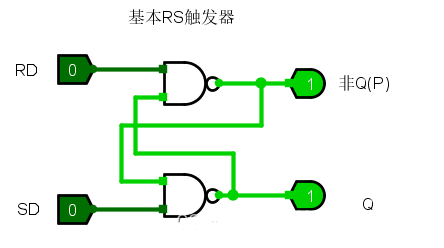

1、基本RS鎖存器

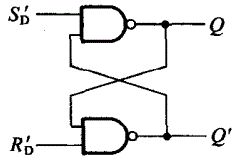

最簡單的觸發器是基本RS觸發器,基本RS鎖存器可以由兩個與非門構成,電路如下:

基本RS鎖存器由電平觸發,并且有一個重要的約束條件:/SD和/RD不能同時為零。即:/SD+/RD=1。

2、門控SR鎖存器

門控SR 鎖存器(或時鐘控制 SR 鎖存器)只能在存在使能信號以及所需輸入時更改其輸出狀態。因此,它也稱為 同步 SR 鎖存器 。相反,可以在應用其所需輸入條件時立即改變其狀態的鎖存器稱為異步鎖存器。

這意味著輸入僅在鎖存器啟用時才影響鎖存器;否則,即使應用輸入,輸出狀態也保持不變。換句話說,當 ENABLE 信號為高電平時,鎖存器處于活動狀態;當 ENABLE 信號為低電平時,鎖存器處于非活動狀態。該啟用信號用作時鐘脈沖。

因此,門控SR鎖存器也稱為時鐘SR觸發器或同步SR鎖存器。由于它僅在時鐘脈沖為高電平時響應輸入,因此也稱為電平觸發觸發器。門控 SR 鎖存器或時鐘控制 SR 觸發器的邏輯電路如下所示。

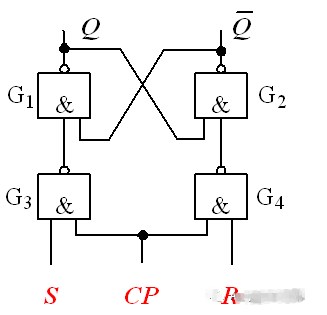

3、同步RS鎖存器

許多時候,我們希望觸發器只有在時鐘來臨時,輸出狀態改變,其它時候,觸發器維持,因為這樣做可以讓多個電路單元的狀態同時得以改變,這個時鐘,我們稱為同步時鐘。

如下圖所示,將基本RS鎖存器的輸入端分別經過一個與非門作為鐘控信號。就變成了同步RS鎖存器。

同步RS鎖存器與基本RS鎖存器的不同之處在于,只有時鐘CP=1的時候,輸出狀態才能被改變。但是,同步鎖存器也具有一個約束條件,就是當CP=1時,S和R不能同時為1。

此外,同步RS鎖存器還有一個不足之處在于:當CP=1時,S和R若多次改變,每次改變都會影響輸出。這種現象,稱為空翻現象。

二、RS鎖存器的作用

RS鎖存器在數字系統中具有多種重要作用,主要包括以下幾個方面:

數據存儲:RS鎖存器最基本的作用就是存儲一位二進制數據。在數字電路中,經常需要臨時存儲某些數據以便后續處理,RS鎖存器正是實現這一功能的關鍵元件。

狀態保持:RS鎖存器能夠在輸入信號消失后,保持已轉換的穩定狀態,這一特性使得它在需要保持電路狀態不變的場合中尤為重要。

信號同步:在復雜的數字系統中,各個部分可能需要同步工作。RS鎖存器可以作為同步信號的一部分,通過控制其狀態的轉換來實現不同部分之間的同步。

邏輯控制:RS鎖存器還可以作為邏輯控制元件,通過與其他電路元件的組合,實現復雜的邏輯控制功能。

三、RS鎖存器的功能

RS鎖存器的功能主要體現在以下幾個方面:

置位與復位功能:

置位(Set):當Set(S)輸入為高電平時,無論Reset(R)輸入為何種電平,RS鎖存器都將輸出Q置為1(同時Q'輸出為0),表示電路處于“置位”狀態。

復位(Reset):當Reset(R)輸入為高電平時,無論Set(S)輸入為何種電平,RS鎖存器都將輸出Q置為0(同時Q'輸出為1),表示電路處于“復位”狀態。

保持功能:當Set(S)和Reset(R)輸入均為低電平時,RS鎖存器將保持當前的狀態不變。這一特性使得RS鎖存器能夠在沒有外部輸入信號的情況下,長期保持其存儲的數據。

競爭與冒險避免:在數字電路中,由于信號傳輸的延遲和干擾等因素,可能會出現競爭與冒險現象。RS鎖存器通過其雙穩態特性,能夠在一定程度上避免競爭與冒險的發生,提高電路的穩定性和可靠性。

四、SR鎖存器的工作原理

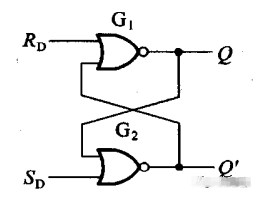

圖為與非門構成的SR鎖存器

圖為或非門構成SR鎖存器

上面兩圖分別是使用兩個與非門和兩個或非門組成的SR鎖存器,本文以圖兩個或非門組成的SR鎖存器進行功能分析。

當SD=1,RD=0時,或非門G2一端以SD作為輸入,故G2輸出低電平,G2和RD作為G1的輸入,所以G1輸出為高電平,此時SR鎖存器輸出Q端為高電平,Q'為低電平。Q的次態與Q的現態無關,輸出端Q均為高電平,故SD被稱為置數端。

當SD=0,RD=1時,因為或非門G1的RD端輸入高電平,所以G1輸出端輸出低電平,或非門G2輸入均為低電平,則Q非為高電平,故SR鎖存器Q輸出為低電平,Q'輸出高電平。Q的次態與Q現態無關,輸出端均為低電平,RD被稱為SR鎖存器清零端。

當SD=0,RD=0,Q的現態為0時,則Q'的次態為高電平,進而推出或非門G1的輸出為低電平,所以Q的次態為0;當Q的現態為1時,則或非門G2的輸出為0,或非門G1將RD和或非門G2輸出作為輸入,所以或非門G1輸出高電平,即Q的次態為高電平,由此可知,Q端的次態和現態保持相同,所以當SD與RD端輸入數據均無效時,SR鎖存器具有保持功能。

五、RS鎖存器的實現方式

RS鎖存器可以通過多種邏輯門電路實現,其中最常見的是使用與非門(NAND Gate)或或非門(NOR Gate)構建。以下分別介紹這兩種實現方式:

1. 使用與非門實現RS鎖存器

使用兩個與非門可以實現一個基本的RS鎖存器。兩個與非門的輸入和輸出相互交叉耦合,形成正反饋回路。當Set(S)輸入為高電平時,通過與非門的邏輯運算,可以使得輸出Q置為1;同樣地,當Reset(R)輸入為高電平時,可以使得輸出Q置為0。當Set(S)和Reset(R)輸入均為低電平時,由于正反饋回路的存在,RS鎖存器將保持當前的狀態不變。

2. 使用或非門實現RS鎖存器

與與非門類似,兩個或非門也可以構建成RS鎖存器。但是需要注意的是,由于或非門的邏輯特性與與非門相反(全0輸出1,有1輸出0),因此在使用或非門實現RS鎖存器時,需要調整輸入信號的邏輯電平。具體來說,當Set(S)輸入為低電平時(相當于與非門中的高電平),通過或非門的邏輯運算,可以使得輸出Q置為1;同樣地,當Reset(R)輸入為低電平時(相當于與非門中的高電平),可以使得輸出Q置為0。當Set(S)和Reset(R)輸入均為高電平時(相當于與非門中的低電平),RS鎖存器將保持當前的狀態不變。

六、RS鎖存器的應用實例

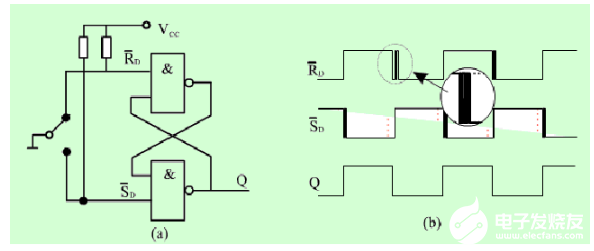

基本RS鎖存器雖然電路相當簡單,但有很廣泛的使用,下圖是在時序電路是廣泛使用的消除抖動開關電路的使用的例子。

我們通常使用的開關一般是機械觸點實現開關的合上和斷開的,由于機械觸點存在彈性,這就決定了當它們合上的時候,產生反彈的問題,反映在電信號上將出現不規則的脈沖信號,若要求合上輸出就為低電平時,就須通過電路加以改進,此圖就實現變個功能。

RS鎖存器由于其簡單性和實用性,在數字系統中有著廣泛的應用。以下列舉幾個典型的應用實例:

寄存器:在CPU中,寄存器是存儲臨時數據的重要部件。RS鎖存器可以作為寄存器的一部分,用于存儲和保持CPU執行指令時所需的臨時數據。

觸發器:觸發器是數字電路中用于存儲和傳輸信息的基本單元。RS鎖存器可以作為觸發器的一種基礎形式,雖然在實際應用中更常見到的是D觸發器、JK觸發器或T觸發器等,但RS鎖存器為這些更復雜的觸發器提供了基礎概念。通過添加時鐘信號或其他控制邏輯,RS鎖存器可以被擴展為這些更高級的觸發器。

開關電路:在數字電子學中,RS鎖存器經常被用作簡單的開關電路。例如,在控制系統中,它可以根據外部信號(如按鈕或傳感器)的輸入來開啟或關閉某個電路。當Set信號被激活時,電路打開;當Reset信號被激活時,電路關閉。

同步控制:在需要精確同步的電路中,RS鎖存器可以用來確保不同部分的操作按照預定的順序進行。通過精心設計的時鐘信號和觸發邏輯,可以確保RS鎖存器在適當的時候接收Set或Reset信號,從而控制電路的同步操作。

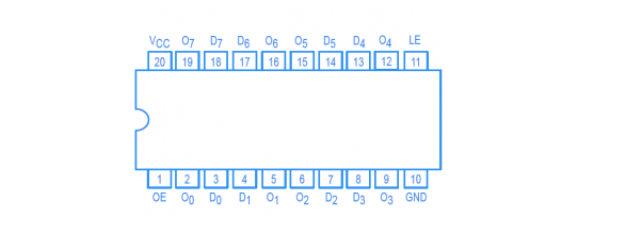

數據鎖存:在數據傳輸過程中,為了防止數據丟失或錯誤,經常需要使用鎖存器來暫存數據。RS鎖存器可以在接收到有效數據后,將其鎖存起來,直到下一個時鐘周期或觸發信號到來時才釋放數據。這種特性使得RS鎖存器在數據通信和存儲系統中非常有用。

狀態機:在狀態機設計中,RS鎖存器可以用來表示系統的不同狀態。通過控制Set和Reset信號的輸入,可以切換系統的狀態,并根據當前狀態執行相應的操作。雖然在實際應用中,更復雜的觸發器(如JK觸發器)可能更適合用于狀態機設計,但RS鎖存器作為基礎概念仍然具有重要的指導意義。

故障檢測和恢復:在數字系統中,故障檢測和恢復是非常重要的功能。RS鎖存器可以通過其雙穩態特性來檢測電路中的故障,并在檢測到故障時通過Reset信號將系統恢復到初始狀態。這種機制有助于提高系統的可靠性和穩定性。

時序電路中的時序元素:在時序電路中,RS鎖存器可以作為時序元素之一,與其他時序元素(如時鐘、計數器等)協同工作,實現復雜的時序控制功能。例如,在計數器設計中,RS鎖存器可以用來存儲計數器的當前值,并在需要時將其輸出到外部電路。

-

時鐘

+關注

關注

11文章

1747瀏覽量

131802 -

鎖存器

+關注

關注

8文章

908瀏覽量

41645 -

RS觸發器

+關注

關注

3文章

101瀏覽量

18045

發布評論請先 登錄

相關推薦

RS鎖存器的工作原理和應用實例

RS鎖存器的工作原理和應用實例

評論