SLM片內(nèi)監(jiān)控IP數(shù)據(jù)分析為高價(jià)值應(yīng)用提供了更為自動(dòng)化的數(shù)據(jù)分析手法。

一直以來(lái),片內(nèi)監(jiān)控IP是為開(kāi)發(fā)者提供量測(cè)芯片內(nèi)部工作狀態(tài),評(píng)估產(chǎn)品功耗等關(guān)鍵性能指標(biāo)的核心技術(shù)方案。片內(nèi)監(jiān)控IP(例如常見(jiàn)的ring oscillator)采集的數(shù)據(jù)有助于在芯片制造階段(即芯片放入最終設(shè)備之前)了解和判斷芯片是否滿(mǎn)足必要的功耗或性能要求。然而,這個(gè)過(guò)程中的挑戰(zhàn)在于:即便能在制造測(cè)試不同階段期間收集所有數(shù)據(jù),但數(shù)據(jù)分析方法仍大量依賴(lài)于手動(dòng)操作,而且需要經(jīng)驗(yàn)豐富的產(chǎn)品開(kāi)發(fā)者運(yùn)用專(zhuān)業(yè)知識(shí)來(lái)預(yù)處理和解釋數(shù)據(jù)分析結(jié)果。

如今,芯片生命周期管理(Silicon Lifecycle Management )解決方案的生產(chǎn)和監(jiān)控分析方案取得了長(zhǎng)足進(jìn)步,大大提高了分析過(guò)程的自動(dòng)化程度,幫助用戶(hù)進(jìn)一步自動(dòng)化識(shí)別產(chǎn)品功耗和性能等關(guān)鍵問(wèn)題,大大提升了開(kāi)發(fā)效率。此外,片內(nèi)監(jiān)控IP數(shù)據(jù)分析還首次實(shí)現(xiàn)了對(duì)Vmin優(yōu)化等關(guān)鍵應(yīng)用的自動(dòng)化處理。將嵌入式監(jiān)控IP的數(shù)據(jù)與前沿機(jī)器學(xué)習(xí)算法相結(jié)合,有助于確定更低、更優(yōu)的Vmin值,從而降低器件功耗并延長(zhǎng)現(xiàn)場(chǎng)使用壽命,并顯著減少測(cè)試成本。

SLM片內(nèi)監(jiān)控IP

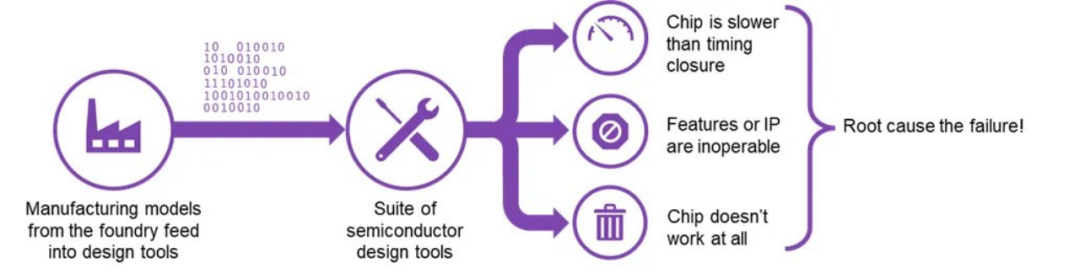

如圖1所示,在完成產(chǎn)品設(shè)計(jì)和流片后,可能會(huì)遇到這樣的問(wèn)題:實(shí)際芯片的運(yùn)行速度比規(guī)格值慢,設(shè)計(jì)中的某些IP不起作用(例如,4核器件設(shè)計(jì)的其中2個(gè)內(nèi)核不起作用),或者芯片已完全失效。

▲圖 1:首次流片中遇到的典型問(wèn)題

此時(shí),產(chǎn)品良率負(fù)責(zé)人或產(chǎn)品開(kāi)發(fā)者需要準(zhǔn)確了解芯片內(nèi)部發(fā)生的情況,嘗試找出這些問(wèn)題的根本原因并加以調(diào)試。這通常要用到嵌入式SLM片內(nèi)監(jiān)控IP。另外,工藝、電壓和溫度(PVT)傳感器也可以為根本原因分析提供關(guān)鍵信息。

雖然PVT IP用途很廣,但在目前的先進(jìn)SoC中,用于測(cè)量芯片功耗和性能的工藝檢測(cè)IP正日益發(fā)揮關(guān)鍵價(jià)值。電壓傳感IP的分析數(shù)據(jù)有助于檢測(cè)芯片的具體壓降狀況,并直接與測(cè)試儀上特定的測(cè)試失敗情況相關(guān)聯(lián)。與此類(lèi)似,溫度傳感IP的分析數(shù)據(jù)可以揭示芯片內(nèi)部的溫度梯度(例如芯片某區(qū)域存在過(guò)熱問(wèn)題),并直接對(duì)應(yīng)到測(cè)試儀上的特定測(cè)試失效結(jié)果,進(jìn)而協(xié)助找出失效的根本原因。

相對(duì)來(lái)說(shuō)工藝檢測(cè)IP主要用于測(cè)量芯片的工藝健康狀況,屬于hard IP,是專(zhuān)為特定代工廠的各個(gè)工藝節(jié)點(diǎn)而設(shè)計(jì)的。此類(lèi)器件中包含由各種反相器、NAND或NOR標(biāo)準(zhǔn)單元構(gòu)成的環(huán)形振蕩器鏈(ring oscillator),在設(shè)計(jì)中通常用于組成簡(jiǎn)單、獨(dú)立且同構(gòu)的邏輯集群。例如,采用反相器標(biāo)準(zhǔn)單元的環(huán)形振蕩器由奇數(shù)個(gè)反相器組成,每個(gè)反相器的輸出端都連接到下一個(gè)反相器的輸入端,而最后一個(gè)單元的輸出端則連接至第一個(gè)單元的輸入端,從而形成閉環(huán)。正如其名,器件導(dǎo)通時(shí),這些RO鏈將會(huì)自限性地快速振蕩。在正常情況下,RO鏈將以盡可能高的頻率運(yùn)行;而一旦芯片出現(xiàn)異常或失效,其振蕩頻率會(huì)顯著降低。

從這些監(jiān)控IP獲得的數(shù)據(jù)通常需經(jīng)過(guò)手動(dòng)分析并繪制成圖表,以便與代工廠的流片前時(shí)序模型進(jìn)行比較。在極端情況下,可能會(huì)遇到保持時(shí)間違例等時(shí)序相關(guān)問(wèn)題,例如實(shí)際芯片比時(shí)序模型快,或者芯片的運(yùn)行速度達(dá)不到設(shè)計(jì)性能要求。在這兩種情況下,都可以通過(guò)SLM片內(nèi)傳感IP數(shù)據(jù)分析方案來(lái)進(jìn)一步找出根本原因,并識(shí)別導(dǎo)致這些時(shí)序問(wèn)題的具體cell。此外,如果性能表現(xiàn)在正常范圍內(nèi),但設(shè)計(jì)的裕量過(guò)大,則可以在確保仍滿(mǎn)足性能要求的前提下,通過(guò)選擇速度較慢的cell來(lái)進(jìn)一步降低功耗。

Path Margin Monitor是一種新型嵌入式監(jiān)控IP,目前也正廣泛采用。這些監(jiān)控IP會(huì)在產(chǎn)品制造測(cè)試期間,測(cè)量特定功能邏輯路徑的裕量,以此來(lái)提高芯片特征測(cè)量結(jié)果的質(zhì)量。不過(guò),與作為hard IP且放置在芯片裸片外圍的工藝檢測(cè)IP不同,PMM屬于soft IP,可以獨(dú)立于工藝節(jié)點(diǎn)合成到設(shè)計(jì)中,并放置在任何邏輯路徑旁。通過(guò)定期測(cè)量路徑的裕度,PMM使開(kāi)發(fā)者能夠評(píng)估器件在使用壽命內(nèi)的老化情況。器件的裕度可能會(huì)隨器件老化而降低。而PMM的數(shù)據(jù)可以提示是否需要調(diào)整器件的頻率或工作電壓,從而能夠延長(zhǎng)器件的使用壽命,此外還有助于開(kāi)發(fā)者在器件發(fā)生故障之前識(shí)別并召回所有即將出現(xiàn)故障的器件。

SLM片內(nèi)監(jiān)控分析的興起

分析來(lái)自片內(nèi)監(jiān)控IP的數(shù)據(jù)一直都需要手動(dòng)操作,非常耗時(shí)費(fèi)力。這個(gè)過(guò)程通常涉及收集和存儲(chǔ)大量數(shù)據(jù),然后還要從數(shù)據(jù)庫(kù)中下載數(shù)據(jù)。繼而,開(kāi)發(fā)者必須花費(fèi)數(shù)小時(shí)手動(dòng)分類(lèi),定義合并和堆疊數(shù)據(jù)集以生成一些圖表。期間還需要自行評(píng)估并確定是否存在要采取糾正措施的問(wèn)題。這是一個(gè)繁瑣而緩慢的過(guò)程,必須周而復(fù)始地進(jìn)行。在芯片的生命周期中,從早期新產(chǎn)品導(dǎo)入(NPI)階段到大批量制造(HVM)期間的維護(hù)狀態(tài)下,都必須執(zhí)行這個(gè)過(guò)程,以此觀察芯片隨時(shí)間推移的運(yùn)行情況。因此,SLM In-Chip Monitor Analytics的目標(biāo)是自動(dòng)執(zhí)行這一繁瑣分析過(guò)程,讓開(kāi)發(fā)者可以一鍵獲得可行的信息,從而將相關(guān)耗時(shí)從數(shù)小時(shí)縮短至幾分鐘。

為實(shí)現(xiàn)這個(gè)自動(dòng)化目標(biāo),需要將以下幾個(gè)要素整合到同一個(gè)分析解決方案中:

來(lái)自監(jiān)控IP的數(shù)據(jù)

來(lái)自這些監(jiān)控器的設(shè)計(jì)元數(shù)據(jù),例如物理特征 - 2/3/4鰭片變體、SVT/LVT/ULVT Vt或閾值電壓樣式

仿真元數(shù)據(jù),例如FF/TT/SS/FS/SFcorner 條件

測(cè)試元數(shù)據(jù),例如測(cè)試芯片時(shí)的電壓、頻率和溫度

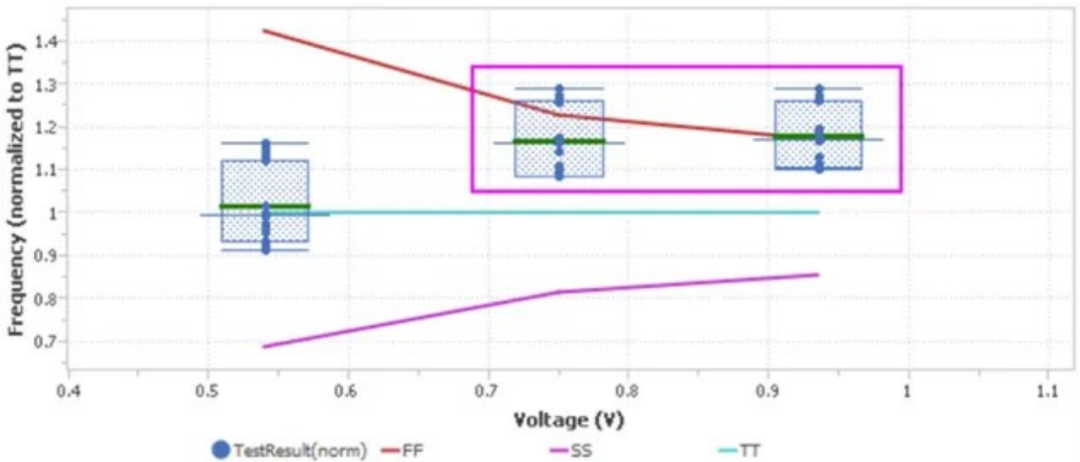

下方圖2為自動(dòng)化目標(biāo)差距分析的結(jié)果。這是一個(gè)標(biāo)準(zhǔn)漏斗圖,描繪了所有生產(chǎn)的芯片中,具有相同物理特性的RO鏈在不同電壓下的測(cè)試結(jié)果,并與foundry的仿真設(shè)計(jì)目標(biāo)進(jìn)行了比較。實(shí)際上,就是獲取測(cè)試儀的測(cè)量結(jié)果并將其除以TT(Typical, Typical)目標(biāo)值,其中TT代表典型PMOS和典型NMOS仿真時(shí)序結(jié)果。此外,為了完善漏斗圖的邊界,圖中還加入了FF(Fast, Fast)目標(biāo)值和SS(Slow, Slow)目標(biāo)值,并將它們同樣除以TT目標(biāo)值,以確定在漏斗圖中的相對(duì)位置。

▲圖 2:?jiǎn)蝹€(gè)環(huán)形振蕩器鏈在三(3)種不同電壓下測(cè)試的漏斗圖

理想情況下,如果沒(méi)有異樣或偏差,所有經(jīng)測(cè)試的芯片性能都應(yīng)該位于青色的TT線上。但在本例中,測(cè)試期間提高電壓時(shí),有一半芯片的運(yùn)行速度要比FF目標(biāo)值快,這表示存在掃描鏈hold timing violation。因此,如果這些器件發(fā)生掃描鏈?zhǔn)В梢越柚吮O(jiān)控分析來(lái)找出問(wèn)題的根本原因。

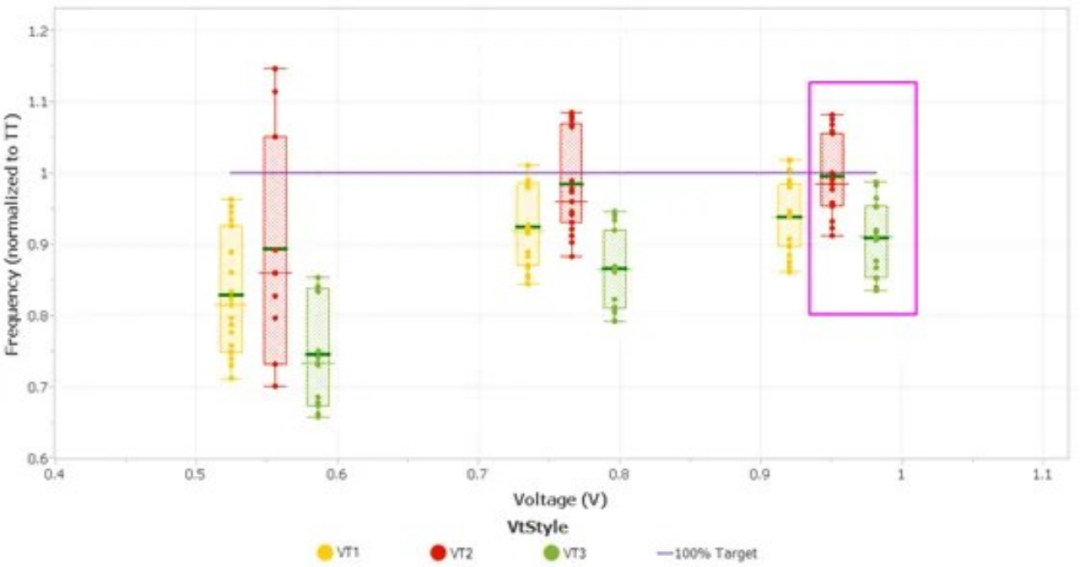

如下方圖3所示,監(jiān)控分析已擴(kuò)展到包含3條具有獨(dú)特物理特征的RO鏈。它們的鰭片數(shù)量、柵極類(lèi)型以及負(fù)載電容均相同,但Vt(例如閾值電壓)不同。對(duì)于其各自的不同Vt,測(cè)試中分別標(biāo)記為VT1、VT2和VT3。

▲圖 3:Vt不同的3個(gè)獨(dú)特RO鏈的箱線圖

結(jié)果顯示,在較高電壓下,RO鏈間的偏差較大,其中VT2大致達(dá)到目標(biāo),而VT3低于目標(biāo)。此類(lèi)偏差預(yù)示著潛在的時(shí)序故障。

監(jiān)控分析解決方案可以提供更多分析信息,以便進(jìn)行詳盡的實(shí)驗(yàn)設(shè)計(jì)(DOE),了解各種物理晶體管特征會(huì)如何影響多個(gè)RO鏈中的性能,從而確定DOE的哪個(gè)部分對(duì)與TT目標(biāo)值的差距影響最大。

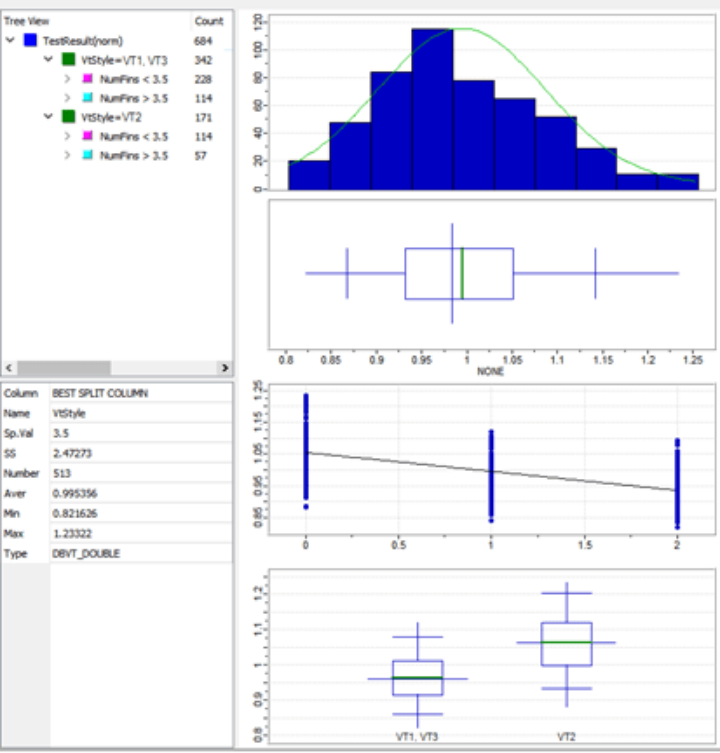

例如,下方圖4顯示了一個(gè)多變量DOE,可以獨(dú)立執(zhí)行一系列詳盡的物理實(shí)驗(yàn),確認(rèn)圖3中所示的研究結(jié)果,即在統(tǒng)計(jì)上,VT3與目標(biāo)的差距明顯比VT2要大。此外,所有實(shí)驗(yàn)的相關(guān)性表明,Vt類(lèi)型對(duì)該差距的影響要比鰭片、柵極類(lèi)型等更大。

圖4中還包含了一個(gè)回歸樹(shù)。回歸樹(shù)是一種統(tǒng)計(jì)方法,可以通過(guò)分類(lèi)變量來(lái)分解連續(xù)變量。本例中,分類(lèi)變量為RO DOE,即構(gòu)成RO的所有物理特征;連續(xù)變量為與目標(biāo)的差距。對(duì)整個(gè)芯片總體進(jìn)行實(shí)驗(yàn)排列之后,回歸樹(shù)可以指示在其中哪個(gè)分類(lèi)變量(例如物理屬性)對(duì)連續(xù)變量的影響最大。在本例中,Vt類(lèi)型是導(dǎo)致目標(biāo)差距最大的相關(guān)因素。對(duì)于某條關(guān)鍵路徑,如果懷疑存在負(fù)裕量問(wèn)題或遇到了芯片故障,且認(rèn)為這些問(wèn)題是由VT3引起的,則可以考慮將VT3單元更換為VT2單元,因?yàn)閂T2的性能更具可預(yù)測(cè)性。

▲圖 4:確定哪些物理特征對(duì)與TT目標(biāo)值的差距影響最大的多變量DOE

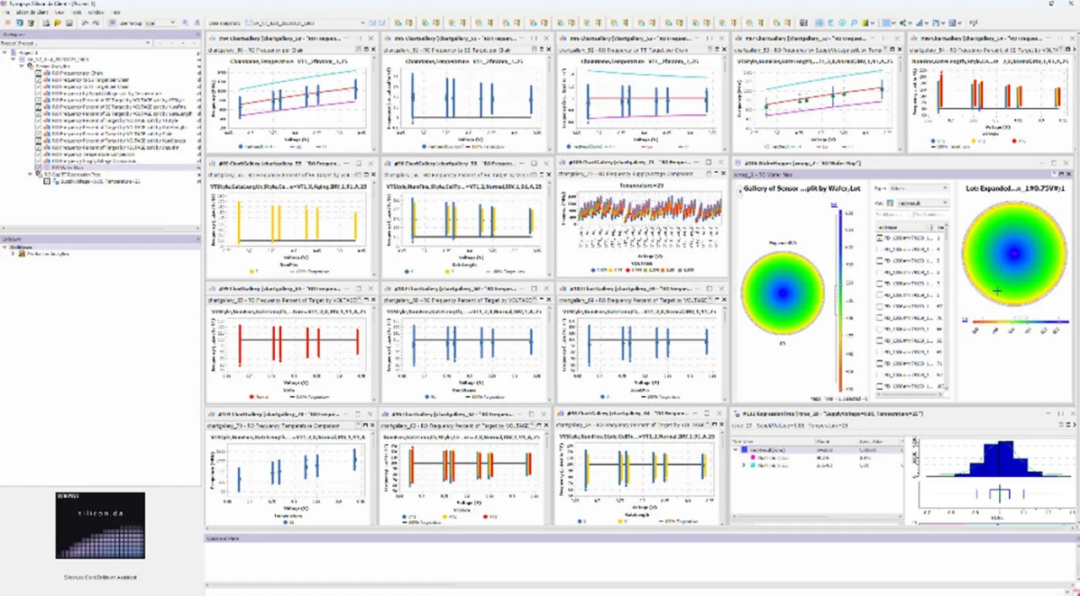

使用監(jiān)控分析解決方案對(duì)芯片進(jìn)行工藝分類(lèi)以實(shí)現(xiàn)自動(dòng)化的例子還有很多,圖5為一個(gè)典型分析工具輸出模板,用戶(hù)可以從中選擇和查看多種不同的分析輸出報(bào)告。

▲圖 5:由Silicon.da Monitor Analytics執(zhí)行的工藝分類(lèi)分析報(bào)告。

不過(guò),工藝分類(lèi)只是監(jiān)控分析的主要用例之一。其他用例還有許多,例如Vmin預(yù)測(cè)。

Vmin預(yù)測(cè)

Vmin預(yù)測(cè)具有諸多優(yōu)勢(shì),目前也正日益普及。首先,確定器件在滿(mǎn)足性能要求情況下的最低運(yùn)行電壓對(duì)于提升器件能效有著重大影響。運(yùn)行電壓越低,器件消耗的電量就越少。這主要體現(xiàn)在兩個(gè)方面:(1)提高器件/設(shè)備(例如手機(jī))的性能;(2)最終延長(zhǎng)器件/設(shè)備的使用壽命。不過(guò),盡管這非常重要,但每個(gè)器件的最低工作電壓各不相同,這并不容易實(shí)現(xiàn)。要想獲得每個(gè)器件的真實(shí)Vmin,就必須大量進(jìn)行制造測(cè)試,這不僅耗費(fèi)大量時(shí)間,影響產(chǎn)品上市進(jìn)程,還會(huì)增加測(cè)試成本。如果有一種方法可以精確預(yù)測(cè)真實(shí)的Vmin,且無(wú)需大量投入時(shí)間和成本,無(wú)疑將為產(chǎn)品開(kāi)發(fā)者創(chuàng)造巨大價(jià)值。

盡管多年來(lái)開(kāi)發(fā)者們一直在嘗試預(yù)測(cè)Vmin,但并不是所有的方法都能取得理想效果。為了塑造準(zhǔn)確的Vmin預(yù)測(cè)模型,需要以下幾個(gè)關(guān)鍵要素:(1)穩(wěn)健的機(jī)器學(xué)習(xí)(ML)模型;(2)實(shí)際測(cè)量并收集器件樣本的Vmin,以協(xié)助訓(xùn)練模型;(3)來(lái)自監(jiān)控IP的數(shù)據(jù)(例如前面討論過(guò)的PVT和PMM),以提供器件的更多特征,從而提高模型的準(zhǔn)確度。

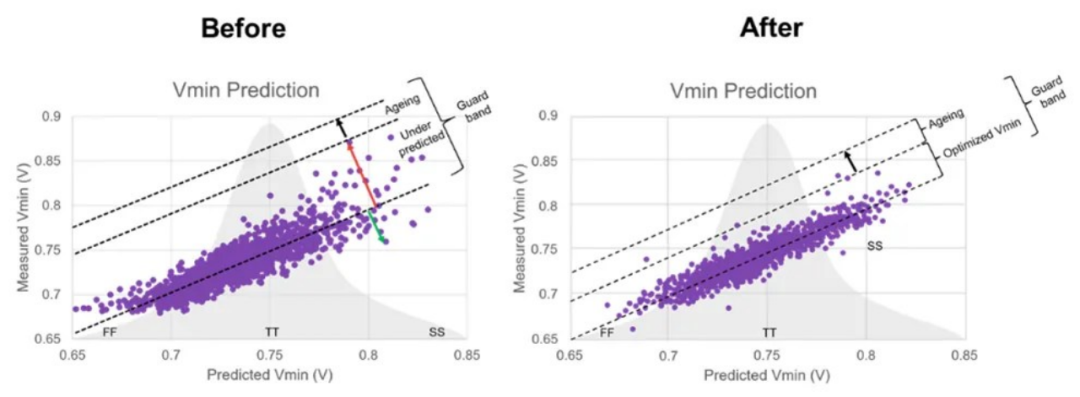

下方圖6顯示了兩種不同Vmin預(yù)測(cè)模型的準(zhǔn)確度差異。預(yù)測(cè)模型越好,測(cè)量值與預(yù)測(cè)值之間的相關(guān)性就越緊密(右側(cè)圖表)。理想情況是模型可以準(zhǔn)確預(yù)測(cè)要測(cè)量對(duì)象的Vmin。

▲圖 6:準(zhǔn)確度不同的兩個(gè)Vmin預(yù)測(cè)模型

圖中,x=y線下方表示預(yù)測(cè)的Vmin與該器件的Vmin測(cè)量值相同或較之更高,因此線下方的器件均符合要求。而線上方則表示預(yù)測(cè)值小于測(cè)量值,相關(guān)器件不符合要求。為了確保器件良率足夠高,同時(shí)考慮補(bǔ)償器件老化影響,考慮在Vmin預(yù)測(cè)值的基礎(chǔ)上增加一個(gè)小幅度電壓(guard band)。不過(guò),在補(bǔ)償電壓之前,如果大多數(shù)器件已符合要求,則可能不需要額外的guard band。在這種情況下,可以將預(yù)測(cè)的Vmin作為測(cè)試起點(diǎn),進(jìn)一步展開(kāi)Vmin測(cè)試,尋找更優(yōu)Vmin。

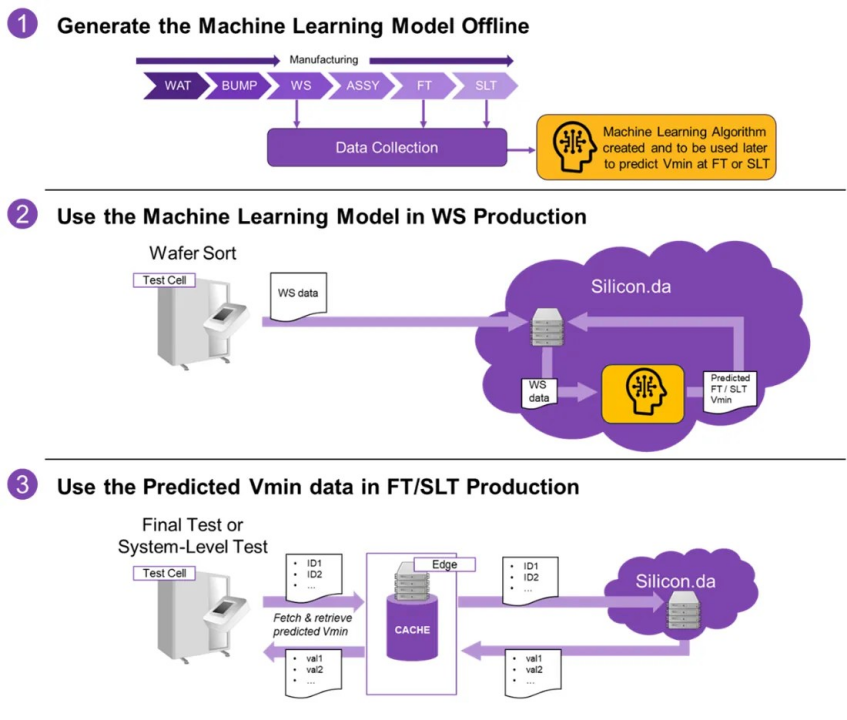

要將Vmin預(yù)測(cè)模型投入實(shí)際應(yīng)用,可參考圖7在生產(chǎn)中建立該模型的相關(guān)規(guī)程。

▲圖 7:Vmin預(yù)測(cè)的相關(guān)規(guī)程

其中第一步是在預(yù)先確定的一組器件上創(chuàng)建和訓(xùn)練ML模型。這一步需實(shí)際測(cè)量Vmin,收集的Vmin測(cè)量數(shù)據(jù)是訓(xùn)練模型的關(guān)鍵要素。

第二步是將下一批新芯片在晶圓分類(lèi)過(guò)程中收集的生產(chǎn)數(shù)據(jù)應(yīng)用于該模型。請(qǐng)注意,此時(shí)不再需要實(shí)際執(zhí)行Vmin測(cè)試,因?yàn)镸L模型將能預(yù)測(cè)在FT和/或SLT期間要使用的Vmin值。預(yù)測(cè)的Vmin將離線存儲(chǔ)在數(shù)據(jù)庫(kù)中,以供FT或SLT測(cè)試期間使用。

第三步(也是最后一步)為在FT或SLT測(cè)試期間利用預(yù)測(cè)的Vmin。測(cè)試開(kāi)發(fā)者可以將該預(yù)測(cè)值作為最終產(chǎn)品的Vmin;如需改進(jìn)結(jié)果,可以將Vmin 預(yù)測(cè)值用作進(jìn)一步測(cè)量Vmin測(cè)試的起點(diǎn)。開(kāi)發(fā)者可以將此值作為起點(diǎn),對(duì)測(cè)量的Vmin進(jìn)一步展開(kāi)測(cè)試。利用預(yù)測(cè)值作為起始點(diǎn),從而顯著減少測(cè)試時(shí)間。

為綜上所言,為了在整個(gè)生命周期內(nèi)監(jiān)控和維護(hù)器件的健康狀況,并改善功耗和性能等關(guān)鍵運(yùn)行指標(biāo),開(kāi)發(fā)者需要了解復(fù)雜SoC中的實(shí)際運(yùn)行情況。不然就像無(wú)頭蒼蠅,只能通過(guò)耗費(fèi)大量的開(kāi)發(fā)和測(cè)試成本才能加以改進(jìn)。新思SLM Analytics的片內(nèi)監(jiān)控IP數(shù)據(jù)分析方案另辟蹊徑為廣大開(kāi)發(fā)者提供了直觀呈現(xiàn)監(jiān)控?cái)?shù)據(jù)和自動(dòng)生成數(shù)據(jù)分析的技術(shù)思路,從而更高效地實(shí)現(xiàn)這些關(guān)鍵KPI。

-

芯片

+關(guān)注

關(guān)注

456文章

51166瀏覽量

427204 -

機(jī)器學(xué)習(xí)

+關(guān)注

關(guān)注

66文章

8438瀏覽量

133078 -

數(shù)據(jù)分析

+關(guān)注

關(guān)注

2文章

1461瀏覽量

34160

原文標(biāo)題:芯片開(kāi)發(fā)者的Next Level:如何在制造階段快速精準(zhǔn)實(shí)現(xiàn)那些關(guān)鍵KPI?

文章出處:【微信號(hào):Synopsys_CN,微信公眾號(hào):新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

MTIE、TDEV數(shù)據(jù)分析說(shuō)明

數(shù)據(jù)分析需要的技能

加快MIMO測(cè)試速度和降低測(cè)試成本的方法

RF整合到SOC怎么減少測(cè)試成本?

BI分享秀——高度開(kāi)放的數(shù)據(jù)分析經(jīng)驗(yàn)共享

生產(chǎn)數(shù)據(jù)分析的必要性

BI數(shù)據(jù)分析軟件使用指南

如何實(shí)現(xiàn)GPS較短的測(cè)試時(shí)間和較低的測(cè)試成本?

電商數(shù)據(jù)分析攻略,讓你輕松搞定數(shù)據(jù)分析!

利用測(cè)試排序儀器降低測(cè)試成本

用標(biāo)準(zhǔn)數(shù)據(jù)分析方案做數(shù)據(jù)可視化更省成本

使用校準(zhǔn)降低衛(wèi)星設(shè)計(jì)和測(cè)試成本

SLM片內(nèi)監(jiān)控IP數(shù)據(jù)分析顯著減少測(cè)試成本

SLM片內(nèi)監(jiān)控IP數(shù)據(jù)分析顯著減少測(cè)試成本

評(píng)論