1. 概述

Spartan6系列是一類低成本高容量的FPGA,采用45nm低功耗敷銅技術,能在功耗、性能、成本之間很好地平衡;Spartan6系列內部采用雙寄存器、6輸入的LUT,還有一系列的內建系統(tǒng)級模塊,這些系統(tǒng)級模塊有18Kb Block Ram、第二代DSP48A21 Slice、SDRAM存儲器接口(DDR接口)、強健的混合型時鐘管理模塊、Select IO技術、優(yōu)化的高速串行收發(fā)器GTP Transceiver、PCIE接口、先進的系統(tǒng)級電源管理模式、可自動檢測配置、具有AES和Device DNA保護的加強IP。Spartan6特別適合于高容量的邏輯設計、面向用戶的DSP設計、低成本設計。

圖 1Spartan-6芯片XC6SLX16

2. Spartan6的特點

兩小類

Spartan-6 LX FPGA優(yōu)勢是邏輯優(yōu)化;

Spartan-6 LXT FPGA優(yōu)勢是高速串行連接性;

低設計成本

低動靜態(tài)功耗

45nm技術對功耗做了優(yōu)化;

睡眠模式零功耗;

掛起模式時可保持芯片內部狀態(tài)、并有多個引腳可實現(xiàn)芯片的喚醒操作;

LX FPGAs, -1L使用1.0V的內核電壓;LX and LXT FPGAs, -2, -3, and -3N使用1.2V的內核電壓;

Select IO可采用多電平標準

每對差分IO最高可達1080Mb/s的數(shù)據(jù)傳輸速度;

每個引腳的輸出電流最高可達24mA;

1.2--3.3V電平標準和協(xié)議供選擇;

低功耗的HSTL、SSTL存儲器接口技術;

符合熱插拔規(guī)范;

可調節(jié)IO接口片斜率以提高信號完整性;

高速串行收發(fā)器(LXT FPGA才有)

最高可達3.2Gbps;

支持的高速接口包括Serial ATA, Aurora,1G Ethernet, PCI Express, OBSAI, CPRI, EPON,GPON, DisplayPort, and XAUI;

PCIE接口設計用到的Endpoint block(LXT FPGA才有)

支持PCI接口,與33MHZ、32bit/64bitPCI協(xié)議兼容

高效的DSP48A1模塊

快速的18X18乘法器或48bit累加器,具備流水化瀑布化能力;

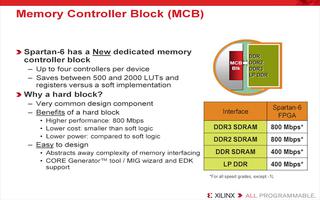

集成的存儲器控制接口模塊

支持DDR, DDR2, DDR3, and LPDDR;

數(shù)據(jù)率最高可達800Mb/s;

存儲器控制接口有多個端口,每個端口包含各自的獨立地FIFO,可實現(xiàn)存儲器的高速讀寫;

足夠的邏輯資源

可選的移位寄存器或分布式RAM;

高效的6輸入LUT;

Block RAM

每個Block RAM 18Kb大小,一個Block RAM可以通過編程當做兩個9Kb大小的Block RAM使用;

Clock Management Tile (CMT)時鐘管理模塊

16個低偏斜的時鐘網(wǎng)絡;內部DCM可消除時鐘偏斜和周期扭曲變化;內部PLL可實現(xiàn)相位鎖定,實現(xiàn)時鐘低抖動;

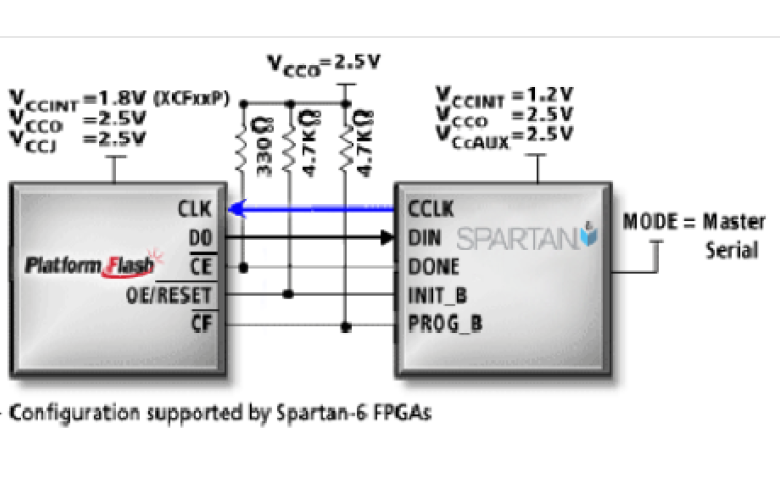

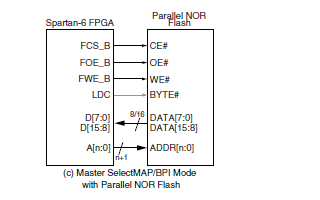

簡化的器件配置

有兩個引腳用于配置方式的自動檢測;

支持SPI Flash(最多4個)和Nor Flash配置;

以JTAG進行編程的 Xilinx Platform Flash ;

支持多重引導,便于遠程升級;

對設計的安全保護

獨一無二的Device DNA標志用于設計認證;

AES比特流加密;

支持MicroBlaze軟處理器系統(tǒng)

豐富的工業(yè)IP和參考設計

3. Spartan6的資源

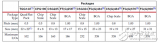

下表是Spartan-6系列各型號的邏輯資源情況,對該表的解釋如下:

每個SLICE包含4個LUT和8個flip-flops;

每個DSP48A1 slice包含1個18X18乘法器、1個48bit累加器、1個加法器;

每個18Kb的Block RAM可以用作2個9Kb的Block RAM;

每個CMT包含2個DCM和1個PLL;

在-3N 速度等級的器件里沒有存儲器接口(DDR接口);

表格 1Spartan-6 FPGA邏輯資源一覽表

下表是Spartan-6系列的IO資源情況,其中,GTP的個數(shù)是指GTP Lane的個數(shù)。

表格 2 Spartan-6系列IO資源一覽表

-

Spartan-6

+關注

關注

4文章

38瀏覽量

17581

發(fā)布評論請先 登錄

相關推薦

用Spartan-6和Virtex-6設計——賽靈思培訓課程

Spartan-6 FPGA工業(yè)影像目標設計平臺(Xilin

一文詳解Spartan-6系列IO Tile結構

Spartan6開發(fā)中bufpll mapping error

Spartan-6 FPGA Configuration User Guide

Xilinx Spartan-6系列封裝概述和管腳分配

Spartan-6 FPGA中的DCM功能介紹

spartan-6 FPGA的時鐘資源的用戶指南資料免費下載

spartan-6 FPGA可配置邏輯塊的用戶指南資料免費下載

Spartan-6 FPGA的配置教程說明

Spartan-6系列FPGA的詳細資料概述

Spartan6的特點_Spartan-6系列各型號的邏輯資源

Spartan6的特點_Spartan-6系列各型號的邏輯資源

評論