觸發器穩態的判斷是數字電路設計中的一個重要環節,它涉及到觸發器在不同輸入條件下的輸出狀態穩定性。

一、觸發器穩態判斷的基本方法

- 理解觸發器類型 :

首先,需要明確觸發器的類型,如RS觸發器、D觸發器、JK觸發器等。不同類型的觸發器具有不同的輸入端和輸出端,以及不同的穩態特性。 - 分析輸入條件 :

觸發器的穩態取決于其輸入條件。對于RS觸發器,需要分析R和S兩個輸入端的電平狀態;對于D觸發器,則需要關注D輸入端和時鐘信號(CLK)的狀態;對于JK觸發器,則需要考慮J、K輸入端以及時鐘信號(CLK)的狀態。 - 查閱真值表或狀態轉換圖 :

觸發器的真值表或狀態轉換圖是判斷穩態的重要工具。真值表列出了所有可能的輸入組合及其對應的輸出狀態,而狀態轉換圖則直觀地展示了觸發器在不同輸入條件下的狀態轉換過程。 - 確定穩態條件 :

根據觸發器的真值表或狀態轉換圖,可以確定觸發器的穩態條件。穩態條件是指觸發器在特定輸入組合下能夠保持輸出狀態不變的條件。

二、不同類型觸發器的穩態特性

- RS觸發器 :

- 穩態條件 :當R=0且S=0時,觸發器保持其當前狀態不變(保持狀態);當R=0且S=1時,觸發器被置為復位狀態(Q=0);當R=1且S=0時,觸發器被置為置位狀態(Q=1);當R=1且S=1時,觸發器處于禁止狀態(輸出不定)。

- 判斷方法 :通過檢查R和S輸入端的電平狀態,結合真值表或狀態轉換圖,可以確定RS觸發器的穩態。

- D觸發器 :

- 穩態條件 :D觸發器的穩態取決于時鐘信號(CLK)的邊沿(上升沿或下降沿)以及D輸入端的電平狀態。當時鐘信號邊沿到來時,D觸發器的輸出Q將跟隨D輸入端的電平狀態。

- 判斷方法 :關注時鐘信號的變化,并記錄D輸入端在時鐘邊沿前的電平狀態。根據時鐘信號的邊沿類型和D輸入端的電平狀態,結合真值表或狀態轉換圖,可以判斷D觸發器的穩態。

- JK觸發器 :

- 穩態條件 :JK觸發器的穩態取決于時鐘信號(CLK)的邊沿以及J和K輸入端的狀態。當時鐘信號邊沿到來時,JK觸發器的輸出Q將根據J和K的狀態進行翻轉、置位或保持。

- 判斷方法 :同樣需要關注時鐘信號的變化,并記錄J和K輸入端在時鐘邊沿前的狀態。根據時鐘信號的邊沿類型和J、K輸入端的狀態,結合真值表或狀態轉換圖,可以判斷JK觸發器的穩態。

三、注意事項

- 避免不定態 :對于RS觸發器而言,需要特別注意避免R和S同時為1的情況,因為這會導致觸發器進入不定態。在實際應用中,通常會通過添加額外的邏輯電路來確保R和S不會同時為1。

- 時鐘信號的穩定性 :對于D觸發器和JK觸發器而言,時鐘信號的穩定性對觸發器的穩態判斷至關重要。如果時鐘信號存在抖動或不穩定現象,可能會導致觸發器在不應該翻轉的時候翻轉,從而影響系統的穩定性和可靠性。

- 輸入信號的同步性 :在復雜的數字系統中,可能需要多個觸發器協同工作。此時,需要確保各個觸發器的輸入信號是同步的,以避免因信號不同步而導致的錯誤狀態轉換。

- 考慮負載效應 :在實際應用中,觸發器的輸出可能會驅動其他電路或設備。因此,在判斷觸發器的穩態時,還需要考慮負載效應對觸發器輸出狀態的影響。

綜上所述,觸發器穩態的判斷需要結合觸發器的類型、輸入條件以及真值表或狀態轉換圖進行綜合分析。通過仔細分析這些因素并遵循相應的注意事項,可以準確地判斷觸發器的穩態并確保數字系統的穩定性和可靠性。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

RS觸發器

+關注

關注

3文章

101瀏覽量

18047 -

數字電路

+關注

關注

193文章

1629瀏覽量

80823 -

觸發器

+關注

關注

14文章

2003瀏覽量

61350

發布評論請先 登錄

相關推薦

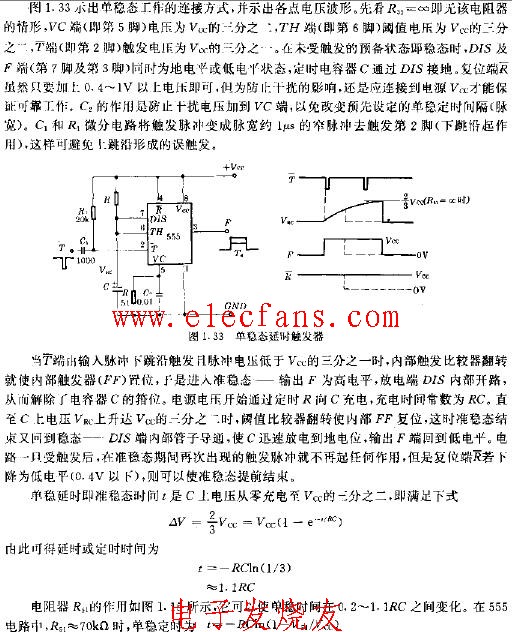

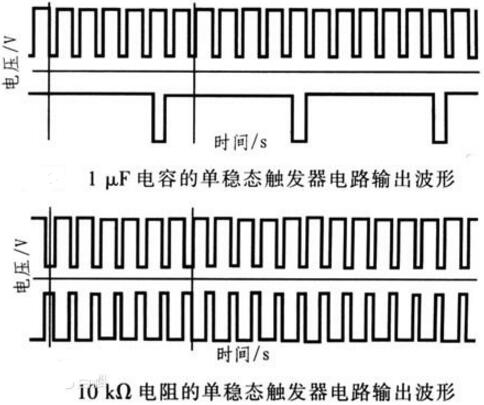

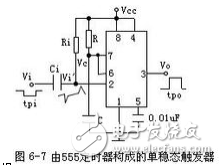

單穩態觸發器的暫穩態時間與什么有關

單穩態觸發器是一種能夠在某個時間間隔內將輸入信號的電平轉換為期望的輸出信號電平的數字電路。在單穩態觸發器中,暫穩態時間是指當

d觸發器有幾個穩態 觸發器上升沿下降沿怎么判斷

穩態是指觸發器在某個特定的輸入狀態下穩定保持輸出的狀態。根據觸發器的類型和觸發方式,觸發器分為很多種類,不同類型的

單穩態觸發器暫穩態由什么來維持

單穩態觸發器(Monostable Trigger)是一種數字電路,它在接收到一個觸發信號后,能夠保持輸出狀態一段時間,然后自動返回到初始狀態。單穩態

觸發器穩態怎么判斷

觸發器穩態怎么判斷

評論