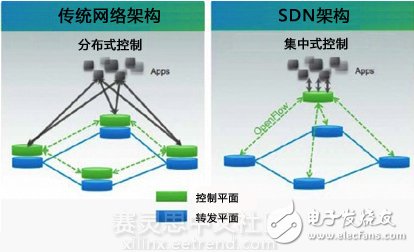

SDN(Software Defined Network, 軟件定義網(wǎng)絡(luò))是一種新型的網(wǎng)絡(luò)架構(gòu),將網(wǎng)絡(luò)的控制平面與數(shù)據(jù)轉(zhuǎn)發(fā)平面進(jìn)行分離,從而通過集中的控制器中的軟件平臺(tái)去實(shí)現(xiàn)可編程化控制底層硬件,實(shí)現(xiàn)對網(wǎng)絡(luò)資源靈活的按需調(diào)配。在SDN網(wǎng)絡(luò)中,網(wǎng)絡(luò)設(shè)備只負(fù)責(zé)單純的數(shù)據(jù)轉(zhuǎn)發(fā),可以采用通用的硬件。而原來負(fù)責(zé)控制的操作系統(tǒng)將提煉為獨(dú)立的網(wǎng)絡(luò)操作系統(tǒng),負(fù)責(zé)對不同業(yè)務(wù)特性進(jìn)行適配。

基于開放協(xié)議的方案的當(dāng)前SDN實(shí)現(xiàn)的主流方案,OpenFlow協(xié)議本身就能控制轉(zhuǎn)發(fā)層面,可以高效且嚴(yán)格地實(shí)現(xiàn)轉(zhuǎn)發(fā)層面和控制層面的分離,天生就適合SDN,因此OpenFlow是實(shí)現(xiàn)SDN的主流開放協(xié)議標(biāo)準(zhǔn)。

圖1:傳統(tǒng)網(wǎng)絡(luò)架構(gòu)與SDN架構(gòu)的對比

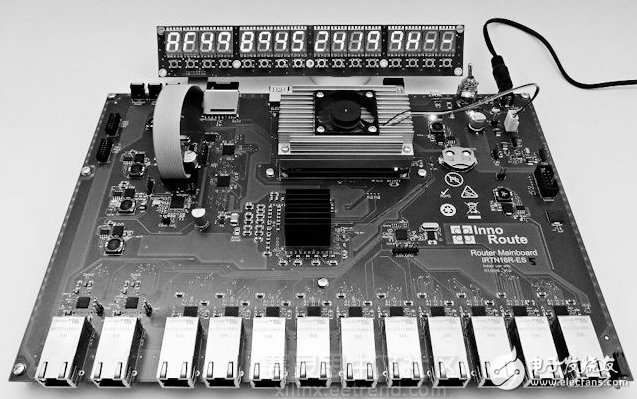

TrustNode是一家來自德國的公司InnoRoute推出的OpenFlow SDN路由板卡,這款產(chǎn)品可擴(kuò)展靈活性高,超低延遲設(shè)計(jì)(2.5微秒),支持IPv6協(xié)議,集成了USB2.0/3.0端口、SD卡槽以及12個(gè)GbE網(wǎng)絡(luò)通信端口。可應(yīng)用到物聯(lián)網(wǎng)(IoT)、工業(yè)級(jí)應(yīng)用以及網(wǎng)絡(luò)接入等領(lǐng)域。

圖2:InnoRoute TrustNode SDN路由板卡正面照

這款產(chǎn)品采用了Intel 1.9 GHz,雙核Atom處理器,4GB RAM,并且移植了Linux操作系統(tǒng),作為控制中心。除此之外,所有的數(shù)據(jù)處理和網(wǎng)絡(luò)通信是放在板卡中心的FPGA中實(shí)現(xiàn)的,采用的是Xilinx Artix-7 A200 FPGA器件,使用了134.6k LUTs、269.2k flip-flops和12.8Mbits BRAM的FPGA資源。

為什么說這款產(chǎn)品靈活擴(kuò)展性比較高呢?因?yàn)樗С钟脩羰褂肵ilinx Vivado HLS Design Suit WebPAck(官網(wǎng)免費(fèi)下載)工具進(jìn)行自定義功能開發(fā),支持VHDL、Verilog和高級(jí)語言(C/C++/SystemC),包括軟件和FPGA IP設(shè)計(jì)都向用戶開放,完善的文檔資源能夠讓用戶快速熟悉自定義功能設(shè)計(jì)和實(shí)現(xiàn)。也就是說借助這款板級(jí)(PCB)SDN,用戶可以縮短將自己產(chǎn)品面市的時(shí)間。

圖3:TrustNode SDN精美外觀設(shè)計(jì)

Xilinx All Programmable FPGA器件提供了該板卡可擴(kuò)展性、超低延遲的特性。Artix-7系列器件是各類成本和功耗敏感型應(yīng)用的最好選擇,例如軟件定義無線電(SDR)、機(jī)器視覺相機(jī)以及可穿戴設(shè)備等。

-

網(wǎng)絡(luò)架構(gòu)

+關(guān)注

關(guān)注

1文章

95瀏覽量

12636 -

sdn

+關(guān)注

關(guān)注

3文章

254瀏覽量

44872

發(fā)布評論請先 登錄

相關(guān)推薦

verilog在psoc中延遲

SY89296L 2.5V/3.3V 2.5GHz可編程延遲線評估板

如何在STM8S103F3上實(shí)現(xiàn)微秒延遲?

可以用TIMER4創(chuàng)建1微秒的延遲嗎?

請問怎么在ucosII中實(shí)現(xiàn)微秒級(jí)的延時(shí)?

如何在StarterWare工程里使用微秒延遲

路由優(yōu)先級(jí)

基于遺傳算法的混合SDN路由節(jié)能算法

實(shí)時(shí)MCU如何實(shí)現(xiàn)超低延遲

如何利用神經(jīng)網(wǎng)絡(luò)預(yù)測閃存尾端延遲的發(fā)生?

TrustNode板級(jí)SDN路由上市_超低延遲2.5微秒

TrustNode板級(jí)SDN路由上市_超低延遲2.5微秒

評論