在數(shù)字邏輯電路中,D觸發(fā)器(Data Flip-Flop)和RS觸發(fā)器(Reset-Set Flip-Flop)是兩種常用的存儲(chǔ)單元。它們?cè)诠δ苌嫌幸欢ǖ南嗨菩裕泊嬖谝恍┎町悺?/p>

一、D觸發(fā)器與RS觸發(fā)器的基本概念

- D觸發(fā)器

D觸發(fā)器是一種具有數(shù)據(jù)輸入(D)、時(shí)鐘輸入(CLK)和輸出(Q)的存儲(chǔ)單元。當(dāng)CLK信號(hào)的上升沿或下降沿到來(lái)時(shí),D觸發(fā)器將輸入端的數(shù)據(jù)D存儲(chǔ)到輸出端Q。D觸發(fā)器具有以下特點(diǎn):

(1)數(shù)據(jù)傳輸:D觸發(fā)器可以實(shí)現(xiàn)數(shù)據(jù)的同步傳輸,即在時(shí)鐘信號(hào)的控制下,數(shù)據(jù)從輸入端D傳輸?shù)捷敵龆薗。

(2)存儲(chǔ)功能:D觸發(fā)器具有存儲(chǔ)功能,可以將輸入端的數(shù)據(jù)D存儲(chǔ)在輸出端Q,實(shí)現(xiàn)數(shù)據(jù)的保持。

(3)時(shí)鐘控制:D觸發(fā)器的存儲(chǔ)功能受到時(shí)鐘信號(hào)的控制,只有在時(shí)鐘信號(hào)的上升沿或下降沿到來(lái)時(shí),數(shù)據(jù)才會(huì)被存儲(chǔ)。

- RS觸發(fā)器

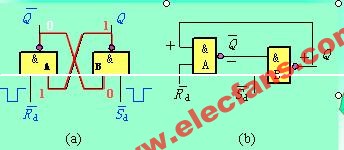

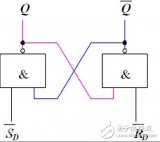

RS觸發(fā)器是一種具有置位(Set)輸入(S)、復(fù)位(Reset)輸入(R)和輸出(Q)的存儲(chǔ)單元。RS觸發(fā)器可以實(shí)現(xiàn)數(shù)據(jù)的置位和復(fù)位操作。RS觸發(fā)器具有以下特點(diǎn):

(1)置位操作:當(dāng)S=1且R=0時(shí),RS觸發(fā)器將輸出端Q置為1。

(2)復(fù)位操作:當(dāng)R=1且S=0時(shí),RS觸發(fā)器將輸出端Q置為0。

(3)保持操作:當(dāng)S=0且R=0時(shí),RS觸發(fā)器保持輸出端Q的當(dāng)前狀態(tài)不變。

(4)無(wú)效狀態(tài):當(dāng)S=1且R=1時(shí),RS觸發(fā)器的狀態(tài)不確定,可能導(dǎo)致輸出端Q的不穩(wěn)定。

二、D觸發(fā)器與RS觸發(fā)器的功能轉(zhuǎn)換

- 利用D觸發(fā)器實(shí)現(xiàn)RS觸發(fā)器

通過(guò)將D觸發(fā)器的輸入端D與RS觸發(fā)器的置位輸入S相連接,可以實(shí)現(xiàn)RS觸發(fā)器的置位功能。同時(shí),通過(guò)將D觸發(fā)器的時(shí)鐘輸入CLK與RS觸發(fā)器的復(fù)位輸入R相連接,可以實(shí)現(xiàn)RS觸發(fā)器的復(fù)位功能。具體實(shí)現(xiàn)方法如下:

(1)置位功能:將D觸發(fā)器的輸入端D與RS觸發(fā)器的置位輸入S相連接,當(dāng)S=1時(shí),D觸發(fā)器的輸出端Q將被置為1。

(2)復(fù)位功能:將D觸發(fā)器的時(shí)鐘輸入CLK與RS觸發(fā)器的復(fù)位輸入R相連接,當(dāng)R=1時(shí),D觸發(fā)器的輸出端Q將被復(fù)位為0。

(3)保持功能:當(dāng)S=0且R=0時(shí),D觸發(fā)器的輸出端Q將保持當(dāng)前狀態(tài)不變。

- 利用RS觸發(fā)器實(shí)現(xiàn)D觸發(fā)器

通過(guò)將RS觸發(fā)器的置位輸入S與復(fù)位輸入R分別與D觸發(fā)器的數(shù)據(jù)輸入D和時(shí)鐘輸入CLK相連接,可以實(shí)現(xiàn)D觸發(fā)器的功能。具體實(shí)現(xiàn)方法如下:

(1)數(shù)據(jù)傳輸:將RS觸發(fā)器的置位輸入S與D觸發(fā)器的數(shù)據(jù)輸入D相連接,當(dāng)S=1時(shí),RS觸發(fā)器的輸出端Q將存儲(chǔ)D觸發(fā)器的數(shù)據(jù)輸入D。

(2)時(shí)鐘控制:將RS觸發(fā)器的復(fù)位輸入R與D觸發(fā)器的時(shí)鐘輸入CLK相連接,當(dāng)R=1時(shí),RS觸發(fā)器的輸出端Q將被復(fù)位為0,從而實(shí)現(xiàn)時(shí)鐘信號(hào)的控制。

(3)保持功能:當(dāng)S=0且R=0時(shí),RS觸發(fā)器的輸出端Q將保持當(dāng)前狀態(tài)不變,實(shí)現(xiàn)數(shù)據(jù)的保持。

三、D觸發(fā)器與RS觸發(fā)器在數(shù)字電路設(shè)計(jì)中的應(yīng)用

- 寄存器設(shè)計(jì)

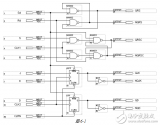

在數(shù)字電路設(shè)計(jì)中,寄存器是一種常見(jiàn)的存儲(chǔ)單元,用于存儲(chǔ)數(shù)據(jù)和指令。D觸發(fā)器和RS觸發(fā)器都可以用于寄存器的設(shè)計(jì)。通過(guò)將多個(gè)D觸發(fā)器或RS觸發(fā)器級(jí)聯(lián),可以實(shí)現(xiàn)多位的數(shù)據(jù)存儲(chǔ)。

- 計(jì)數(shù)器設(shè)計(jì)

計(jì)數(shù)器是一種用于實(shí)現(xiàn)數(shù)字計(jì)數(shù)功能的電路。D觸發(fā)器和RS觸發(fā)器都可以用于計(jì)數(shù)器的設(shè)計(jì)。通過(guò)將多個(gè)D觸發(fā)器或RS觸發(fā)器級(jí)聯(lián),并設(shè)置適當(dāng)?shù)闹梦缓蛷?fù)位邏輯,可以實(shí)現(xiàn)不同進(jìn)制的計(jì)數(shù)器。

- 同步時(shí)序電路設(shè)計(jì)

在同步時(shí)序電路設(shè)計(jì)中,D觸發(fā)器和RS觸發(fā)器都可以用于實(shí)現(xiàn)數(shù)據(jù)的同步傳輸和存儲(chǔ)。通過(guò)合理選擇D觸發(fā)器或RS觸發(fā)器,并設(shè)置適當(dāng)?shù)臅r(shí)鐘信號(hào),可以實(shí)現(xiàn)同步時(shí)序電路的設(shè)計(jì)。

-

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7139瀏覽量

89573 -

存儲(chǔ)

+關(guān)注

關(guān)注

13文章

4353瀏覽量

86169 -

RS觸發(fā)器

+關(guān)注

關(guān)注

3文章

101瀏覽量

18042 -

數(shù)字邏輯電路

+關(guān)注

關(guān)注

0文章

106瀏覽量

15876

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基本RS觸發(fā)器實(shí)驗(yàn)

基本RS觸發(fā)器

不同功能觸發(fā)器的相互轉(zhuǎn)換方法

什么是RS觸發(fā)器,RS觸發(fā)器的工作原理是什么?

觸發(fā)器功能的模擬實(shí)現(xiàn)

RS觸發(fā)器工作原理_RS觸發(fā)器邏輯功能_RS觸發(fā)器和SR觸發(fā)器的區(qū)別

基于CPLD的觸發(fā)器功能的模擬實(shí)現(xiàn)

d與rs觸發(fā)器間功能的轉(zhuǎn)換

d與rs觸發(fā)器間功能的轉(zhuǎn)換

評(píng)論