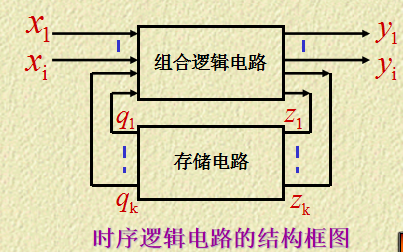

時(shí)序邏輯電路是數(shù)字電路中的一種重要類型,它具有存儲(chǔ)和處理信息的能力。時(shí)序邏輯電路的描述方法有很多種,不同的方法適用于不同的設(shè)計(jì)和分析場(chǎng)景。以下是五種常見的時(shí)序邏輯電路描述方法的介紹:

- 狀態(tài)圖(State Diagram)

狀態(tài)圖是一種圖形化的描述方法,用于表示時(shí)序邏輯電路的狀態(tài)和狀態(tài)之間的轉(zhuǎn)換。狀態(tài)圖由以下元素組成:

- 狀態(tài)(State):表示電路在某一時(shí)刻的狀態(tài),通常用一個(gè)圓圈表示。

- 初始狀態(tài)(Initial State):表示電路開始工作時(shí)的狀態(tài),通常用一個(gè)箭頭指向該狀態(tài)。

- 輸入(Input):影響狀態(tài)轉(zhuǎn)換的信號(hào),通常用箭頭旁邊的文字表示。

- 狀態(tài)轉(zhuǎn)換(State Transition):表示從一個(gè)狀態(tài)到另一個(gè)狀態(tài)的過程,通常用帶箭頭的線段表示。

- 輸出(Output):根據(jù)當(dāng)前狀態(tài)和輸入信號(hào)產(chǎn)生的結(jié)果,通常用圓圈旁邊的文字表示。

狀態(tài)圖的優(yōu)點(diǎn)是直觀、易于理解,適用于設(shè)計(jì)和分析簡(jiǎn)單的時(shí)序邏輯電路。但是,對(duì)于復(fù)雜的電路,狀態(tài)圖可能會(huì)變得非常龐大和難以管理。

- 狀態(tài)表(State Table)

狀態(tài)表是一種表格化的描述方法,用于詳細(xì)列出時(shí)序邏輯電路的所有狀態(tài)和狀態(tài)轉(zhuǎn)換。狀態(tài)表通常包括以下幾列:

- 當(dāng)前狀態(tài)(Current State):表示電路在某一時(shí)刻的狀態(tài)。

- 輸入(Input):影響狀態(tài)轉(zhuǎn)換的信號(hào)。

- 下一狀態(tài)(Next State):根據(jù)當(dāng)前狀態(tài)和輸入信號(hào),電路將轉(zhuǎn)換到的狀態(tài)。

- 輸出(Output):根據(jù)當(dāng)前狀態(tài)和輸入信號(hào)產(chǎn)生的結(jié)果。

狀態(tài)表的優(yōu)點(diǎn)是信息全面、易于查找,適用于設(shè)計(jì)和分析中等復(fù)雜度的時(shí)序邏輯電路。但是,對(duì)于非常復(fù)雜的電路,狀態(tài)表可能會(huì)變得非常冗長(zhǎng)。

- 有限狀態(tài)機(jī)(Finite State Machine, FSM)

有限狀態(tài)機(jī)是一種數(shù)學(xué)模型,用于描述和分析時(shí)序邏輯電路。有限狀態(tài)機(jī)由以下元素組成:

- 狀態(tài)(State):表示電路在某一時(shí)刻的狀態(tài),可以是有限的或無限的。

- 輸入(Input):影響狀態(tài)轉(zhuǎn)換的信號(hào)。

- 狀態(tài)轉(zhuǎn)換函數(shù)(State Transition Function):根據(jù)當(dāng)前狀態(tài)和輸入信號(hào),確定電路將轉(zhuǎn)換到的狀態(tài)。

- 輸出函數(shù)(Output Function):根據(jù)當(dāng)前狀態(tài)和輸入信號(hào),確定電路產(chǎn)生的結(jié)果。

有限狀態(tài)機(jī)的優(yōu)點(diǎn)是具有嚴(yán)格的數(shù)學(xué)基礎(chǔ),適用于設(shè)計(jì)和分析復(fù)雜的時(shí)序邏輯電路。但是,有限狀態(tài)機(jī)的描述和實(shí)現(xiàn)可能比較復(fù)雜。

- 邏輯表達(dá)式(Logic Expression)

邏輯表達(dá)式是一種代數(shù)化的描述方法,用于表示時(shí)序邏輯電路的狀態(tài)和狀態(tài)轉(zhuǎn)換。邏輯表達(dá)式通常包括以下幾種類型:

- 狀態(tài)方程(State Equation):表示狀態(tài)之間的關(guān)系,通常用邏輯門和邏輯運(yùn)算符表示。

- 輸出方程(Output Equation):表示狀態(tài)和輸入信號(hào)與輸出之間的關(guān)系,通常用邏輯門和邏輯運(yùn)算符表示。

邏輯表達(dá)式的優(yōu)點(diǎn)是簡(jiǎn)潔、易于實(shí)現(xiàn),適用于設(shè)計(jì)和分析簡(jiǎn)單的時(shí)序邏輯電路。但是,對(duì)于復(fù)雜的電路,邏輯表達(dá)式可能會(huì)變得非常復(fù)雜。

- 硬件描述語言(Hardware Description Language, HDL)

硬件描述語言是一種用于設(shè)計(jì)和描述數(shù)字電路的編程語言。常見的硬件描述語言有VHDL和Verilog。硬件描述語言具有以下特點(diǎn):

- 抽象級(jí)別:硬件描述語言提供了不同的抽象級(jí)別,如行為級(jí)、寄存器傳輸級(jí)和門級(jí),以適應(yīng)不同的設(shè)計(jì)需求。

- 模塊化:硬件描述語言支持模塊化設(shè)計(jì),可以將復(fù)雜的電路分解為多個(gè)子模塊,便于管理和重用。

- 仿真和驗(yàn)證:硬件描述語言提供了仿真和驗(yàn)證工具,可以在實(shí)際硬件實(shí)現(xiàn)之前,對(duì)電路的功能和性能進(jìn)行測(cè)試和驗(yàn)證。

硬件描述語言的優(yōu)點(diǎn)是功能強(qiáng)大、靈活性高,適用于設(shè)計(jì)和分析各種復(fù)雜度的時(shí)序邏輯電路。但是,硬件描述語言的學(xué)習(xí)和使用可能需要一定的專業(yè)知識(shí)。

總結(jié):

時(shí)序邏輯電路的五種描述方法各有優(yōu)缺點(diǎn),適用于不同的設(shè)計(jì)和分析場(chǎng)景。狀態(tài)圖和狀態(tài)表適用于直觀、簡(jiǎn)單的電路;有限狀態(tài)機(jī)適用于具有嚴(yán)格數(shù)學(xué)基礎(chǔ)的復(fù)雜電路;邏輯表達(dá)式適用于簡(jiǎn)潔、易于實(shí)現(xiàn)的電路;硬件描述語言適用于功能強(qiáng)大、靈活性高的電路。在實(shí)際應(yīng)用中,可以根據(jù)具體需求和場(chǎng)景選擇合適的描述方法。

-

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1629瀏覽量

80821 -

時(shí)序邏輯電路

+關(guān)注

關(guān)注

2文章

94瀏覽量

16594 -

數(shù)學(xué)模型

+關(guān)注

關(guān)注

0文章

83瀏覽量

11985 -

輸入信號(hào)

+關(guān)注

關(guān)注

0文章

469瀏覽量

12608

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

#硬聲創(chuàng)作季 數(shù)字電子技術(shù)基礎(chǔ):時(shí)序邏輯電路的五種描述方法

同步時(shí)序邏輯電路

異步時(shí)序邏輯電路

時(shí)序邏輯電路分析有幾個(gè)步驟(同步時(shí)序邏輯電路的分析方法)

時(shí)序邏輯電路由什么組成_時(shí)序邏輯電路特點(diǎn)是什么

數(shù)字電路教程之時(shí)序邏輯電路課件的詳細(xì)資料免費(fèi)下載

時(shí)序邏輯電路的分析方法

時(shí)序邏輯電路的五種描述方法

時(shí)序邏輯電路的五種描述方法

評(píng)論