隨著人們對計算性能需求的增加以及數據量的顯著提升,嵌入式領域傳統的微處理器和外設的系統架構設計顯得越來越微不足道,除此之外很多應用還要求系統在滿足相關行業標準的同時還需要具有可靠性和安全性。目前在單一的處理器上同時滿足處理高帶寬數據、執行系統應用程序、響應實時任務請求并滿足行業安全標準似乎很難,因此多核異構處理器架構應運而生。一個多核異構處理系統一般由不同類型的多個單核心或多核心處理器組成,最簡單的形式是由一個多核處理器和GPU組成。

圖1:異構多核處理器的時代已經到來

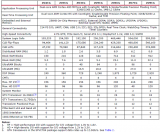

作為行業的領導者Xilinx正在從產品、工具和理念上來推動從傳統可編程邏輯器件向“All Programmable(全可編程)”的轉變。Zynq UltraScale+ MPSoC是Xilinx推出的第二代多處理器SoC器件,采用了16nm FinFET+工藝技術,共分為CG、EG和EV三個系列,都集成了多核應用處理器(四核ARM Cortex-A53應用處理器)、多核圖形處理器(雙核ARM Mali-400圖形處理器)、多核實時處理器(雙核ARM Cortex-R5實時處理器)、平臺管理單元(電源管理、錯誤管理、配置管理以及安全管理)和可編程邏輯資源(高性能計算和豐富I/O擴展等)。與上一代ZYNQ-7000系列相比,其在加密、安全、電源管理和性能方面都得到了顯著的增強。

圖2:傳統系統架構設計向現代一體式整合方式的轉變

傳統的嵌入式系統設計一般都會采用一個或者多個微處理器來實現數據采集、數據處理、人機界面、系統控制等功能,這種方式明顯使得系統變得復雜,需要設計生產多塊PCB板卡,增加系統成本。采用異構多核處理器所有功能都可以用一個處理器來實現,降低了系統PCB設計成本和系統復雜度,但是這對工程師則提出了更高的要求。

對于Zynq UltraScale+ MPSoC的開發,Xilinx為工程師提供了豐富的軟硬件設計工具和參考設計產品組合,Vivado設計工具與NI matlab工具相結合實現IP的抽象設計與自動化,能夠大幅度簡化編程并提高生產,借助SDSoC工具也可以實現整個嵌入式系統的設計,同時讓不會Verilog/VHDL語言的軟件工程師使用邏輯資源為ARM程序加速。

-

Xilinx

+關注

關注

71文章

2171瀏覽量

122145 -

Zynq

+關注

關注

10文章

610瀏覽量

47298 -

MPSoC

+關注

關注

0文章

199瀏覽量

24322

發布評論請先 登錄

相關推薦

Xilinx宣布推出汽車級Zynq UltraScale+ MPSoC系列

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

閑話Zynq UltraScale+ MPSoC(連載1)

Ti推出面向Zynq UltraScale+ MPSoC的電源參考設計

Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞

Zynq UltraScale+ MPSoC的發售消息

詳解Xilinx公司Zynq? UltraScale+?MPSoC產品

米爾科技Zynq UltraScale+ MPSoC技術參考手冊介紹

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

ZYNQ Ultrascale+ MPSoC系列FPGA芯片設計

Zynq UltraScale+ MPSoC的隔離設計示例

適用于Xilinx Zynq UltraScale+ MPSoC應用的電源參考設計

Xilinx Zynq UltraScale+ MPSoC多核異構架構設計詳解

Xilinx Zynq UltraScale+ MPSoC多核異構架構設計詳解

評論