新一代FPGA中采用的基本都是AXI4總線協(xié)議,例如與slaver側(cè)的DMA或DDR等通信。這篇講AXI4的文章感覺(jué)講的很清楚。

0.緒論AXI是高級(jí)擴(kuò)展接口,在AMBA3.0中提出,AMBA4.0將其修改升級(jí)為AXI4.0。AMBA4.0 包括AXI4.0、AXI4.0-lite、ACE4.0、AXI4.0-stream

AXI4.0-lite是AXI的簡(jiǎn)化版本,ACE4.0 是AXI緩存一致性擴(kuò)展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA進(jìn)行以數(shù)據(jù)為主導(dǎo)的大量數(shù)據(jù)的傳輸應(yīng)用。

1.簡(jiǎn)介

1.1 關(guān)于AXI協(xié)議

AMBA AXI協(xié)議支持支持高性能、高頻率系統(tǒng)設(shè)計(jì)。

關(guān)鍵特點(diǎn):

-

適合高帶寬低延時(shí)設(shè)計(jì)

-

無(wú)需復(fù)雜的橋就能實(shí)現(xiàn)高頻操作

-

能滿足大部分器件的接口要求

-

適合高初始延時(shí)的存儲(chǔ)控制器

-

提供互聯(lián)架構(gòu)的靈活性與獨(dú)立性

-

向下兼容已有的AHB和APB接口

-

分離的地址/控制、數(shù)據(jù)相位

-

使用字節(jié)線來(lái)支持非對(duì)齊的數(shù)據(jù)傳輸

-

使用基于burst的傳輸,只需傳輸首地址

-

分離的讀、寫(xiě)數(shù)據(jù)通道,能提供低功耗DMA

-

支持多種尋址方式

-

支持亂序傳輸

-

允許容易的添加寄存器級(jí)來(lái)進(jìn)行時(shí)序收斂

1.2 AXI架構(gòu)

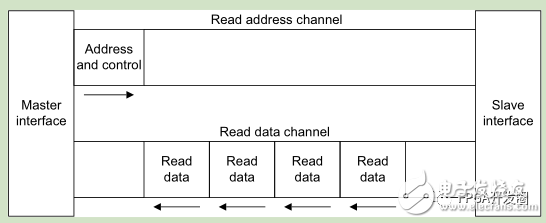

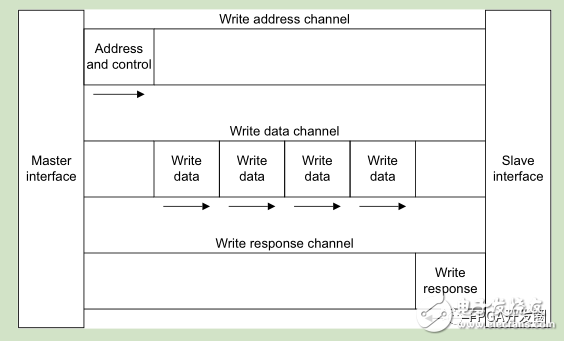

AXI協(xié)議是基于burst的傳輸,并且定義了以下5個(gè)獨(dú)立的傳輸通道:讀地址通道、讀數(shù)據(jù)通道、寫(xiě)地址通道、寫(xiě)數(shù)據(jù)通道、寫(xiě)響應(yīng)通道。

地址通道攜帶控制消息用于描述被傳輸?shù)臄?shù)據(jù)屬性,數(shù)據(jù)傳輸使用寫(xiě)通道來(lái)實(shí)現(xiàn)“主”到“從”的傳輸,“從”使用寫(xiě)響應(yīng)通道來(lái)完成一次寫(xiě)傳輸;讀通道用來(lái)實(shí)現(xiàn)數(shù)據(jù)從“從”到“主”的傳輸。

圖 1-1 讀架構(gòu)

圖 1-2 寫(xiě)架構(gòu)

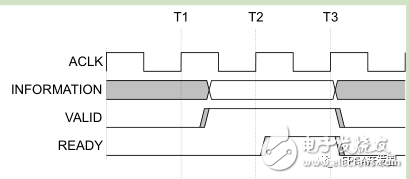

AXI是基于VALID/READY的握手機(jī)制數(shù)據(jù)傳輸協(xié)議,傳輸源端使用VALID表明地址/控制信號(hào)、數(shù)據(jù)是有效的,目的端使用READY表明自己能夠接受信息。

讀/寫(xiě)地址通道:讀、寫(xiě)傳輸每個(gè)都有自己的地址通道,對(duì)應(yīng)的地址通道承載著對(duì)應(yīng)傳輸?shù)牡刂房刂菩畔ⅰ?/span>

讀數(shù)據(jù)通道:讀數(shù)據(jù)通道承載著讀數(shù)據(jù)和讀響應(yīng)信號(hào)包括數(shù)據(jù)總線(8/16/32/64/128/256/512/1024bit)和指示讀傳輸完成的讀響應(yīng)信號(hào)。

寫(xiě)數(shù)據(jù)通道:寫(xiě)數(shù)據(jù)通道的數(shù)據(jù)信息被認(rèn)為是緩沖(buffered)了的,“主”無(wú)需等待“從”對(duì)上次寫(xiě)傳輸?shù)拇_認(rèn)即可發(fā)起一次新的寫(xiě)傳輸。寫(xiě)通道包括數(shù)據(jù)總線(8/16…1024bit)和字節(jié)線(用于指示8bit 數(shù)據(jù)信號(hào)的有效性)。

寫(xiě)響應(yīng)通道:“從”使用寫(xiě)響應(yīng)通道對(duì)寫(xiě)傳輸進(jìn)行響應(yīng)。所有的寫(xiě)傳輸需要寫(xiě)響應(yīng)通道的完成信號(hào)。

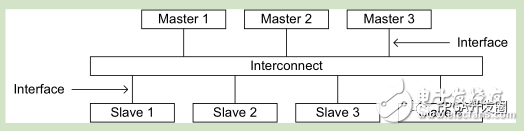

圖 1-3 接口與互聯(lián)

AXI協(xié)議提供單一的接口定義,能用在下述三種接口之間:master/interconnect、slave/interconnect、master/slave。

可以使用以下幾種典型的系統(tǒng)拓?fù)浼軜?gòu):

-

共享地址與數(shù)據(jù)總線

-

共享地址總線,多數(shù)據(jù)總線

-

multilayer多層,多地址總線,多數(shù)據(jù)總線

在大多數(shù)系統(tǒng)中,地址通道的帶寬要求沒(méi)有數(shù)據(jù)通道高,因此可以使用共享地址總線,多數(shù)據(jù)總線結(jié)構(gòu)來(lái)對(duì)系統(tǒng)性能和互聯(lián)復(fù)雜度進(jìn)行平衡。

寄存器片(Register Slices):

每個(gè)AXI通道使用單一方向傳輸信息,并且各個(gè)通道直接沒(méi)有任何固定關(guān)系。因此可以可以在任何通道任何點(diǎn)插入寄存器片,當(dāng)然這會(huì)導(dǎo)致額外的周期延遲。

使用寄存器片可以實(shí)現(xiàn)周期延遲(cycles of latency)和最大操作頻率的折中;使用寄存器片可以分割低速外設(shè)的長(zhǎng)路徑。

2.信號(hào)描述

表 2-1 全局信號(hào)

|

信號(hào)名 |

源 |

描述 |

|

ACLK |

全局時(shí)鐘信號(hào) |

|

|

ARESETn |

復(fù)位源 |

全局復(fù)位信號(hào),低有效 |

表 2-2 寫(xiě)地址通道信號(hào)

|

信號(hào)名 |

源 |

描述 |

|

AWID |

主機(jī) |

寫(xiě)地址ID,用來(lái)標(biāo)志一組寫(xiě)信號(hào) |

|

AWADDR |

主機(jī) |

寫(xiě)地址,給出一次寫(xiě)突發(fā)傳輸?shù)膶?xiě)地址 |

|

AWLEN |

主機(jī) |

突發(fā)長(zhǎng)度,給出突發(fā)傳輸?shù)拇螖?shù) |

|

AWSIZE |

主機(jī) |

突發(fā)大小,給出每次突發(fā)傳輸?shù)淖止?jié)數(shù) |

|

AWBURST |

主機(jī) |

突發(fā)類型 |

|

AWLOCK |

主機(jī) |

總線鎖信號(hào),可提供操作的原子性 |

|

AWCACHE |

主機(jī) |

內(nèi)存類型,表明一次傳輸是怎樣通過(guò)系統(tǒng)的 |

|

AWPROT |

主機(jī) |

保護(hù)類型,表明一次傳輸?shù)奶貦?quán)級(jí)及安全等級(jí) |

|

AWQOS |

主機(jī) |

質(zhì)量服務(wù)QoS |

|

AWREGION |

主機(jī) |

區(qū)域標(biāo)志,能實(shí)現(xiàn)單一物理接口對(duì)應(yīng)的多個(gè)邏輯接口 |

|

AWUSER |

主機(jī) |

用戶自定義信號(hào) |

|

AWVALID |

主機(jī) |

有效信號(hào),表明此通道的地址控制信號(hào)有效 |

|

AWREADY |

從機(jī) |

表明“從”可以接收地址和對(duì)應(yīng)的控制信號(hào) |

表 2-3 寫(xiě)數(shù)據(jù)通道信號(hào)

|

信號(hào)名 |

源 |

描述 |

|

WID |

主機(jī) |

一次寫(xiě)傳輸?shù)腎D tag |

|

WDATA |

主機(jī) |

寫(xiě)數(shù)據(jù) |

|

WSTRB |

主機(jī) |

寫(xiě)數(shù)據(jù)有效的字節(jié)線,用來(lái)表明哪8bits數(shù)據(jù)是有效的 |

|

WLAST |

主機(jī) |

表明此次傳輸是最后一個(gè)突發(fā)傳輸 |

|

WUSER |

主機(jī) |

用戶自定義信號(hào) |

|

WVALID |

主機(jī) |

寫(xiě)有效,表明此次寫(xiě)有效 |

|

WREADY |

從機(jī) |

表明從機(jī)可以接收寫(xiě)數(shù)據(jù) |

表 2-4 寫(xiě)響應(yīng)通道信號(hào)

|

信號(hào)名 |

源 |

描述 |

|

BID |

從機(jī) |

寫(xiě)響應(yīng)ID tag |

|

BRESP |

從機(jī) |

寫(xiě)響應(yīng),表明寫(xiě)傳輸?shù)臓顟B(tài) |

|

BUSER |

從機(jī) |

用戶自定義 |

|

BVALID |

從機(jī) |

寫(xiě)響應(yīng)有效 |

|

BREADY |

主機(jī) |

表明主機(jī)能夠接收寫(xiě)響應(yīng) |

表 2-5 讀地址通道信號(hào)

|

信號(hào)名 |

源 |

描述 |

|

ARID |

主機(jī) |

讀地址ID,用來(lái)標(biāo)志一組寫(xiě)信號(hào) |

|

ARADDR |

主機(jī) |

讀地址,給出一次寫(xiě)突發(fā)傳輸?shù)淖x地址 |

|

ARLEN |

主機(jī) |

突發(fā)長(zhǎng)度,給出突發(fā)傳輸?shù)拇螖?shù) |

|

ARSIZE |

主機(jī) |

突發(fā)大小,給出每次突發(fā)傳輸?shù)淖止?jié)數(shù) |

|

ARBURST |

主機(jī) |

突發(fā)類型 |

|

ARLOCK |

主機(jī) |

總線鎖信號(hào),可提供操作的原子性 |

|

ARCACHE |

主機(jī) |

內(nèi)存類型,表明一次傳輸是怎樣通過(guò)系統(tǒng)的 |

|

ARPROT |

主機(jī) |

保護(hù)類型,表明一次傳輸?shù)奶貦?quán)級(jí)及安全等級(jí) |

|

ARQOS |

主機(jī) |

質(zhì)量服務(wù)QoS |

|

ARREGION |

主機(jī) |

區(qū)域標(biāo)志,能實(shí)現(xiàn)單一物理接口對(duì)應(yīng)的多個(gè)邏輯接口 |

|

ARUSER |

主機(jī) |

用戶自定義信號(hào) |

|

ARVALID |

主機(jī) |

有效信號(hào),表明此通道的地址控制信號(hào)有效 |

|

ARREADY |

從機(jī) |

表明“從”可以接收地址和對(duì)應(yīng)的控制信號(hào) |

表 2-6 讀數(shù)據(jù)通道信號(hào)

|

信號(hào)名 |

源 |

描述 |

|

RID |

從機(jī) |

讀ID tag |

|

RDATA |

從機(jī) |

讀數(shù)據(jù) |

|

RRESP |

從機(jī) |

讀響應(yīng),表明讀傳輸?shù)臓顟B(tài) |

|

RLAST |

從機(jī) |

表明讀突發(fā)的最后一次傳輸 |

|

RUSER |

從機(jī) |

用戶自定義 |

|

RVALID |

從機(jī) |

表明此通道信號(hào)有效 |

|

RREADY |

主機(jī) |

表明主機(jī)能夠接收讀數(shù)據(jù)和響應(yīng)信息 |

表 2-7 低功耗接口信號(hào)

|

信號(hào)名 |

源 |

描述 |

|

CSYSREQ |

時(shí)鐘控制器 |

系統(tǒng)退出低功耗請(qǐng)求,此信號(hào)從“時(shí)鐘控制器”到“外設(shè)” |

|

CSYSACK |

外設(shè) |

退出低功耗狀態(tài)確認(rèn) |

|

CACTIVE |

外設(shè) |

外設(shè)請(qǐng)求時(shí)鐘有效 |

3.信號(hào)接口要求

3.1時(shí)鐘復(fù)位

時(shí)鐘

每個(gè)AXI組件使用一個(gè)時(shí)鐘信號(hào)ACLK,所有輸入信號(hào)在ACLK上升沿采樣,所有輸出信號(hào)必須在ACLK上升沿后發(fā)生。

復(fù)位

AXI使用一個(gè)低電平有效的復(fù)位信號(hào)ARESETn,復(fù)位信號(hào)可以異步斷言,但必須和時(shí)鐘上升沿同步去斷言。

復(fù)位期間對(duì)接口有如下要求:①主機(jī)接口必須驅(qū)動(dòng)ARVALID,AWVALID,WVALID為低電平;②從機(jī)接口必須驅(qū)動(dòng)RVALID,BVALID為低電平;③所有其他信號(hào)可以被驅(qū)動(dòng)到任意值。

在復(fù)位后,主機(jī)可以在時(shí)鐘上升沿驅(qū)動(dòng)ARVALID,AWVALID,WVALID為高電平。

3.2基本讀寫(xiě)傳輸

握手過(guò)程

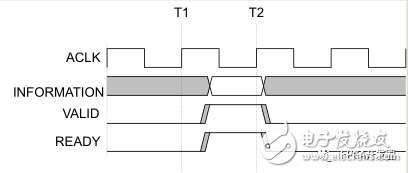

5個(gè)傳輸通道均使用VALID/READY信號(hào)對(duì)傳輸過(guò)程的地址、數(shù)據(jù)、控制信號(hào)進(jìn)行握手。使用雙向握手機(jī)制,傳輸僅僅發(fā)生在VALID、READY同時(shí)有效的時(shí)候。下圖是幾種握手機(jī)制:

圖 3-1 VALID before READY 握手

圖 3-2 READY before VALID 握手

圖 3-3 VALID with READY 握手

通道信號(hào)要求

通道握手信號(hào):每個(gè)通道有自己的xVALID/xREADY握手信號(hào)對(duì)。

寫(xiě)地址通道:當(dāng)主機(jī)驅(qū)動(dòng)有效的地址和控制信號(hào)時(shí),主機(jī)可以斷言AWVALID,一旦斷言,需要保持AWVALID的斷言狀態(tài),直到時(shí)鐘上升沿采樣到從機(jī)的AWREADY。AWREADY默認(rèn)值可高可低,推薦為高(如果為低,一次傳輸至少需要兩個(gè)周期,一個(gè)用來(lái)斷言AWVALID,一個(gè)用來(lái)斷言AWREADY);當(dāng)AWREADY為高時(shí),從機(jī)必須能夠接受提供給它的有效地址。

寫(xiě)數(shù)據(jù)通道:在寫(xiě)突發(fā)傳輸過(guò)程中,主機(jī)只能在它提供有效的寫(xiě)數(shù)據(jù)時(shí)斷言WVALID,一旦斷言,需要保持?jǐn)嘌誀顟B(tài),知道時(shí)鐘上升沿采樣到從機(jī)的WREADY。WREADY默認(rèn)值可以為高,這要求從機(jī)總能夠在單個(gè)周期內(nèi)接受寫(xiě)數(shù)據(jù)。主機(jī)在驅(qū)動(dòng)最后一次寫(xiě)突發(fā)傳輸是需要斷言WLAST信號(hào)。

寫(xiě)響應(yīng)通道:從機(jī)只能它在驅(qū)動(dòng)有效的寫(xiě)響應(yīng)時(shí)斷言BVALID,一旦斷言需要保持,直到時(shí)鐘上升沿采樣到主機(jī)的BREADY信號(hào)。當(dāng)主機(jī)總能在一個(gè)周期內(nèi)接受寫(xiě)響應(yīng)信號(hào)時(shí),可以將BREADY的默認(rèn)值設(shè)為高。

讀地址通道:當(dāng)主機(jī)驅(qū)動(dòng)有效的地址和控制信號(hào)時(shí),主機(jī)可以斷言ARVALID,一旦斷言,需要保持ARVALID的斷言狀態(tài),直到時(shí)鐘上升沿采樣到從機(jī)的ARREADY。ARREADY默認(rèn)值可高可低,推薦為高(如果為低,一次傳輸至少需要兩個(gè)周期,一個(gè)用來(lái)斷言ARVALID,一個(gè)用來(lái)斷言ARREADY);當(dāng)ARREADY為高時(shí),從機(jī)必須能夠接受提供給它的有效地址。

讀數(shù)據(jù)通道:只有當(dāng)從機(jī)驅(qū)動(dòng)有效的讀數(shù)據(jù)時(shí)從機(jī)才可以斷言RVALID,一旦斷言需要保持直到時(shí)鐘上升沿采樣到主機(jī)的BREADY。BREADY默認(rèn)值可以為高,此時(shí)需要主機(jī)任何時(shí)候一旦開(kāi)始讀傳輸就能立馬接受讀數(shù)據(jù)。當(dāng)最后一次突發(fā)讀傳輸時(shí),從機(jī)需要斷言RLAST。

通道間關(guān)系

-

AXI協(xié)議要求通道間滿足如下關(guān)系:

-

寫(xiě)響應(yīng)必須跟隨最后一次burst的的寫(xiě)傳輸

-

讀數(shù)據(jù)必須跟隨數(shù)據(jù)對(duì)應(yīng)的地址

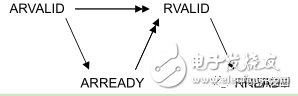

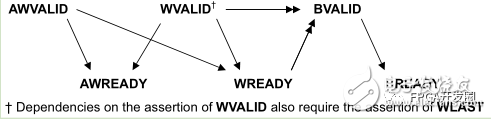

通道握手信號(hào)的依耐關(guān)系

為防止死鎖,通道握手信號(hào)需要遵循一定的依耐關(guān)系。①VALID信號(hào)不能依耐READY信號(hào)。②AXI接口可以等到檢測(cè)到VALID才斷言對(duì)應(yīng)的READY,也可以檢測(cè)到VALID之前就斷言READY。下面有幾個(gè)圖表明依耐關(guān)系,單箭頭指向的信號(hào)能在箭頭起點(diǎn)信號(hào)之前或之后斷言;雙箭頭指向的信號(hào)必須在箭頭起點(diǎn)信號(hào)斷言之后斷言。

圖 3-4 讀傳輸握手依耐關(guān)系

圖 3-5 寫(xiě)傳輸握手依耐關(guān)系

圖 3-6 從機(jī)寫(xiě)響應(yīng)握手依耐關(guān)系

3.3傳輸結(jié)構(gòu)

地址結(jié)構(gòu)

AXI協(xié)議是基于burst的,主機(jī)只給出突發(fā)傳輸?shù)牡谝粋€(gè)字節(jié)的地址,從機(jī)必須計(jì)算突發(fā)傳輸后續(xù)的地址。突發(fā)傳輸不能跨4KB邊界(防止突發(fā)跨越兩個(gè)從機(jī)的邊界,也限制了從機(jī)所需支持的地址自增數(shù))。

1)突發(fā)長(zhǎng)度

ARLEN[7:0]決定讀傳輸?shù)耐话l(fā)長(zhǎng)度,AWLEN[7:0]決定寫(xiě)傳輸?shù)耐话l(fā)長(zhǎng)度。AXI3只支持1~16次的突發(fā)傳輸(Burst_length=AxLEN[3:0]+1),AXI4擴(kuò)展突發(fā)長(zhǎng)度支持INCR突發(fā)類型為1~256次傳輸,對(duì)于其他的傳輸類型依然保持1~16次突發(fā)傳輸(Burst_Length=AxLEN[7:0]+1)。

-

burst傳輸具有如下規(guī)則:

-

wraping burst ,burst長(zhǎng)度必須是2,4,8,16

-

burst不能跨4KB邊界

-

不支持提前終止burst傳輸

所有的組件都不能提前終止一次突發(fā)傳輸。然而,主機(jī)可以通過(guò)解斷言所有的寫(xiě)的strobes來(lái)使非所有的寫(xiě)字節(jié)來(lái)減少寫(xiě)傳輸?shù)臄?shù)量。讀burst中,主機(jī)可以忽略后續(xù)的讀數(shù)據(jù)來(lái)減少讀個(gè)數(shù)。也就是說(shuō),不管怎樣,都必須完成所有的burst傳輸。

注:對(duì)于FIFO,忽略后續(xù)讀數(shù)據(jù)可能導(dǎo)致數(shù)據(jù)丟失,必須保證突發(fā)傳輸長(zhǎng)度和要求的數(shù)據(jù)傳輸大小匹配。

突發(fā)大小

ARSIZE[2:0],讀突發(fā)傳輸;AWSIZE[2:0],寫(xiě)突發(fā)傳輸。

AxSIZE[2:0] bytes in transfer

‘b0001

‘b0012

‘b0104

‘b0118

‘b10016

‘b10132

‘b11064

‘b111128

突發(fā)類型

FIXED:突發(fā)傳輸過(guò)程中地址固定,用于FIFO訪問(wèn)

INCR:增量突發(fā),傳輸過(guò)程中,地址遞增。增加量取決AxSIZE的值。

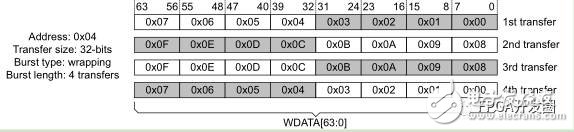

WRAP:回環(huán)突發(fā),和增量突發(fā)類似,但會(huì)在特定高地址的邊界處回到低地址處。回環(huán)突發(fā)的長(zhǎng)度只能是2,4,8,16次傳輸,傳輸首地址和每次傳輸?shù)拇笮?duì)齊。最低的地址整個(gè)傳輸?shù)臄?shù)據(jù)大小對(duì)齊。回環(huán)邊界等于(AxSIZE*AxLEN)。

AxBURST[1:0]burst type

‘b00FIXED

‘b01INCR

‘b10WRAP

‘b11Reserved

Start_Address=AxADDR

Number_Bytes=2^AxSIZE

Burst_Length=AxLEN+1

Aligned_Addr=(INT(Start_Address/Number_Bytes))xNumber_Bytes。//INT表示向下取整。

對(duì)于INCR突發(fā)和WRAP突發(fā)但沒(méi)有到達(dá)回環(huán)邊界,地址由下述方程決定:

Address_N=Aligned_Address+(N-1)xNumber_Bytes

WRAP突發(fā),突發(fā)邊界:

Wrap_Boundary=(INT(Start_Address/(Number_Bytes x Burst_Length)))x(Number_Bytes x Burst_Length)

數(shù)據(jù)讀寫(xiě)結(jié)構(gòu)

WSTRB[n:0]對(duì)應(yīng)于對(duì)應(yīng)的寫(xiě)字節(jié),WSTRB[n]對(duì)應(yīng)WDATA[8n+7:8n]。WVALID為低時(shí),WSTRB可以為任意值,WVALID為高時(shí),WSTRB為高的字節(jié)線必須指示有效的數(shù)據(jù)。

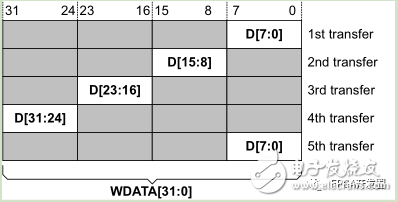

窄傳輸

當(dāng)主機(jī)產(chǎn)生比它數(shù)據(jù)總線要窄的傳輸時(shí),由地址和控制信號(hào)決定哪個(gè)字節(jié)被傳輸:

INCR和WRAP,不同的字節(jié)線決定每次burst傳輸?shù)臄?shù)據(jù),F(xiàn)IXED,每次傳輸使用相同的字節(jié)線。

下圖給出了5次突發(fā)傳輸,起始地址為0,每次傳輸為8bit,數(shù)據(jù)總線為32bit,突發(fā)類型為INCR。

圖 3-7 窄傳輸示例1

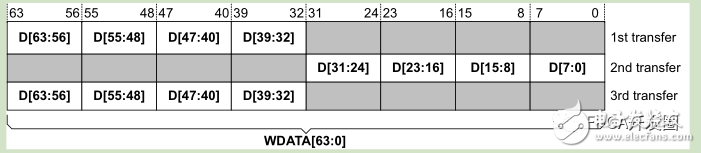

下圖給出3次突發(fā),起始地址為4,每次傳輸32bit,數(shù)據(jù)總線為64bit。

圖 3-8 窄傳輸示例2

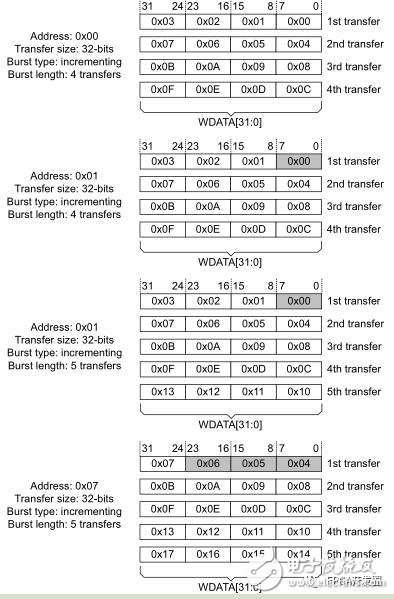

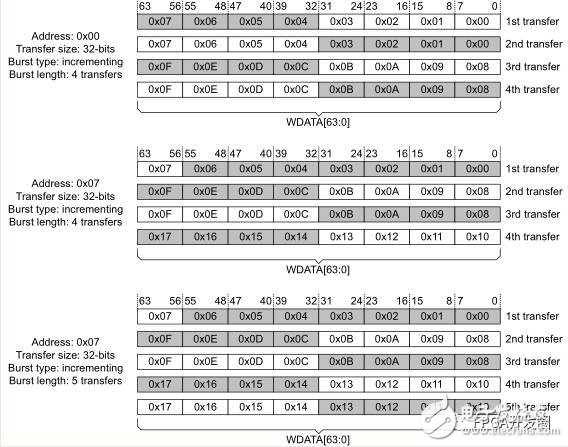

非對(duì)齊傳輸

AXI支持非對(duì)齊傳輸。在大于一個(gè)字節(jié)的傳輸中,第一個(gè)自己的傳輸可能是非對(duì)齊的。如32-bit數(shù)據(jù)包起始地址在0x1002,非32bit對(duì)齊。

主機(jī)可以①使用低位地址線來(lái)表示非對(duì)齊的起始地址;②提供對(duì)齊的起始地址,使用字節(jié)線來(lái)表示非對(duì)齊的起始地址。

圖 3-9 對(duì)齊非對(duì)齊傳輸示例1-32bit總線

圖 3-10 對(duì)齊非對(duì)齊傳輸示例2-64bit總線

圖 3-11 對(duì)齊的回環(huán)傳輸示例

讀寫(xiě)響應(yīng)結(jié)構(gòu)

讀傳輸?shù)捻憫?yīng)信息是附加在讀數(shù)據(jù)通道上的,寫(xiě)傳輸?shù)捻憫?yīng)在寫(xiě)響應(yīng)通道。

RRESP[1:0],讀傳輸

BRESP[1:0],寫(xiě)傳輸

OKAY(‘b00):正常訪問(wèn)成功

EXOKAY(‘b01):Exclusive 訪問(wèn)成功

SLVERR(‘b10):從機(jī)錯(cuò)誤。表明訪問(wèn)已經(jīng)成功到了從機(jī),但從機(jī)希望返回一個(gè)錯(cuò)誤的情況給主機(jī)。

DECERR(‘b11):譯碼錯(cuò)誤。一般由互聯(lián)組件給出,表明沒(méi)有對(duì)應(yīng)的從機(jī)地址。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605989 -

總線協(xié)議

+關(guān)注

關(guān)注

0文章

117瀏覽量

14899

原文標(biāo)題:AXI4總線協(xié)議

文章出處:【微信號(hào):FPGA-EETrend,微信公眾號(hào):FPGA開(kāi)發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

請(qǐng)問(wèn)microblaze如何通過(guò)串口讀寫(xiě)FPGA內(nèi)部axi4總線上的寄存器?

看看在SpinalHDL中AXI4總線互聯(lián)IP的設(shè)計(jì)

AXI4接口協(xié)議的基礎(chǔ)知識(shí)

ZYNQ中DMA與AXI4總線

深入AXI4總線一握手機(jī)制

深入 AXI4總線 (四):RAM 讀取實(shí)戰(zhàn)

AXI4 、 AXI4-Lite 、AXI4-Stream接口

AXI4協(xié)議五個(gè)不同通道的握手機(jī)制

FPGA AXI4協(xié)議學(xué)習(xí)筆記(二)

FPGA AXI4協(xié)議學(xué)習(xí)筆記(三)

AXI4-Lite協(xié)議簡(jiǎn)明學(xué)習(xí)筆記

Xilinx FPGA AXI4總線(一)介紹【AXI4】【AXI4-Lite】【AXI-Stream】

漫談AMBA總線-AXI4協(xié)議的基本介紹

SoC設(shè)計(jì)中總線協(xié)議AXI4與AXI3的主要區(qū)別詳解

一篇文章讀懂讀透FPGA AXI4 總線協(xié)議

一篇文章讀懂讀透FPGA AXI4 總線協(xié)議

評(píng)論