高速緩沖存儲(chǔ)器(Cache)的工作原理,是基于計(jì)算機(jī)程序和數(shù)據(jù)訪問的局部性原理,即程序在執(zhí)行過程中,對(duì)數(shù)據(jù)的訪問往往呈現(xiàn)出時(shí)間和空間的局部性。具體來說,就是程序在某一時(shí)間段內(nèi),會(huì)集中訪問某一小塊內(nèi)存區(qū)域;同時(shí),在訪問了某個(gè)存儲(chǔ)位置的數(shù)據(jù)后,不久后可能會(huì)再次訪問該位置或其附近位置的數(shù)據(jù)。基于這一原理,高速緩沖存儲(chǔ)器通過存儲(chǔ)CPU近期可能訪問的數(shù)據(jù)和指令,來減少對(duì)內(nèi)存的訪問次數(shù),從而提高CPU的運(yùn)行效率。

一、高速緩沖存儲(chǔ)器的基本組成

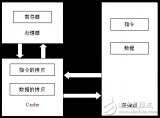

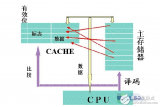

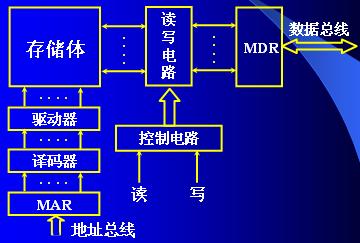

高速緩沖存儲(chǔ)器通常由高速存儲(chǔ)器、聯(lián)想存儲(chǔ)器、替換邏輯電路和相應(yīng)的控制線路組成。這些組件協(xié)同工作,實(shí)現(xiàn)了對(duì)CPU訪問請(qǐng)求的快速響應(yīng)和數(shù)據(jù)的高效存儲(chǔ)。

- 高速存儲(chǔ)器 :這是Cache的主體部分,采用SRAM技術(shù),具有高速存取的特點(diǎn)。高速存儲(chǔ)器被劃分為多個(gè)行和列的存儲(chǔ)單元組,以存儲(chǔ)CPU可能訪問的數(shù)據(jù)和指令。

- 聯(lián)想存儲(chǔ)器 :用于地址聯(lián)想,其存儲(chǔ)單元與高速存儲(chǔ)器具有相同的行數(shù)和列數(shù)。當(dāng)主存儲(chǔ)器中的某個(gè)數(shù)據(jù)塊被調(diào)入高速存儲(chǔ)器時(shí),聯(lián)想存儲(chǔ)器會(huì)記錄該數(shù)據(jù)塊在主存儲(chǔ)器中的位置信息,以便后續(xù)快速定位。

- 替換邏輯電路 :當(dāng)高速存儲(chǔ)器中沒有足夠的空間存儲(chǔ)新的數(shù)據(jù)塊時(shí),替換邏輯電路會(huì)根據(jù)一定的替換算法(如LRU、FIFO、RAND等),選擇并淘汰某個(gè)舊的數(shù)據(jù)塊,以騰出空間存放新調(diào)入的數(shù)據(jù)塊。

- 控制線路 :負(fù)責(zé)協(xié)調(diào)高速緩沖存儲(chǔ)器與其他計(jì)算機(jī)部件(如CPU、內(nèi)存)之間的數(shù)據(jù)交換和指令執(zhí)行。

二、高速緩沖存儲(chǔ)器的工作原理

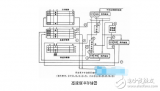

當(dāng)CPU需要訪問某個(gè)地址的數(shù)據(jù)時(shí),高速緩沖存儲(chǔ)器的工作流程大致如下:

- 地址解析 :CPU發(fā)出訪問請(qǐng)求,并提供要訪問的內(nèi)存地址。高速緩沖存儲(chǔ)器首先對(duì)該地址進(jìn)行解析,將其劃分為行號(hào)、列號(hào)和組內(nèi)地址三個(gè)字段。

- 查找高速存儲(chǔ)器 :根據(jù)解析后的地址信息,高速緩沖存儲(chǔ)器在高速存儲(chǔ)器中查找相應(yīng)的數(shù)據(jù)塊。如果找到(即命中),則直接從高速存儲(chǔ)器中讀取數(shù)據(jù)并返回給CPU;如果未找到(即未命中),則需要進(jìn)行下一步操作。

- 訪問內(nèi)存 :當(dāng)高速存儲(chǔ)器中未命中時(shí),高速緩沖存儲(chǔ)器會(huì)向內(nèi)存發(fā)出訪問請(qǐng)求,從內(nèi)存中讀取所需的數(shù)據(jù)塊,并將其存入高速存儲(chǔ)器中相應(yīng)的位置。同時(shí),聯(lián)想存儲(chǔ)器也會(huì)記錄該數(shù)據(jù)塊在主存儲(chǔ)器中的位置信息。

- 數(shù)據(jù)返回 :從內(nèi)存中讀取的數(shù)據(jù)塊被存入高速存儲(chǔ)器后,高速緩沖存儲(chǔ)器會(huì)將其返回給CPU,以滿足CPU的訪問請(qǐng)求。

- 替換操作 (如需要):如果高速存儲(chǔ)器中沒有足夠的空間存儲(chǔ)新的數(shù)據(jù)塊,替換邏輯電路會(huì)根據(jù)替換算法選擇并淘汰某個(gè)舊的數(shù)據(jù)塊,以騰出空間存放新調(diào)入的數(shù)據(jù)塊。

三、高速緩沖存儲(chǔ)器的優(yōu)勢(shì)與挑戰(zhàn)

優(yōu)勢(shì):

- 提高CPU訪問速度 :通過存儲(chǔ)CPU近期可能訪問的數(shù)據(jù)和指令,高速緩沖存儲(chǔ)器顯著減少了CPU對(duì)內(nèi)存的訪問次數(shù),從而提高了CPU的運(yùn)行效率。

- 緩解內(nèi)存帶寬壓力 :由于CPU可以直接從高速緩沖存儲(chǔ)器中讀取數(shù)據(jù)和指令,因此減少了對(duì)內(nèi)存帶寬的需求,緩解了內(nèi)存帶寬的壓力。

- 降低能耗 :由于減少了CPU對(duì)內(nèi)存的訪問次數(shù),因此也降低了系統(tǒng)的整體能耗。

挑戰(zhàn):

- 容量與速度的平衡 :高速緩沖存儲(chǔ)器的容量相對(duì)較小,但其速度卻遠(yuǎn)高于內(nèi)存。如何在保證速度的同時(shí)盡可能提高容量,是高速緩沖存儲(chǔ)器設(shè)計(jì)中的一個(gè)重要挑戰(zhàn)。

- 替換算法的優(yōu)化 :替換算法的選擇對(duì)高速緩沖存儲(chǔ)器的性能有著重要影響。如何設(shè)計(jì)出更加高效、準(zhǔn)確的替換算法,以提高高速緩沖存儲(chǔ)器的命中率和整體性能,是一個(gè)持續(xù)的研究課題。

- 一致性問題 :在寫操作中,如何保持高速緩沖存儲(chǔ)器與內(nèi)存之間數(shù)據(jù)的一致性,是高速緩沖存儲(chǔ)器設(shè)計(jì)中需要解決的一個(gè)重要問題。這通常涉及到復(fù)雜的同步和協(xié)調(diào)機(jī)制。

四、結(jié)論

高速緩沖存儲(chǔ)器作為計(jì)算機(jī)體系結(jié)構(gòu)中的一個(gè)重要組成部分,其工作原理基于程序和數(shù)據(jù)訪問的局部性原理。通過存儲(chǔ)CPU近期可能訪問的數(shù)據(jù)和指令,高速緩沖存儲(chǔ)器顯著提高了CPU的運(yùn)行效率,并緩解了內(nèi)存帶寬的壓力。然而,高速緩沖存儲(chǔ)器的設(shè)計(jì)也面臨著容量與速度的平衡、替換算法的優(yōu)化以及一致性問題等挑戰(zhàn)。隨著計(jì)算機(jī)技術(shù)的不斷發(fā)展,高速緩沖存儲(chǔ)器的性能將會(huì)進(jìn)一步提升,為計(jì)算機(jī)提供更加高效、穩(wěn)定和可靠的數(shù)據(jù)處理能力。

-

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7534瀏覽量

88638 -

內(nèi)存

+關(guān)注

關(guān)注

8文章

3054瀏覽量

74325 -

高速緩沖存儲(chǔ)器

+關(guān)注

關(guān)注

0文章

12瀏覽量

7536

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

中央處理器與高速緩沖存儲(chǔ)器之間的聯(lián)系

高速緩沖存儲(chǔ)器部件結(jié)構(gòu)及原理解析

高速緩沖存儲(chǔ)器的分類及概述

高速緩沖存儲(chǔ)器的作用解析

高速緩沖存儲(chǔ)器的特點(diǎn)解說

高速緩沖存儲(chǔ)器在電腦硬件中的位置分析

高速緩沖存儲(chǔ)器的作用是什么_有什么特點(diǎn)

高速緩沖存儲(chǔ)器基礎(chǔ)知識(shí)詳細(xì)介紹

EE-271: 高速緩沖存儲(chǔ)器在Blackfin?處理器中的應(yīng)用

高速緩沖存儲(chǔ)器有什么作用

高速緩沖存儲(chǔ)器與內(nèi)存的區(qū)別

高速緩沖存儲(chǔ)器是內(nèi)存還是外存,高速緩沖存儲(chǔ)器是為了解決什么

EE-271: 高速緩沖存儲(chǔ)器在Blackfin處理器中的應(yīng)用

高速緩沖存儲(chǔ)器的基本組成和工作原理

高速緩沖存儲(chǔ)器的基本組成和工作原理

評(píng)論