大多數設計者都熟悉基于Pierce(皮爾斯)柵拓撲結構的振蕩器,但很少有人真正了解它是如何工作的,更遑論如何正確的設計。我們經常看到,在振蕩器工作不正常之前,多數人是不愿付出太多精力來關注振蕩器的設計的,而此時產品通常已經量產;許多系統或項目因為它們的晶振無法正常工作而被推遲部署或運行。情況不應該是如此。在設計階段,以及產品量產前的階段,振蕩器應該得到適當的關注。設計者應當避免一場惡夢般的情景:發往外地的產品被大批量地送回來。

本文介紹了Pierce振蕩器的基本知識,并提供一些指導作法來幫助大家如何規劃一個好的振蕩器設計,如何確定不同的外部器件的具體參數以及如何為振蕩器設計一個良好的印刷電路板。

在本文結尾處,有一個簡易的晶振及外圍器件選型指南,其中為MCU推薦了一些晶振型號(針對HSE及LSE),可以幫助大家快速上手。

1、石英晶振的特性及模型 石英晶振的特性及模型

石英晶體是一種可將電能和機械能相互轉化的壓電器件,能量轉變發生在共振頻率點上。它可用如下模型表示:

圖1 石英晶體模型

C 0 :等效電路中與串聯臂并接的電容(譯注:也叫并電容,靜電電容,其值一般僅與晶振的尺寸有關)。

L m :(動態等效電感)代表晶振機械振動的慣性。

C m :(動態等效電容)代表晶振的彈性。

R m :(動態等效電阻)代表電路的損耗。

晶振的阻抗可表示為以下方程(假設R m 可以忽略不計):

其中F s 的是當電抗Z=0時的串聯諧頻率(譯注:它是L m 、C m 和R m 支路的諧振頻率),其表達式如下:

F a 是當電抗Z趨于無窮大時的并聯諧振頻率(譯注:它是整個等效電路的諧振頻率),使用等式

(1),其表達式如下:

在F s 到F a 的區域即通常所謂的:“并聯諧振區”(圖2中的陰影部分),在這一區域晶振工作在并聯諧振狀態(譯注:該區域就是晶振的正常工作區域,F a -F s 就是晶振的帶寬。帶寬越窄,晶振品質因素越高,振蕩頻率越穩定)。在此區域晶振呈電感特性,從而帶來了相當于180 °的相移。

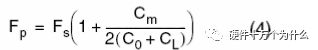

其頻率F P (或者叫F L :負載頻率)表達式如下:

從表達式(4),我們知道可以通過調節負載電容C L 來微調振蕩器的頻率,這就是為什么晶振制造商在其產品說明書中會指定外部負載電容C L 值的原因。通過指定外部負載電容C L 值,可以使晶振晶體振蕩時達到其標稱頻率。

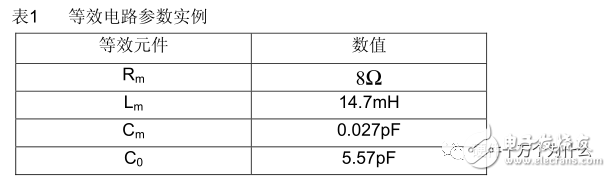

下表給出了一個例子來說明如何調整外部參數來達到晶振電路的8MHz標稱頻率:

使用表達式(2)、(3)和(4),我們可以計算出該晶振的F s 、F a 及F P :

F s = 7988768Hz,F a = 8008102Hz

如果該晶振的C L 為10pF,則其振蕩頻率為:F P = 7995695Hz。

要使其達到準確的標稱振蕩頻率8MHz,C L 應該為4.02pF。

2、振蕩器原理

振蕩器由一個放大器和反饋網絡組成,反饋網絡起到頻率選擇的作用。圖3通過一個框圖來說明振蕩器的基本原理

為了起振,Barkhausen條件必須得到滿足。即閉環增益應大于1,并且總相移為360°。

為了讓振蕩器工作,要保證|A(f)|.|B(f)| >> 1。這意味著開環增益應遠大于1,到達穩定振蕩所需的時間取決于這個開環增益。然而,僅滿足以上條件是不夠解釋為什么晶體振蕩器可以開始振蕩。為了起振,還需要向其提供啟動所需的電能。一般來說,上電的能量瞬變以及噪聲可以提供所需的能量。應當注意到,這個啟動能量應該足夠多,從而能夠保證通過觸發使振蕩器在所需的頻率工作。

實際上,在這種條件下的放大器是非常不穩定的,任何干擾進入這種正反饋閉環系統都會使其不穩定并引發振蕩啟動。干擾可能源于上電,器件禁用/使能的操作以及晶振熱噪聲等...。同時必須注意到,只有在晶振工作頻率范圍內的噪聲才能被放大,這部分相對于噪聲的全部能量來說只是一小部分,這也就是為什么晶體振蕩器需要相當長的時間才能啟動的原因。

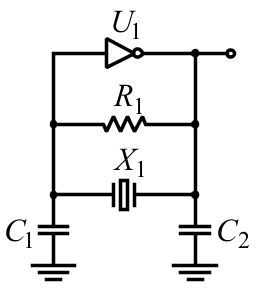

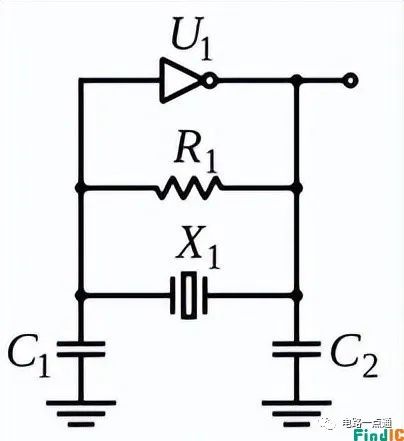

3 Pierce 振蕩器

皮爾斯振蕩器有低功耗、低成本及良好的穩定性等特點,因此常見于通常的應用中。

4 Pierce 振蕩器設計

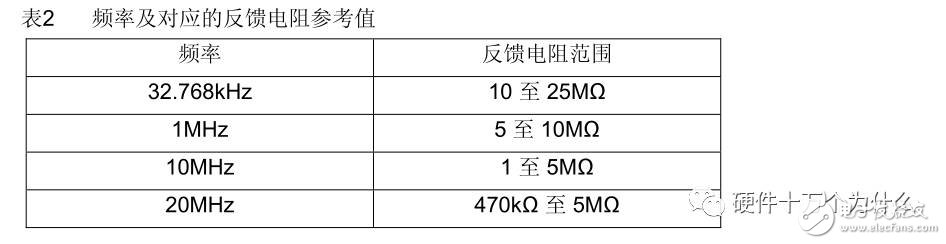

反饋電阻 反饋電阻R F

在大多數情況下,反饋電阻R F 是內嵌在振蕩器電路內的(至少在ST的MCU中是如此)。它的作用是通過引入反饋使反向器的功能等同于放大器。Vin和Vout之間增加的反饋電阻使放大器在Vout= Vin時產生偏置,迫使反向器工作在線性區域(圖5中陰影區)。該放大器放大了晶振的正常工作區域內的在并聯諧振區內的噪聲(例如晶振的熱噪聲)(譯注:工作在線性區的反向器等同于一個反向放大器),從而引發晶振起振。在某些情況下,如果在起振后去掉反饋電阻R F ,振蕩器仍可以繼續正常運轉。

負載電容 負載電容C L

負載電容C L 是指連接到晶振上的終端電容。C L 值取決于外部電容器C L1 和C L2 ,刷電路板上的雜

散電容(C s )。C L 值由由晶振制造商給出。保證振蕩頻率精度,主要取決于振蕩電路的負載電容與

給定的電容值相同,保證振蕩頻率穩定度主要取決于負載電容保持不變。外部電容器C L1 和C L2

可用來調整CL,使之達到晶振制造商的標定值。

即:C L1 = C L2 = 20pF

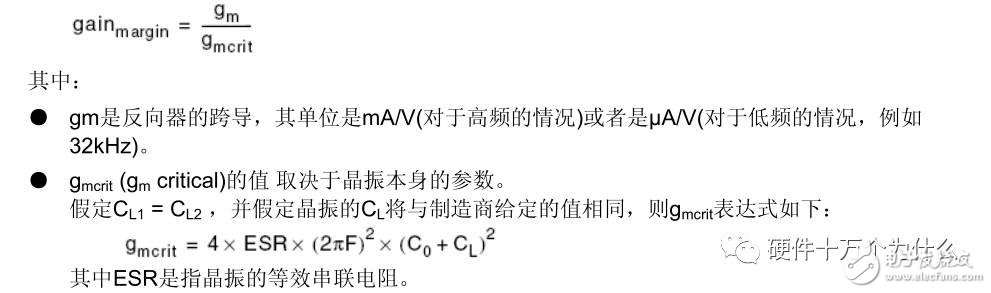

振蕩器的增益裕量

增益裕量是最重要的參數,它決定振蕩器是否能夠正常起振,其表達式如下:

根據Eric Vittoz的理論(譯注:具體可參考Eric A. Vittoz et al., "High-Performance Crystal Oscillator Circuits: Theory and Application", IEEE Journal of Solid-State Circuits, vol. 23, No. 3,pp. 774-782, Jun. 1988),放大器和兩個外部電容的阻抗對晶振的RLC動態等效電路的電抗有補償作用。

基于這一理論,反向器跨導(gm)必須滿足:gm > gmcrit 。在這種情況下才滿足起振的振蕩條件。為保證可靠的起振,增益裕量的最小值一般設為5。

例如,如果設計一個微控制器的振蕩器部分,其gm等于25mA/V。如果所選擇的石英晶振(來自FOX公司)的參數如下:

頻率 = 8MHz,C 0 = 7pF,C L = 10pF,ESR = 80 ?

那么該晶體能否與微控制器配合可靠起振?

如果不能滿足增益裕量起振條件(即增益裕量Gain margin 小于5,晶振無法正常起振),應嘗試選擇一種ESR較低或/和C L 較低的晶振。

5關于PCB的建議

1. 外部雜散電容和電感要控制在一個盡可能小的范圍內,從而避免晶振進入非正常工作模式或引起起振不正常等問題。另外,振蕩器電路旁邊要避免有高頻信號經過。

2. 走線長度越短越好。

3. 接地平面用于信號隔離和減少噪聲。例如:在晶振的保護環(譯注:(Guard ring),指器件或走線外圍成一圈用于屏蔽干擾的導線環,一般要求理論上沒有電流從該導線環上經過)下直接敷地有助于將晶振和來自其他PCB層的噪聲隔離開來。要注意接地平面要緊臨晶振但只限于晶振下面,而不要將此接地平面敷滿整個PCB板(見圖7)。

4. 像圖7所示來布地線是一個好的作法。這種布線方法將振蕩器的輸入與輸出隔離開來,同時也將振蕩器和臨近的電路隔離開來。所有的V SS 過孔不是直接連到地平面上(除晶振焊盤之外),就是連接到終端在C L1 和C L2 下方的地線上。

5. 在每一對V DD 與V SS 端口上連接去藕電容來平滑噪聲。

硬十iBox晶振設計實例:

-

振蕩器

+關注

關注

28文章

3847瀏覽量

139364 -

Pierce振蕩器

+關注

關注

0文章

1瀏覽量

1051 -

振蕩器設計

+關注

關注

0文章

1瀏覽量

1046

原文標題:微控制器振蕩器電路

文章出處:【微信號:Hardware_10W,微信公眾號:硬件十萬個為什么】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

壓控振蕩器vco工作原理是什么

壓控振蕩器的指標有哪些

壓控振蕩器的工作原理是什么

數字振蕩器的相位噪聲是多少

反饋式振蕩器的振蕩平衡條件是什么

高頻振蕩器和低頻振蕩器的區別

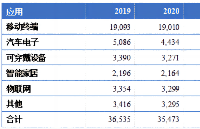

6.晶體和振蕩器 行業研究及十五五規劃分析報告(不同應用晶體和振蕩器分析)

5.晶體和振蕩器 行業研究及十五五規劃分析報告(不同產品類型晶體和振蕩器分析)

如何巧妙運用Pierce振蕩器知識規劃一個好的振蕩器設計?

如何巧妙運用Pierce振蕩器知識規劃一個好的振蕩器設計?

評論