Vivado 2024.1已正式發布,今天我們就來看看新版本帶來了哪些新特性。

Open Dataflow Design

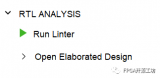

無論是Synthesis階段還是Implementation階段,打開Vivado圖形界面,在導航欄下都能看到新增了一個選項Open Dataflow Design,如下圖所示。這個功能對于我們分析系統的數據流非常有用。

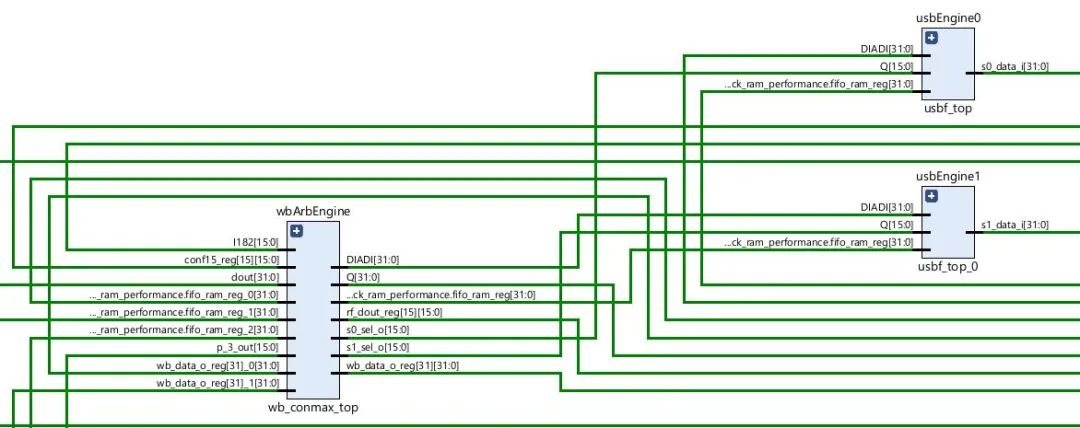

如下圖所示,顯示了一個設計的DFV(DataFlow Viewer)視圖,可以看到DFV只會顯示模塊的輸入/輸出管腳以及和其他模塊的連接關系,進而表征了數據流向,這正是其聚焦點。一些控制信號如時鐘、復位、讀/寫使能以及讀/寫地址等被剔除。這也是其與常規的Schematic視圖的區別。DFV的一個典型應用場景是手工布局:根據互聯程度判定關鍵模塊,進而在畫Pblock時將這些關鍵模塊放置在同一個Pblock內。

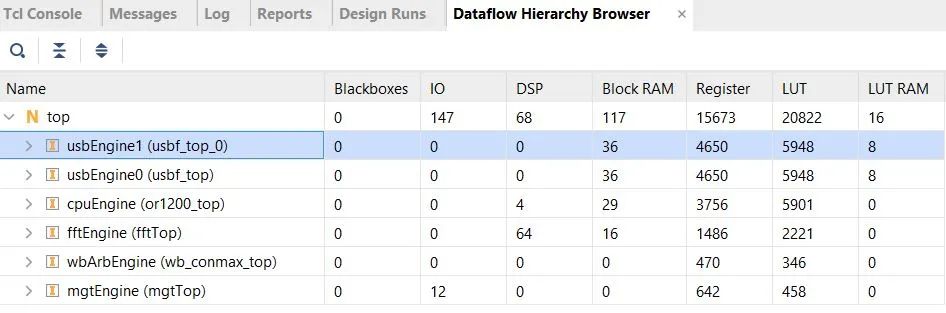

此外,一旦打開DFV視圖,Vivado還會同時給出設計流水的層次化視圖,如下圖所示,便于用戶觀察某個模塊下的數據流。

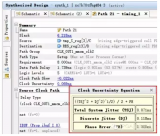

GEN_REPORTS_PARALLEL

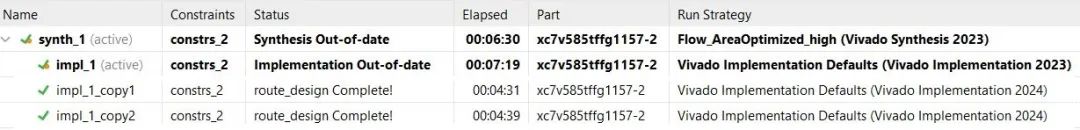

Vivado 2024.1的Implementation Run新增了一個屬性:GEN_REPORTS_PARALLEL,默認情況下該屬性是被勾選上的,如下圖所示。顧名思義,其作用是在Implementation階段并行生成各種報告,從而縮短編譯時間。下圖顯示了用Vivado 2023.2創建的工程Implementation所需的編譯時間(impl_1),將此工程采用2024.1進行編譯,其中impl_1_copy1勾選了GEN_REPORTS_PARALLEL屬性,而impl_1_copy2沒有勾選該屬性,可以看到兩者有8秒的時間差異,同時相比于2023.2,編譯時間縮短了38.26%。

USER_CLOCK_VTREE_TYPE

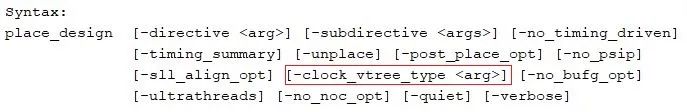

如果目標芯片是Versal SSI芯片,如VP1502或VP1902,該屬性可用于針對設計中的指定時鐘設置時鐘Vtree類型,其可選值有3個,分別為InterSLR、intraSLR和balanced。默認情況下為InterSLR。此外,place_design還專門新增了一個選項-clock_vtree_type,如下圖所示。該選項也有3個可選值,與USER_CLOCK_VTREE_TYPE可選值一致。不同之處在于該選項是全局選項,而USER_CLOCK_VTREE_TYPE是針對指定時鐘。但兩者的目的的相同的,都可改善時鐘偏移(Clock Skew)。

-

design

+關注

關注

0文章

158瀏覽量

45778 -

編譯

+關注

關注

0文章

661瀏覽量

33040 -

Vivado

+關注

關注

19文章

815瀏覽量

66886

原文標題:Vivado 2024.1有哪些新特性?(1)

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

請問我可以免費更新Vivado版本到2016.1嗎?

怎么將vivado12.3更新到最新的15.4版本?

Vivado Design Suite HLx 版本 2016.4 現已發布

Vivado Design Suite 2014.4.1 現已推出!

賽靈思Vivado設計套件推出2013.1版本,提供IP 集成器和高層次綜合功能

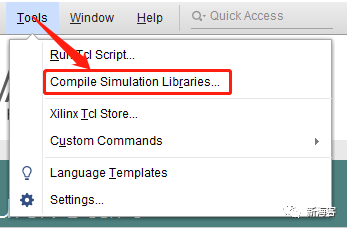

使用Vivado 2017調用Modelsim的詳細步驟

如何使用Vivado 2022.1版本工具鏈實現ZCU102 USB啟動(上)

Vivado Design Suite用戶指南:版本說明、安裝和許可

Vivado2018版本中Modelsim的配置

Vivado 2024.1版本的新特性(1)

Vivado 2024.1版本的新特性(1)

評論