微處理器的執(zhí)行單元(Execution Unit,簡稱EU)是微處理器中負責執(zhí)行指令的核心部分,它集成了多種功能單元,共同協(xié)作完成算術運算、邏輯運算以及指令的譯碼和執(zhí)行等任務。以下是對微處理器執(zhí)行單元的詳細闡述:

一、執(zhí)行單元的基本概述

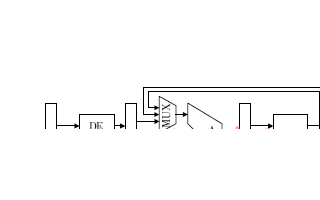

執(zhí)行單元是微處理器中除總線接口單元(Bus Interface Unit,簡稱BIU)之外的另一個重要組成部分。在8086微處理器等經(jīng)典架構(gòu)中,EU和BIU共同協(xié)作,完成指令的讀取、譯碼和執(zhí)行。執(zhí)行單元主要負責指令的實際執(zhí)行,包括算術運算、邏輯運算、指令譯碼等,是微處理器性能的關鍵因素之一。

二、執(zhí)行單元的主要組成部分

執(zhí)行單元通常包括算術邏輯單元(Arithmetic Logic Unit,簡稱ALU)、標志寄存器、暫存器、寄存器組和控制單元等關鍵組成部分。

- 算術邏輯單元(ALU) :

ALU是執(zhí)行單元的核心部件,負責執(zhí)行所有的算術運算(如加、減、乘、除)和邏輯運算(如與、或、非、異或)。ALU接收來自控制單元的指令和數(shù)據(jù),執(zhí)行相應的運算,并將運算結(jié)果存儲到寄存器中供后續(xù)使用。ALU的性能直接決定了微處理器的運算能力。 - 標志寄存器 :

標志寄存器(Flag Register)也稱為程序狀態(tài)字寄存器(Program Status Word Register,簡稱PSW),用于記錄或存放狀態(tài)標志和控制標志信息。這些標志信息包括運算結(jié)果的溢出、符號、零標志等,對于程序的執(zhí)行和條件判斷至關重要。 - 暫存器和寄存器組 :

執(zhí)行單元內(nèi)部包含多個暫存器和寄存器組,用于臨時存儲數(shù)據(jù)和指令。這些寄存器包括通用寄存器(用于存儲運算過程中需要頻繁訪問的數(shù)據(jù))、程序計數(shù)器(PC,用于指示下一條要執(zhí)行的指令的地址)等。寄存器組的設計和優(yōu)化對于提高指令執(zhí)行效率具有重要作用。 - 控制單元 :

雖然控制單元在物理上可能不屬于執(zhí)行單元的一部分,但它在執(zhí)行單元中扮演著至關重要的角色。控制單元負責根據(jù)指令的需求,控制執(zhí)行單元內(nèi)各部件執(zhí)行相應的操作。它根據(jù)指令譯碼結(jié)果,激活相應的控制線路,確保指令能夠正確執(zhí)行。

三、執(zhí)行單元的工作流程

執(zhí)行單元的工作流程通常包括以下幾個步驟:

- 取指 :

在指令周期的開始階段,BIU從內(nèi)存中取出下一條要執(zhí)行的指令,并將其存儲到指令寄存器中。 - 譯碼 :

控制單元對指令進行譯碼,確定指令的類型、操作數(shù)以及需要執(zhí)行的操作。 - 執(zhí)行 :

執(zhí)行單元根據(jù)譯碼結(jié)果,從寄存器組或內(nèi)存中取出操作數(shù),通過ALU等部件執(zhí)行相應的算術或邏輯運算。運算結(jié)果將存儲到寄存器中供后續(xù)使用。 - 寫回 :

如果運算結(jié)果需要寫回到內(nèi)存或寄存器中,執(zhí)行單元將發(fā)送相應的寫回信號,確保數(shù)據(jù)能夠正確存儲。

四、執(zhí)行單元的性能優(yōu)化

為了提高執(zhí)行單元的性能,現(xiàn)代微處理器通常采用多種優(yōu)化技術,包括:

- 指令流水線 :

指令流水線技術通過將指令的執(zhí)行過程分解為多個階段(如取指、譯碼、執(zhí)行、寫回等),并允許不同指令的不同階段并行執(zhí)行,從而顯著提高指令的執(zhí)行效率。 - 分支預測 :

分支預測技術用于預測程序中的分支指令的執(zhí)行路徑,從而提前加載并執(zhí)行預測路徑上的指令。這有助于減少因分支導致的執(zhí)行延遲和性能損失。 - 緩存技術 :

現(xiàn)代微處理器通常采用多級緩存技術來存儲最近訪問的指令和數(shù)據(jù)。緩存的引入可以減少對內(nèi)存的訪問次數(shù),提高指令和數(shù)據(jù)的讀取效率。 - 多核與并行處理 :

為了提高整體性能,現(xiàn)代微處理器普遍采用多核設計,每個核心都包含獨立的執(zhí)行單元。多核處理器可以并行執(zhí)行多個任務,從而顯著提高整體計算性能。

五、總結(jié)

微處理器的執(zhí)行單元是微處理器中負責執(zhí)行指令的核心部分,它集成了算術邏輯單元、標志寄存器、暫存器、寄存器組和控制單元等關鍵組成部分。執(zhí)行單元通過執(zhí)行算術運算、邏輯運算以及指令的譯碼和執(zhí)行等任務,為計算機系統(tǒng)的運行提供強大的支持。隨著科技的不斷進步和應用需求的不斷增長,微處理器的執(zhí)行單元也在不斷優(yōu)化和創(chuàng)新,以滿足更高性能、更低功耗和更強安全性的需求。

-

寄存器

+關注

關注

31文章

5363瀏覽量

121151 -

微處理器

+關注

關注

11文章

2274瀏覽量

82766 -

指令

+關注

關注

1文章

611瀏覽量

35811

發(fā)布評論請先 登錄

相關推薦

TI推出Sitara微處理器單元Sitara微處理器單元AM

TI微處理器介紹

什么是微處理器_微處理器具有什么功能

微處理器的組成

基于FPGA的VLIW微處理器基本功能實現(xiàn)設計

微處理器由什么組成 微處理器和cpu的關系

嵌入式微處理器的原理和應用

主流嵌入式微處理器的結(jié)構(gòu)與原理是什么 常見的嵌入式微處理器類型包括

嵌入式系統(tǒng)的微處理器選擇

微處理器的執(zhí)行單元是什么

微處理器的執(zhí)行單元是什么

評論