近年來(lái),由具有金屬-鐵電-絕緣層-半導(dǎo)體(MFIS)結(jié)構(gòu)的鐵電場(chǎng)效應(yīng)晶體管(FeFET)組成的鐵電存儲(chǔ)器,以其非破壞性讀出、存儲(chǔ)密度高等優(yōu)點(diǎn),成為最具潛力的下一代非揮發(fā)性存儲(chǔ)器件之一。MFIS結(jié)構(gòu)作為FeFET的核心部件,其電學(xué)性能將影響到鐵電存儲(chǔ)器的存儲(chǔ)能力和穩(wěn)定性。在已有的研究中,研究者一方面采用實(shí)驗(yàn)方法研究MFIS結(jié)構(gòu)器件的電學(xué)性能,另一方面試圖從理論上對(duì)器件的電學(xué)性能進(jìn)行研究。

本文將利用Silvaco公司的Atlas器件模擬軟件,結(jié)合Miller等人的鐵電極化模型及電荷薄片模型,對(duì)MFIS結(jié)構(gòu)器件的C—V特性及記憶窗口進(jìn)行模擬,討論應(yīng)用電壓、絕緣層厚度及材料對(duì)MFIS結(jié)構(gòu)器件的影響,探討提高M(jìn)FIS結(jié)構(gòu)器件性能的有效途徑。

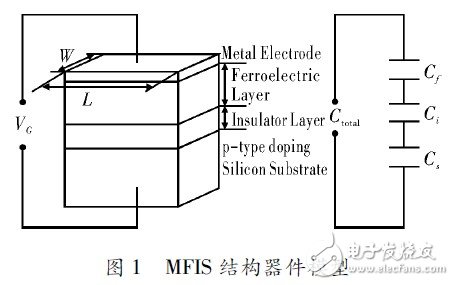

1 MFIS器件結(jié)構(gòu)

MFIS結(jié)構(gòu)是在傳統(tǒng)MOS電容器的基礎(chǔ)上,在金屬電極和絕緣層之間增加具有極化行為的鐵電材料,利用鐵電層的極化行為進(jìn)行二進(jìn)制數(shù)據(jù)存儲(chǔ)。圖1為典型MFIS結(jié)構(gòu)及其等效電路,鐵電層厚度為df,絕緣層厚度為di。理想情況下,不考慮各層之間的界面捕獲電荷、界面態(tài)及各層內(nèi)部空間電荷和雜質(zhì)的影響。電容器的上電極為肖特基接觸,下電極為歐姆接觸。基底采用均勻摻雜的p型硅,厚度達(dá)到要求。

2 模擬方法

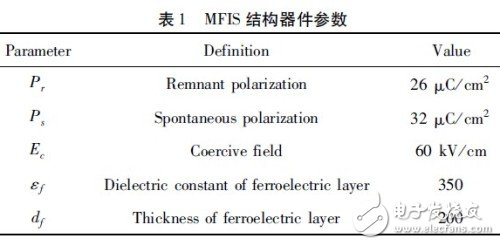

Silvaco公司的器件模擬軟件Atlas,可以對(duì)二維和三維模式下半導(dǎo)體器件的直流、交流及時(shí)域響應(yīng)等進(jìn)行仿真和分析。為考慮MFIS結(jié)構(gòu)器件中鐵電層計(jì)劃行為的飽和狀態(tài)及非飽和狀態(tài),Miller等人提出的鐵電極化模型被改進(jìn)。在Model語(yǔ)句中引入兩種狀下的極化模型Ferro和Unsat.Ferro,器件的相關(guān)參數(shù)在Material語(yǔ)句中進(jìn)行設(shè)置。由于MFIS結(jié)構(gòu)器件在實(shí)際應(yīng)用中多工作于高頻狀態(tài),需要設(shè)置Ferro模型中Fer-roDamp參數(shù)為1。考慮到鐵電薄膜、半導(dǎo)體基底及金屬電極之間的功函數(shù)關(guān)系,MFIS結(jié)構(gòu)的上電極和下電極分別被設(shè)定為肖特基接觸和歐姆接觸。鐵電層采用BNT鐵電薄膜,厚度為200 nm,其參數(shù)可以由文獻(xiàn)中得到,具體參數(shù)如表1所示。

3 結(jié)果與討論

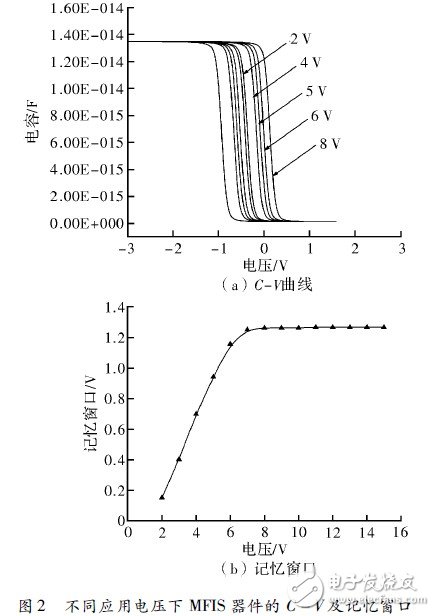

3.1 應(yīng)用電壓對(duì)MFIS結(jié)構(gòu)器件的影響

應(yīng)用電壓的大小不僅能影響鐵電存儲(chǔ)器的存儲(chǔ)能力及穩(wěn)定性,還會(huì)影響到其與半導(dǎo)體集成電路的兼容性。圖2中給出了不同應(yīng)用電壓下MFIS器件的C—V特性及記憶窗口。絕緣層為CeO2,應(yīng)用電壓從2V增加到5 V。由圖中可以看出,由于鐵電層的極化行為,MFIS器件的C—V曲線在不同的掃描電壓方向上出現(xiàn)平移,呈現(xiàn)順時(shí)針的回線狀,并且其寬度隨應(yīng)用電壓的增加逐漸變寬。MFIS器件的記憶窗口隨應(yīng)用電壓的增加而逐漸增大,并在8 V時(shí)達(dá)到飽和。記憶窗口的大小直接影響著MFIS器件的穩(wěn)定性。在較小的記憶窗口下,存儲(chǔ)器的“0”和“1”兩個(gè)邏輯態(tài)容易出現(xiàn)混淆,導(dǎo)致數(shù)據(jù)存取失敗,因此適當(dāng)增加應(yīng)用電壓,有利于提高M(jìn)FIS器件的存儲(chǔ)穩(wěn)定性。

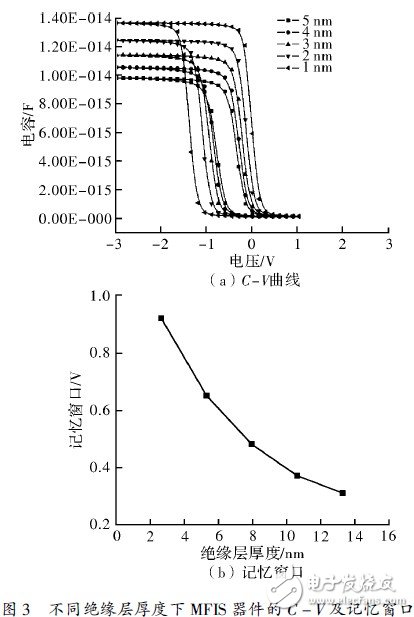

3.2 絕緣層厚度對(duì)MFIS結(jié)構(gòu)器件的影響

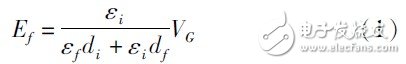

MFIS器件絕緣層的厚度會(huì)影響到MFIS結(jié)構(gòu)的性能。圖3中給出了不同絕緣層厚度下MFIS器件的C—V特性及記憶窗口。器件的應(yīng)用電壓為5 V,絕緣層采用CeO2,厚度從1 nm增加到5 nm。從圖中可以看出,在一定的應(yīng)用電壓下,MFIS器件的C—V曲線隨絕緣層厚度的增加變窄,記憶窗口隨之減小,這與文獻(xiàn)中報(bào)道的絕緣層厚度對(duì)MFIS器件電學(xué)性能的影響一致。這可以由加在鐵電層上的有效電場(chǎng)進(jìn)行解釋。鐵電層上的有效電場(chǎng)Ef為

其中,CG為應(yīng)用電壓;εf和εi為鐵電層和絕緣層的相對(duì)介電常數(shù)。顯然,鐵電層上的有效電場(chǎng)隨著絕緣層厚度的增加而減小,從而導(dǎo)致鐵電層逐漸遠(yuǎn)離飽和狀態(tài),使得電容器的記憶窗口減小。

3.3 絕緣層材料對(duì)MFIS結(jié)構(gòu)器件的影響

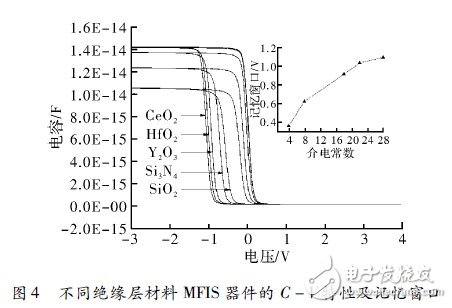

由式(1)可以看出,具有高介電常數(shù)εi的絕緣層,能夠使分配在鐵電層上的有效電場(chǎng)增加,從而使鐵電層趨于飽和,產(chǎn)生一個(gè)較大的記憶窗口。為研究不同絕緣層材料對(duì)MFIS器件相關(guān)性能的影響,利用Arias軟件對(duì)采用SiO2、Si3N4、Y2O3、HfO2及CeO2作為絕緣層的MFIS器件的C—V特性及記憶窗口進(jìn)行了模擬和分析。

圖4給出了在5 V的應(yīng)用電壓下,分別采用不同絕緣層材料時(shí)MFIS器件的C—V特性及記憶窗口。從圖中可以看出,MFIS器件的C—V曲線隨絕緣層介電常數(shù)的增加逐漸變寬,其記憶窗口從0.36 V增大到1.09 V,并逐漸趨于飽和。

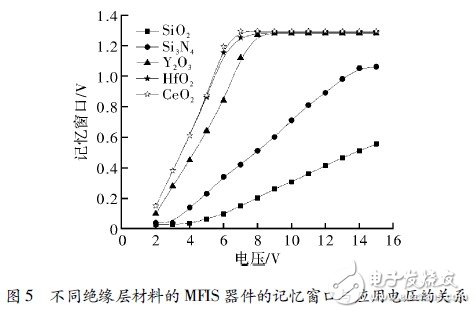

圖5為不同絕緣層材料時(shí)MFIS器件的記憶窗口隨應(yīng)用電壓的變化。從圖中可以看出,高介電常數(shù)為絕緣層jf,MFIS器件的記憶窗口在7 V時(shí)達(dá)到飽和,而低介電常數(shù)為絕緣層時(shí),記憶窗口在15 V時(shí)仍未達(dá)到飽和。這意味著在一定厚度下,高介電常數(shù)的絕緣層能夠使MFIS器件的記憶窗口在一個(gè)較低的應(yīng)用電壓下達(dá)到飽和,從而減小工作電壓,使得其與現(xiàn)代集成電路設(shè)計(jì)工藝相兼容。

4 結(jié)束語(yǔ)

利用器件模擬軟件Arias,結(jié)合飽和狀態(tài)及非飽和狀態(tài)下的鐵電極化模型,研究了應(yīng)用電壓、絕緣層厚度及材料對(duì)MFIS器件的C—V特性及記憶窗口的影響。仿真結(jié)果表明,增加應(yīng)用電壓、減小絕緣層厚度及采用高介電常數(shù)材料,可以使器件的C—V曲線逐漸變寬,記憶窗口逐漸增大。但是考慮到MFIS器件與現(xiàn)代集成電路的工作電壓的兼容性,以及過(guò)薄的絕緣層可能會(huì)引起的漏電流,使得采用高介電常數(shù)的絕緣材料作為MFIS器件的絕緣層成為一個(gè)提高M(jìn)FIS器件性能的有效途徑。

-

模擬設(shè)計(jì)

+關(guān)注

關(guān)注

1文章

55瀏覽量

18482 -

Atlas

+關(guān)注

關(guān)注

0文章

27瀏覽量

14192

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

模擬設(shè)計(jì)中噪聲分析誤區(qū)

模擬設(shè)計(jì)中的噪聲誤區(qū)

LED器件的電學(xué)指標(biāo)有哪幾項(xiàng)

基于Atlas的MFIS結(jié)構(gòu)器件電學(xué)性能模擬

模擬設(shè)備高速轉(zhuǎn)換器

Cadence教程之如何使用VieloSo模擬設(shè)計(jì)環(huán)境進(jìn)行設(shè)計(jì)

PSoC Creator模擬設(shè)計(jì):如何解決模擬電壓?jiǎn)栴}

PSoC Creator模擬設(shè)計(jì):Analog Device Viewer

PSoC Creator模擬設(shè)計(jì):引腳放置的模擬及注意事項(xiàng)

模擬設(shè)計(jì)中噪聲分析的誤區(qū)及注意事項(xiàng)

陶瓷的微觀結(jié)構(gòu)和電學(xué)性能

基于Atlas的MFIS結(jié)構(gòu)器件電學(xué)性能模擬設(shè)計(jì)

基于Atlas的MFIS結(jié)構(gòu)器件電學(xué)性能模擬設(shè)計(jì)

評(píng)論