時鐘芯片的測試工作需細致入微,涵蓋從時鐘生成過程到芯片內部關鍵模塊的全面評估。其核心功能在于產生穩定且準確的頻率輸出,并能根據系統需求靈活調整。因此,測試的重點在于驗證芯片內部各個環節的穩定性和精確性。

時鐘生成機制解析:時鐘芯片的生成過程可類比為精密調控的水流灌溉系統。外部輸入的參考時鐘作為“水源”,進入芯片后,通過多個相位鎖定環(PLL)模塊進行頻率的倍頻或分頻,最終輸出多種頻率的時鐘信號。測試中,需確保PLL模塊的鎖定性能和穩定性,以及倍頻、分頻后的頻率準確性。

相位與頻率調控機制:相位鑒頻器(PFD)如同“流量計”,負責檢測輸入時鐘與反饋時鐘間的相位差異。任何微小的相位偏差都可能導致輸出時鐘的不準確。PFD將相位差傳遞給電荷泵,電荷泵再與低通濾波器協同工作,將相位差轉換為控制電壓信號,以穩定VCO的輸出頻率。測試需驗證PFD能否精確捕捉相位差,以及電荷泵和濾波器能否穩定生成相應的控制信號。

壓控振蕩器(VCO)的驗證:VCO如同“可調水流速的水泵”,根據輸入電壓生成對應頻率的信號。測試中,需驗證VCO能否根據不同控制電壓產生所需頻率,并關注其輸出的相位噪聲和頻率抖動,這些參數直接影響系統的精度和穩定性。

分頻與輸出端口評估:時鐘芯片將高頻信號通過分頻器降低至所需頻率,再通過輸出端口提供給系統。測試中,需確認分頻器的準確性及輸出端口的信號質量,包括占空比、上升/下降時間及抖動等。

綜合測試內容:為確保時鐘芯片的穩定性和準確性,測試內容涵蓋以下方面:

DC測試:驗證芯片各節點的電平,確保電路工作在設計的電平范圍內。

頻率輸出驗證:在PLL閉環和開環狀態下,確認輸出頻率的準確性。

動態響應測試:在不同負載和溫度條件下,測試芯片的響應,確保輸出頻率穩定。

功耗測量:測量芯片的靜態和動態功耗,確保其符合設計要求。

綜上所述,時鐘芯片的測試流程既嚴謹又復雜,需全面關注信號在芯片內部的流轉過程,確保每一步都在設計范圍內。通過系統化的測試流程,可確保時鐘芯片在各種應用場景下提供準確、穩定的頻率輸出。

-

芯片

+關注

關注

456文章

51192瀏覽量

427325 -

測試

+關注

關注

8文章

5382瀏覽量

127075 -

時鐘

+關注

關注

11文章

1747瀏覽量

131804

發布評論請先 登錄

相關推薦

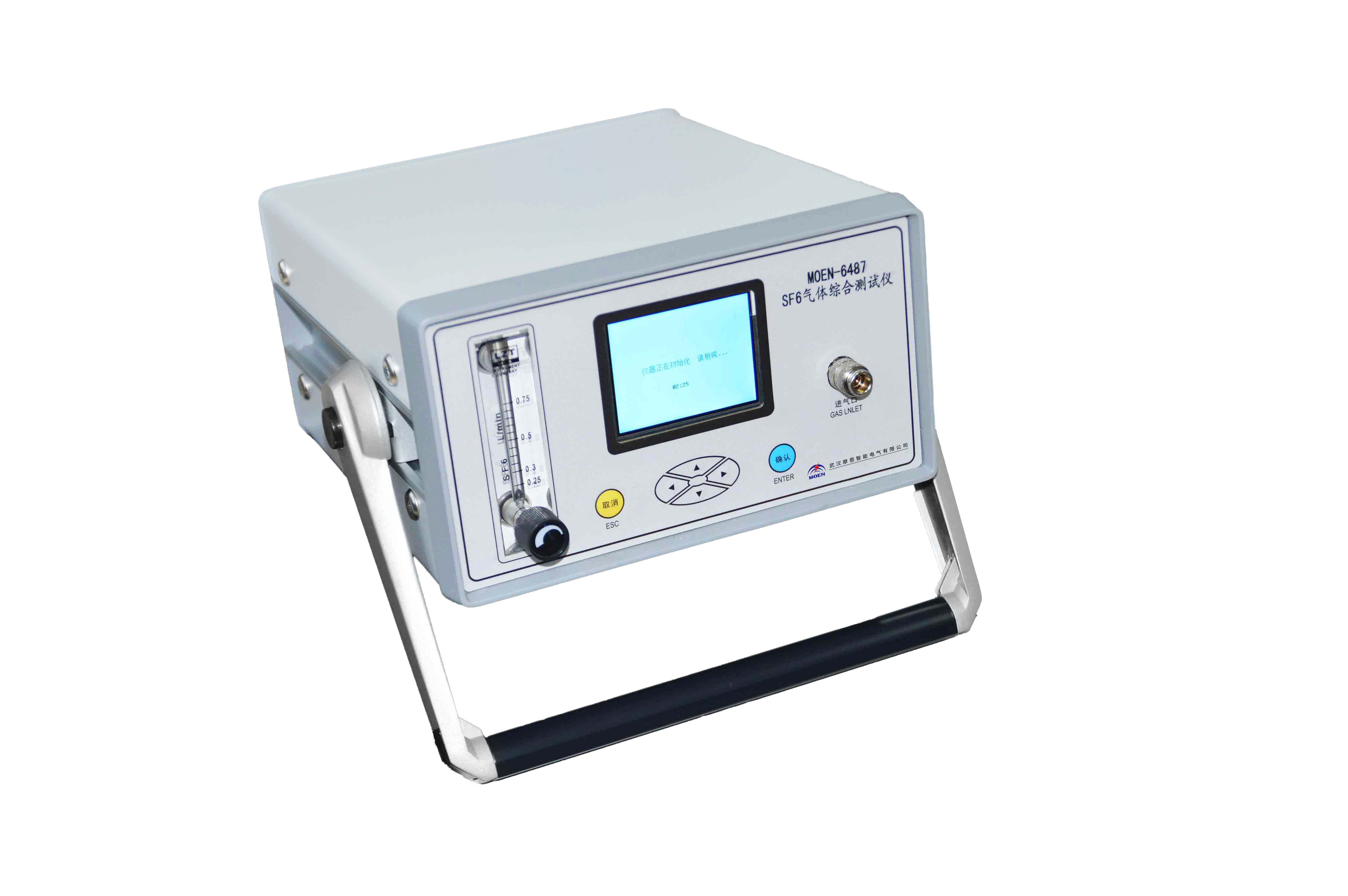

艾法斯Aeroflex 3920 無線電綜合測試儀 3920B

直流充電樁(機)綜合測試儀:確保直流充電樁高效安全運行的關鍵設備

艾法斯 Aeroflex 3920 綜合測試儀

4957系列射頻微波綜合測試儀

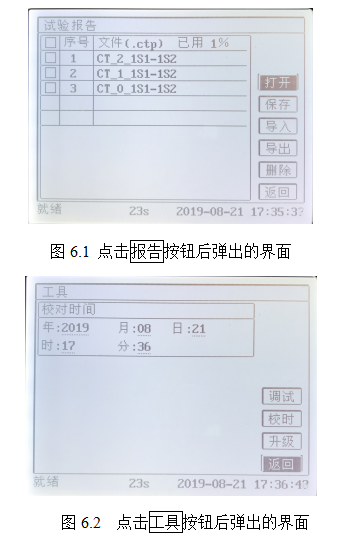

SF6綜合測試儀操作步驟——每日了解電力知識

SF6氣體綜合測試儀如何測量——每日了解電力知識

計量裝置綜合測試系統的接線方式——每日了解電力知識

互感器綜合測試儀的按鈕功能——每日了解電力知識

EV4000新能源汽車動力系統綜合測試儀

無線電綜合測試儀

光伏逆變器綜合測試儀是什么

精密力學檢測設備 | 美能電池片拉脫力綜合測試儀

時鐘芯片綜合測試策略:從生成過程到關鍵模塊

時鐘芯片綜合測試策略:從生成過程到關鍵模塊

評論