文章來(lái)源:半導(dǎo)體與物理

原文作者:jjfly686

本文介紹了3D-NAND浮柵晶體管結(jié)構(gòu)。

傳統(tǒng)平面NAND閃存技術(shù)的擴(kuò)展性已達(dá)到極限。為了解決這一問(wèn)題,3D-NAND閃存技術(shù)應(yīng)運(yùn)而生,通過(guò)在垂直方向上堆疊存儲(chǔ)單元,大幅提升了存儲(chǔ)密度。本文將簡(jiǎn)要介紹3D-NAND浮柵晶體管。

浮柵晶體管的工作原理

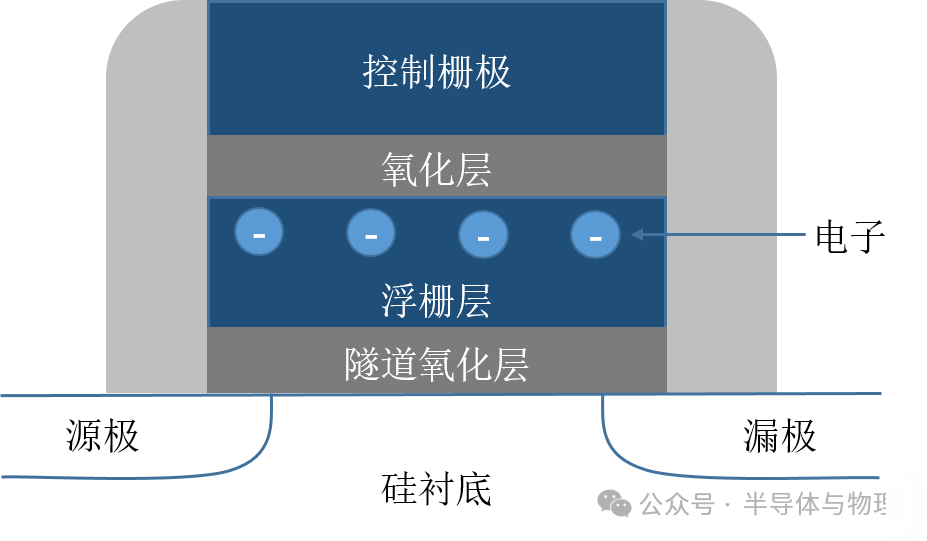

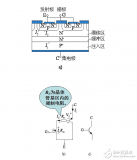

浮柵晶體管是閃存技術(shù)的核心組件,其基本原理是通過(guò)在浮柵中存儲(chǔ)或釋放電荷來(lái)改變晶體管的閾值電壓,從而實(shí)現(xiàn)數(shù)據(jù)的寫入和擦除。浮柵是一個(gè)隔離的導(dǎo)電層,通常由多晶硅制成,能夠長(zhǎng)時(shí)間保持電荷,確保數(shù)據(jù)的持久性。

(平面浮柵晶體管)

3D-NAND中的浮柵晶體管結(jié)構(gòu)

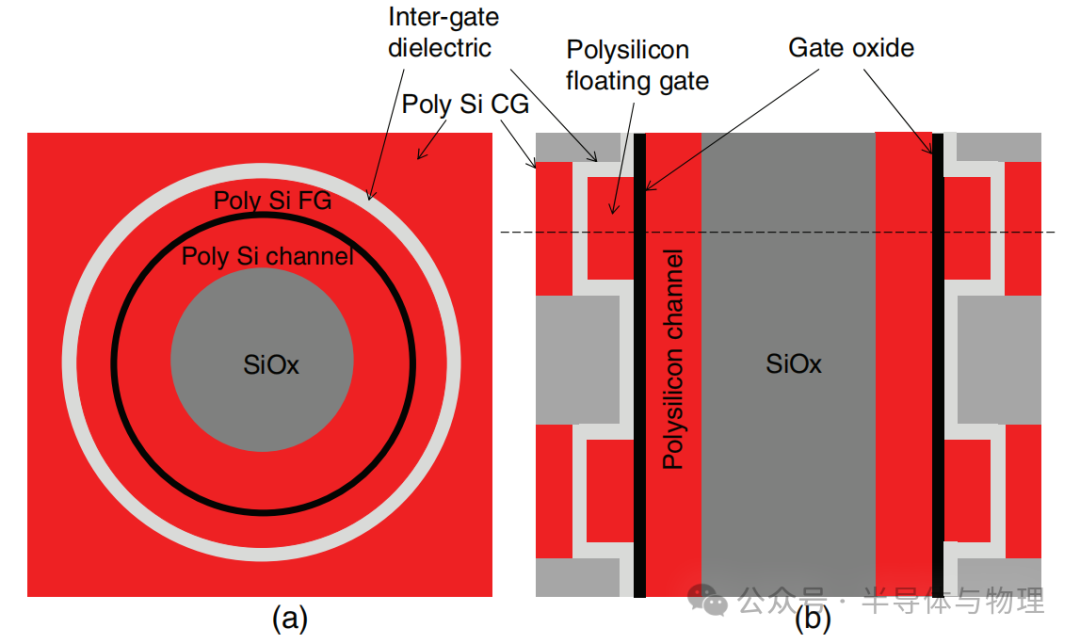

1.第一種材料結(jié)構(gòu)

(a) 顯示了3D-NAND單元的俯視圖,其中包含一個(gè)多晶硅浮柵,該浮柵由氧化物-多晶硅-氧化物-氮化物(OPOP)堆棧組成。這種結(jié)構(gòu)允許每個(gè)存儲(chǔ)單元獨(dú)立地存儲(chǔ)電荷,從而表示不同的數(shù)據(jù)狀態(tài)。

圖(b) 是3D-NAND單元的側(cè)視截面圖,展示了多晶硅浮柵的具體位置。在這個(gè)結(jié)構(gòu)中,浮柵位于控制柵和半導(dǎo)體多晶通道之間,并通過(guò)隧穿氧化層與襯底隔離。當(dāng)向控制柵施加電壓時(shí),電子可以通過(guò)量子隧穿效應(yīng)進(jìn)入浮柵或從浮柵中逃逸,從而實(shí)現(xiàn)數(shù)據(jù)的寫入和擦除。

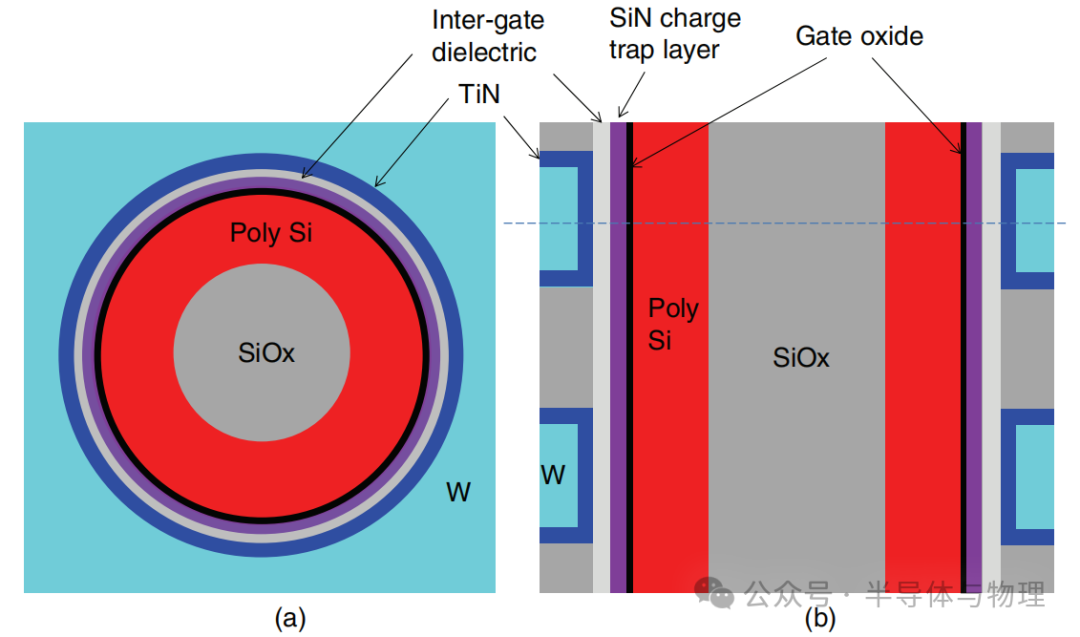

2.第二種材料結(jié)構(gòu)

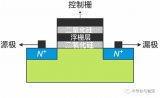

圖2(a) 顯示了3D-NAND單元的俯視截面圖,其中包含一個(gè)氮化物材料電荷陷阱層,該層由氧化物-氮化物-氧化物-氮化物(ONON)堆棧組成。與多晶硅浮柵相比,氮化物電荷陷阱層具有更好的耐久性和數(shù)據(jù)保持能力,因?yàn)殡姾刹皇侵苯哟鎯?chǔ)在導(dǎo)體中,而是被陷阱在氮化物材料的缺陷中,這有助于減少數(shù)據(jù)丟失的風(fēng)險(xiǎn)。

圖(b) 是3D-NAND單元的側(cè)視截面圖,展示了氮化物電荷陷阱層的具體位置。在這種結(jié)構(gòu)中,電荷陷阱層位于控制柵和多晶硅之間,通過(guò)隧穿氧化層與襯底隔離。當(dāng)向控制柵施加電壓時(shí),電子可以通過(guò)量子隧穿效應(yīng)進(jìn)入電荷陷阱層或從電荷陷阱層中逃逸,從而實(shí)現(xiàn)數(shù)據(jù)的寫入和擦除。

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27703瀏覽量

222630 -

NAND

+關(guān)注

關(guān)注

16文章

1690瀏覽量

136460 -

3D

+關(guān)注

關(guān)注

9文章

2910瀏覽量

107995 -

晶體管

+關(guān)注

關(guān)注

77文章

9745瀏覽量

138896

原文標(biāo)題:3D-NAND浮柵晶體管結(jié)構(gòu)

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

什么是3d晶體管

晶體管的結(jié)構(gòu)特性

IGBT絕緣柵雙極晶體管的基本結(jié)構(gòu)與特點(diǎn)

IGBT絕緣柵雙極晶體管

絕緣柵雙極晶體管(IGBT)

絕緣柵雙極晶體管原理、特點(diǎn)及參數(shù)

絕緣柵雙極晶體管

聯(lián)柵晶體管(GAT)是什么意思?

絕緣柵雙極晶體管結(jié)構(gòu)與工作原理解析

Nand Flash結(jié)構(gòu)及錯(cuò)誤機(jī)制

NAND 閃存概述

3D-NAND浮柵晶體管的結(jié)構(gòu)解析

3D-NAND浮柵晶體管的結(jié)構(gòu)解析

評(píng)論