產品簡述

MS1242/MS1243是一款高精度、寬動態范圍、?-Σ模數轉

換芯片,其工作電壓為2.7V至5.25V,可以達到24bit無失碼轉

換,有效精度可達21bit。MS1242/MS1243可以廣泛使用在工

業控制、稱重、液體/氣體化學分析、血液分析、智能發送

器、便攜式測量儀器等領域。

主要特點

? 24位無失碼、21位有效精度模數轉換器

? 集成50Hz、60Hz陷波濾波器

? INL小于0.0015%

? 可編程增益(1?128)

? 單周期建立時間

? 可編程數據速率輸出

? 外接參考電壓范圍:0.1V?5V

? 集成校準功能

? 兼容SPI總線接口

? 低功耗

? 4個模擬輸入通道 (MS1242)

? 8個模擬輸入通道 (MS1243)

應用

?工業過程控制

?重量計

?液體/氣體化學分析

?血液計

?智能變換器

?便攜式設備

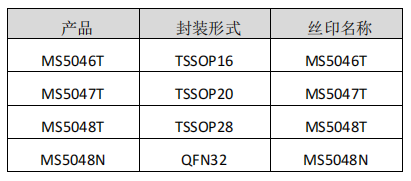

產品規格分類

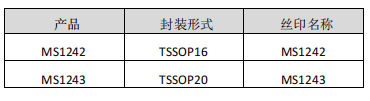

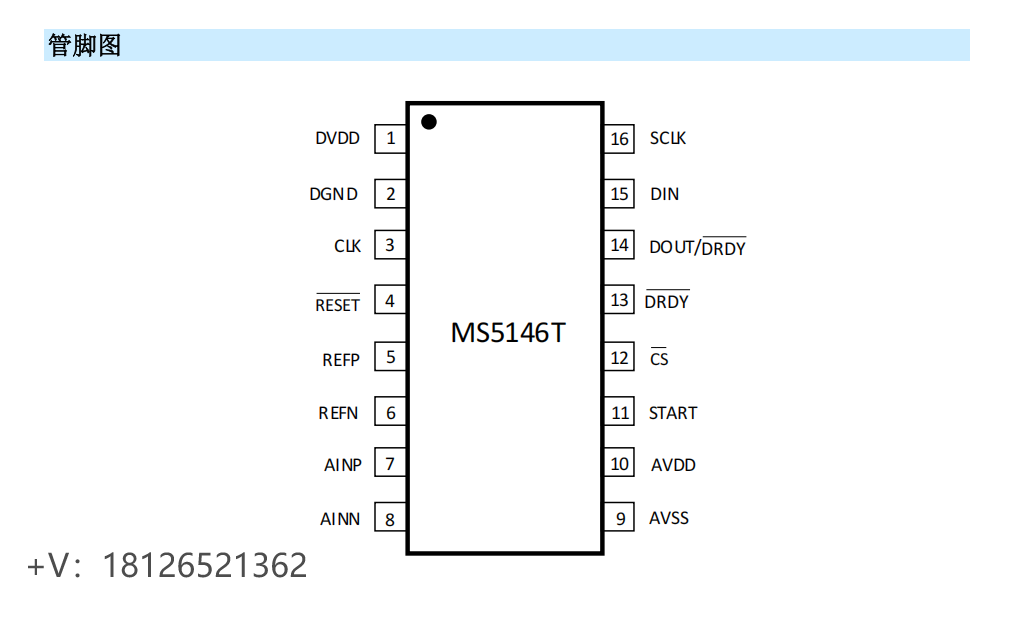

管腳圖

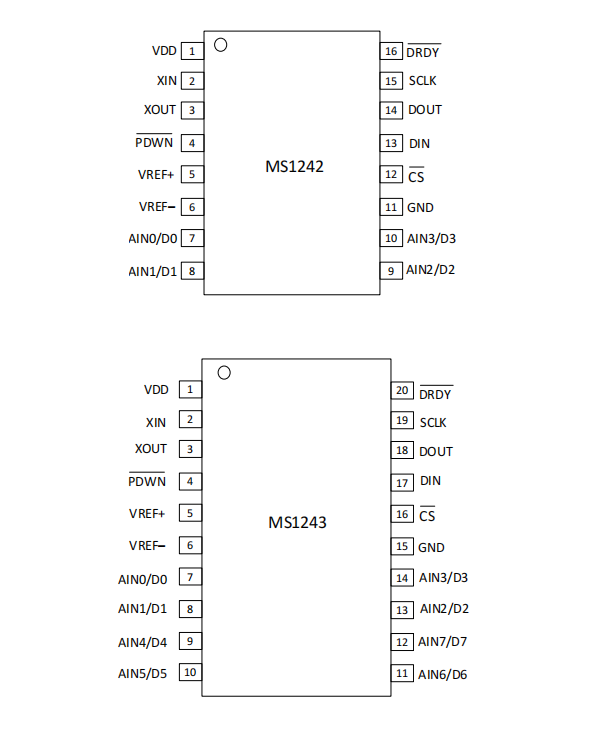

管腳說明

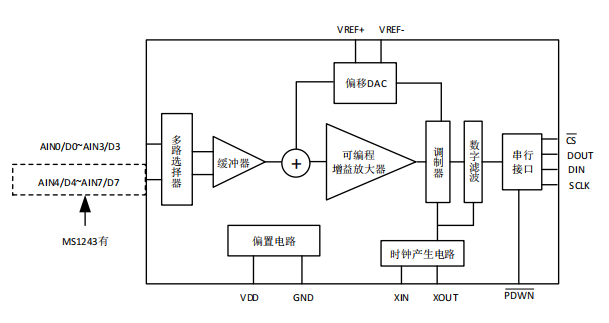

內部框圖

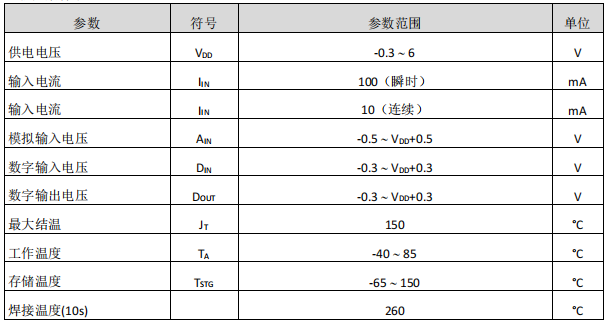

極限參數

芯片使用中,任何超過極限參數的應用方式會對器件造成永久的損壞,芯片長時間處于極限工作

狀態可能會影響器件的可靠性。極限參數只是由一系列極端測試得出,并不代表芯片可以正常工作在

此極限條件下。

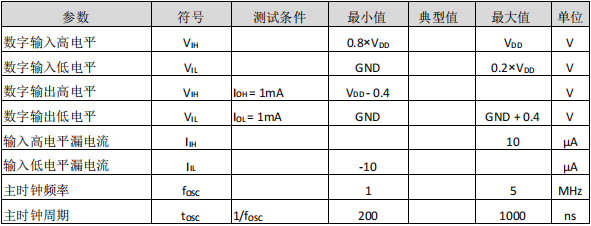

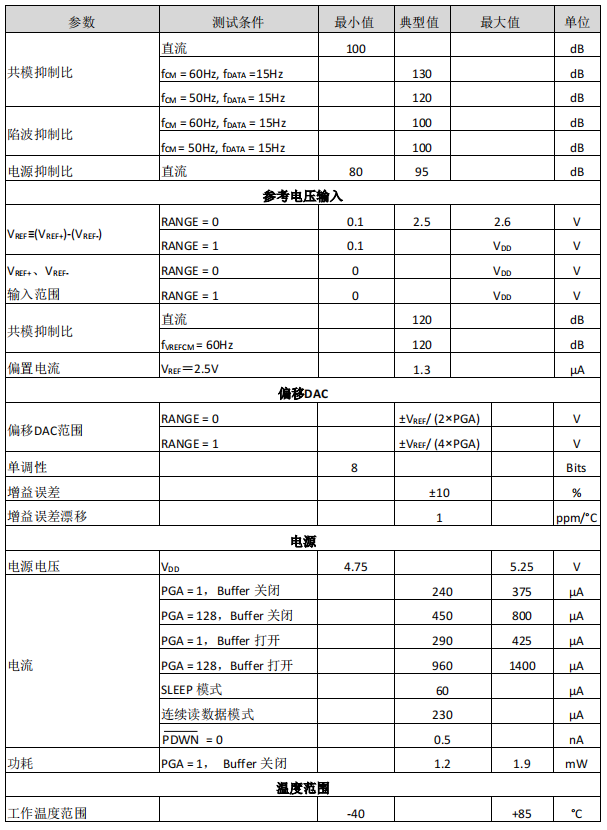

電氣參數

數字特性:TMIN到 TMAX,VDD= 2.7V 到 5.25V。

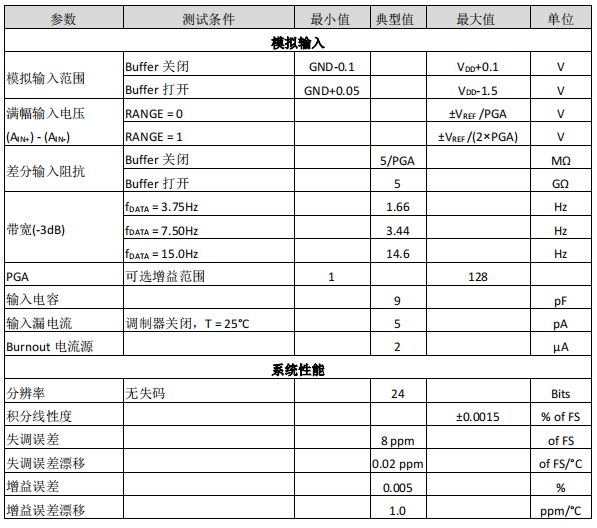

電學特性:TMIN到 TMAX,VDD=+5V,fMOD=19.2kHz,PGA=1,打開 Buffer,

fDATA=15Hz,VREF≡ (VREF+)–(VREF–)= +2.5V。

如有需求請聯系——三亞微科技 王子文(16620966594)

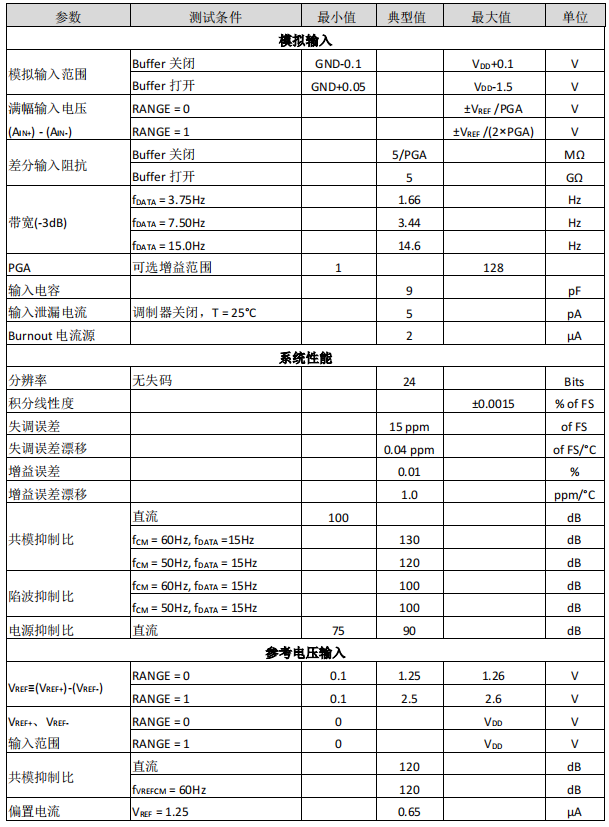

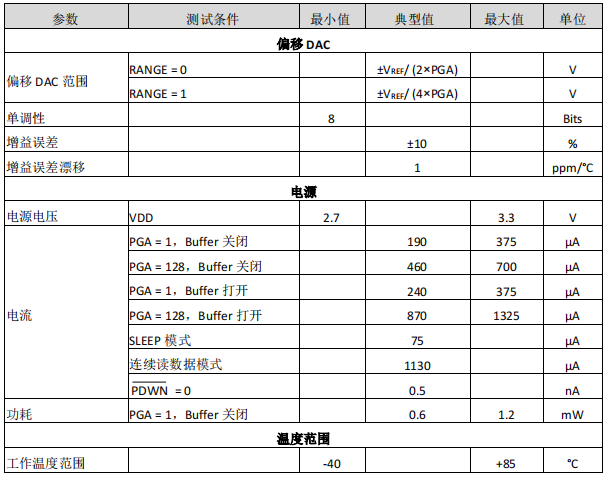

電學特性:TMINto TMAX, VDD= +3V, fMOD= 19.2kHz, PGA = 1, Buffer ON,

fDATA= 15Hz,VREF≡(VREF+)-(VREF-)= +1.25V。

功能描述

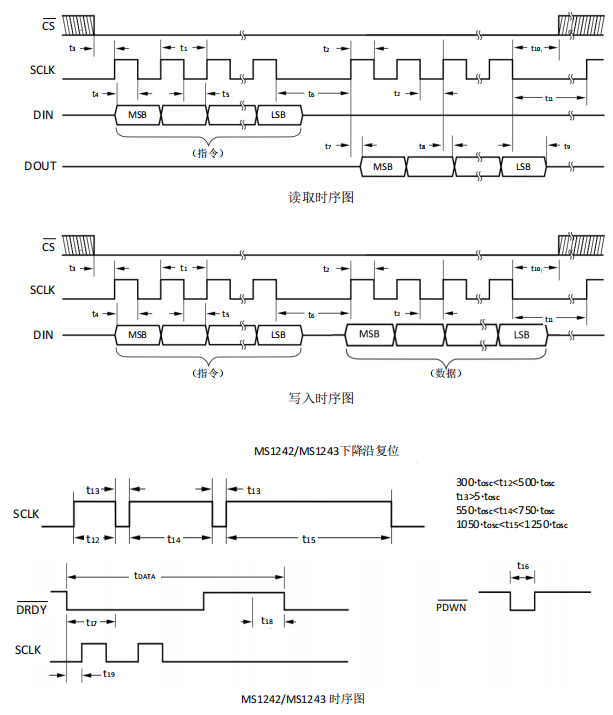

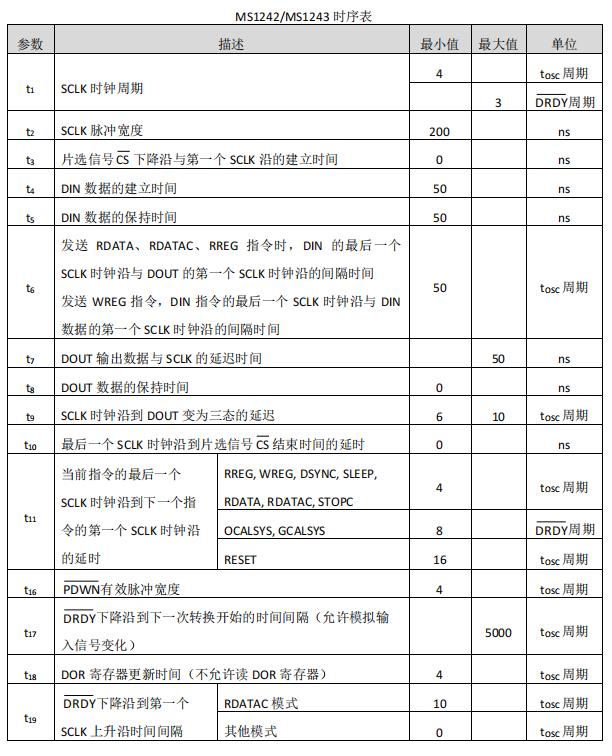

1. 時序圖

如有需求請聯系——三亞微科技 王子文(16620966594)

2. 模塊描述

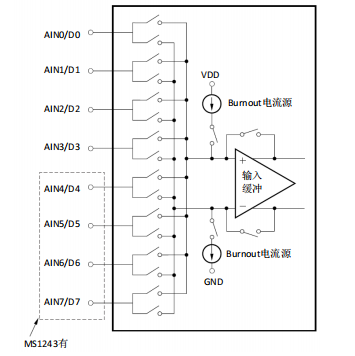

2.1 輸入多路信號選擇器(Input Multiplexer)

MS1242 的輸入信號通道可以任意組合,多路輸入選擇原理圖如下圖所示。

MS1242 可以最多配置 2 對差分輸入或 3 個單端輸入,MS1243 可以最多配置 4 對差分輸入或 7 個

單端輸入。例如,如果選擇 AIN1 為差分正(負)信號的一個輸入端,可以選擇任意其它輸入端為負

(正)端輸入。

MS1242 可以實現在單時鐘周期內完成輸入信號的選擇切換、內部數字濾波器的穩定輸出。為了降

低切換誤差,要求在 DRDY 信號變低后立即配置 MUX 寄存器,允許操作時間參見時序圖 t

17。

2.2 Burnout 電流源

Burnout 電流源用來檢測輸入傳感器短路或開路,其打開或關閉是通過內部寄存器位(BOCS)來設置

的,其電流大小為 2μA,當輸入傳感器處于短路時,Burnout 電流源使得 MS1242 輸出近似為 0;當輸

入傳感器處于開路時,Burnout 電流源使得 MS1242 輸出近似為滿幅狀態。

2.3 輸入緩沖器(Buffer)

在沒有使能模擬輸入緩沖器(Buffer)時,輸入阻抗約 5MΩ/PGA。當系統要求較高的輸入阻抗時,可

以使能模擬輸入緩沖器,此時可以將輸入阻抗提高約到 5GΩ。

緩沖器的使能信號可以由內部寄存器 ACR 控制。當 ACR 寄存器的 BUF 為高時,輸入緩沖器使

能,有效提高輸入阻抗。如果使能緩沖器,芯片增加額外的功耗。消耗功率的大小與 PGA 的增益有

關,PGA=1 時,增加約 50μA 電流,而 PGA=128 時,增加的電流則達 150μA。當開啟緩沖器后,對輸

入信號的范圍有所要求,此時輸入信號的范圍為 AGND+0.3V ? AVDD-1.5V。

2.4 可編程增益放大器(PGA)

內部的電壓增益放大器可以配置為 1,2,4,8,16,32,64,128。通過使用 PGA 可以提高有效轉換精度。

2.5 偏移 DAC

為了擴展輸入范圍,MS1242 內部集成了一個偏移 8bitDAC。偏移 DAC 是一個可編程電壓源,輸入

信號被 PGA 放大后,和偏移 DAC 輸出電壓相加,輸入到?-Σ 調制器中。

2.6 調制器(Modulator)

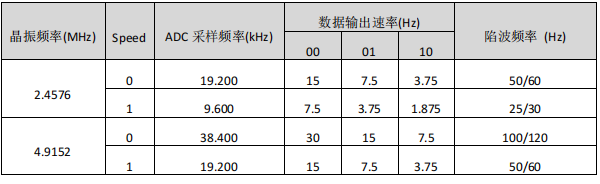

MS1242 的調制器是單環、2 階?-Σ 調制器,調制器的采樣頻率可以通過 SPEED(ACR 寄存器的 bit 5)

控制,具體如下表所示:

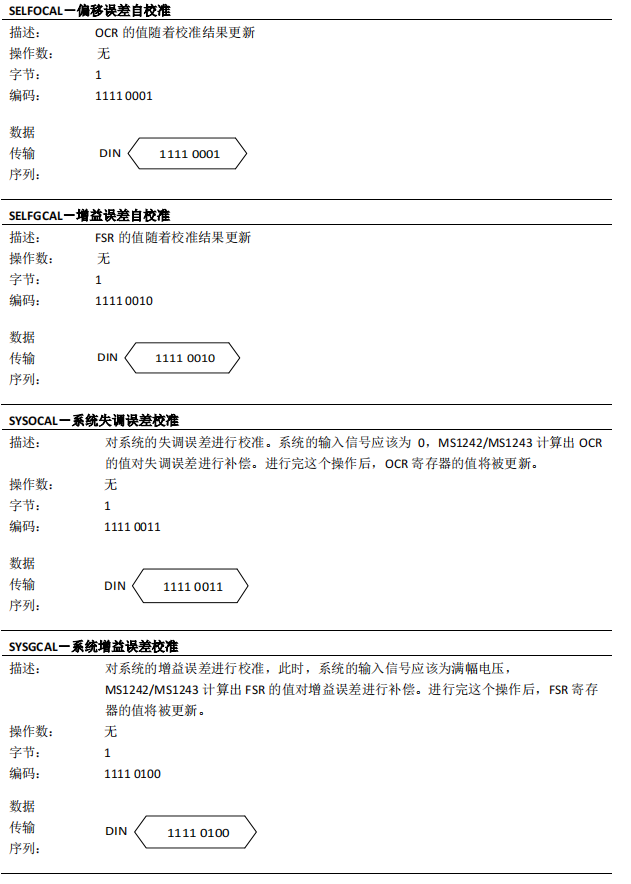

2.7 校準(Calibration)

MS1242 校準包括內部校準和系統校準,校準包括偏移誤差校準、增益誤差校準。

內部校準是通過內部校準命令:偏移和增益誤差自校準(SELFCAL)、增益誤差自校準(SELFGAL)、偏

移誤差自校準(SELFOCAL)。每個校準占用兩個數據轉換周期。在校準期間,ADC 關斷外部輸入端口,

在 SELFCAL 和 SELFGAL 期間 PGA 必須設置為 1。當輸入參考電壓大于 VDD-1.5V 時,必須關斷輸入緩沖

器。

系統校準可以校準系統的偏移誤差和增益誤差,校準必須要求輸入正確的輸入信號后進行。系統

偏移誤差校準(SYSOCAL) 要求輸入零差分電壓,芯片計算出系統的偏移誤差值并寫入 OCR 寄存器中,

在正常轉換時予以抵消。系統增益誤差校準(SYSGCAL) 要求輸入正滿幅度電壓,芯片計算出系統的增

益誤差并寫入 FSR 寄存器中,在正常轉換時予以抵消。每個校準占用兩個數據轉換周期。

在芯片重新上電、外部環境溫度改變、增益(PGA)改變后必須進行誤差校準,以保證模數轉換的正

確。在校準期間,RANGE 位 (ACR bit2)必須設置成 0,且關閉偏移 DAC。完成校準后 DRDY 管腳變低。

校準完成后的第一個輸出數據須舍棄。

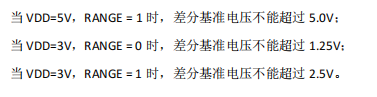

2.8 外部基準電壓

MS1242 需要外接參考電壓,具體值的選擇通過內部 ACR 寄存器配置。參考電壓接在 VREF+與

REF-管腳上,電壓不能超過芯片的電源電壓。

當 VDD=5V,RANGE = 0 時,差分基準電壓不能超過 2.5V;

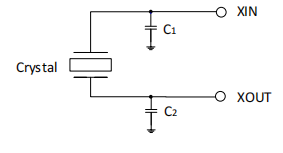

2.9 時鐘產生電路(CLOCK GENERATOR)

MS1242 可以外接晶體、振蕩器或時鐘。如果接外部時鐘,則從 XIN 管腳輸入,此時 XOUT 懸空。

如果外部接晶體,電路要求如下:要求在 XIN 及 XOUT 管腳上同時接 10pF~20pF 的電容。

2.10 數字濾波器(FIR)

MS1242 帶有一個可編程的 FIR 濾波器。FIR 濾波器可以被配置成不同的輸出速率。當使用

2.4576M 的時鐘時,MS1242 的輸出數據的速率可以被配置成 15Hz、7.5Hz 或者 3.75Hz。此時,FIR 濾

波器可以同時對 50Hz 和 60Hz 的雜波信號進行陷波濾波。

若希望得到其他的輸出數據速率,則須使用其他的時鐘頻率。此時,陷波頻率也同時跟著改變。

比如,當使用默認的寄存器配置,時鐘頻率為 3.6864M 的時候,

輸出數據的頻率為: (3.6864MHz/2.4576MHz) ×15Hz = 22.5Hz

陷波頻率為: (3.6864MHz/2.4576MHz ) ×(50Hz 和 60Hz) = (75Hz 和 90Hz)

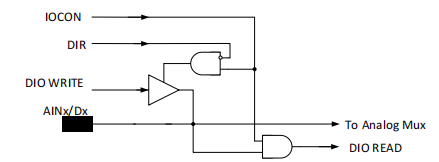

2.11 數據 I/O 接口

MS1242/MS1243 的數據接口提供雙重功能:模擬輸入和數據 I/O。此端口的配置通過內部

IOCON、DIR、DIO 寄存器設置。上電默認配置為模擬輸入。下圖是輸入端口的等效電路:

2.12 串行總線接口( SPI )

MS1242/MS1243 通過 SPI 總線與外部的控制器進行通訊。MS1242/MS1243 只能用于從模式。總線

接口是標準的四線 SPI 總線,包括 CS 、SCLK、 DIN 和 DOUT。

2.12.1 片選信號( CS )

在與 MS1242/MS1243 進行通訊前,外部的控制器必須先發出 CS 片選信號。在整個通訊期間, CS

信號必須維持為低。當 CS 信號變高后,整個 SPI 總線會被復位。 CS 信號也可以被接為常低。

2.12.2 串行時鐘(SCLK)

SCLK 內置施密特觸發器。如果在 3 個 DRDY 周期內都沒有出現 SCLK 時鐘,那么在下一個 SCLK 來

臨時,SPI 總線將被復位,進而開始下一個通訊周期。SCLK 上的一個特定的波形可以復位整個芯片。

2.12.3 數據輸入(DIN)和數據輸出(DOUT)

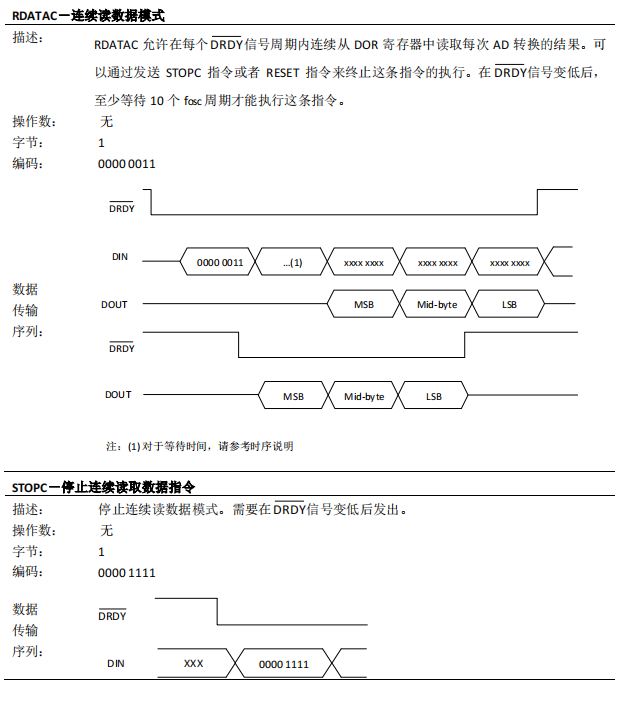

DIN 和 DOUT 引腳分別用來輸入和輸出數據。在未使用時,DOUT 為高阻態,允許將 DIN 和 DOUT

接在一起然后通過一個雙向的總線來驅動它。需要注意的是,這種情況下不適合向 MS1242/MS1243 發

出 RDATAC 指令。因為 RDATAC 指令需要用 STOPC 指令或者 RESET 指令來終止。而在 RDATAC 模式

下,這條雙向總線會一直被 DOUT 占用向外部發送數據,所以就無法通過總線向 MS1242/MS1243 發送

STOPC 指令或者 RESET 指令,就無法終止 RDATAC 狀態。如果 DOUT 發送的數據中形成 STOPC 或者

RESET 指令,此時 DIN 會檢測到 STOPC 或者 RESET 指令,從而終止 RDATAC 狀態或復位芯片。

2.13 數據準備就緒 ( DRDY )

DRDY 信號表示內部數據寄存器的狀態。當內部數據寄存器 DOR 內新的數據準備就緒時, DRDY

信號會變低。當執行完 DOR 的讀操作后, DRDY 信號變高。在 DOR 寄存器的數據準備更新時 DRDY 信

號也會變高,表示此時 DOR 寄存器內的數據不可用,防止在 DOR 寄存器進行更新時從 DOR 寄存器內

讀取數據,參見時序圖 t18。

DRDY 信號也可以從 ACR 寄存器的 bit 7 來獲得。

2.14 數據同步(DSYNC)

MS1242/MS1243 可以通過 DSYNC 指令來進行數據同步。當使用 DSYNC 指令進行數據同步時,數

字濾波器在 DSYNC 指令的最后一個 SCLK 時鐘的邊沿被復位,同時調制器也將處于復位狀態。在

DSYNC 后的第一個 SCLK 內的系統時鐘的上升沿,重新開始轉換。

2.15 上電速率(Supply Voltage Ramp Rate)

MS1242/MS1243 的上電電路可兼容數字電源低到 1V/10ms 的上電速率,為了確保正常工作,電源

電壓應單調上升。

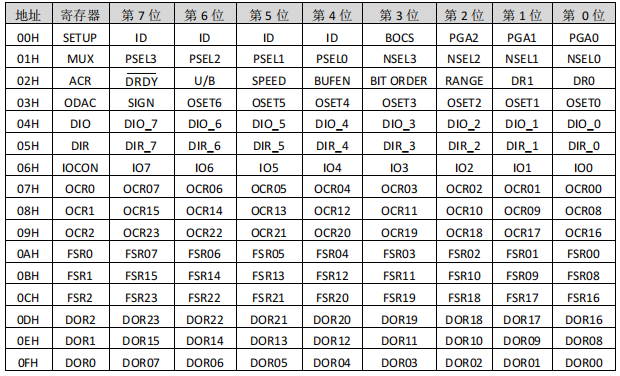

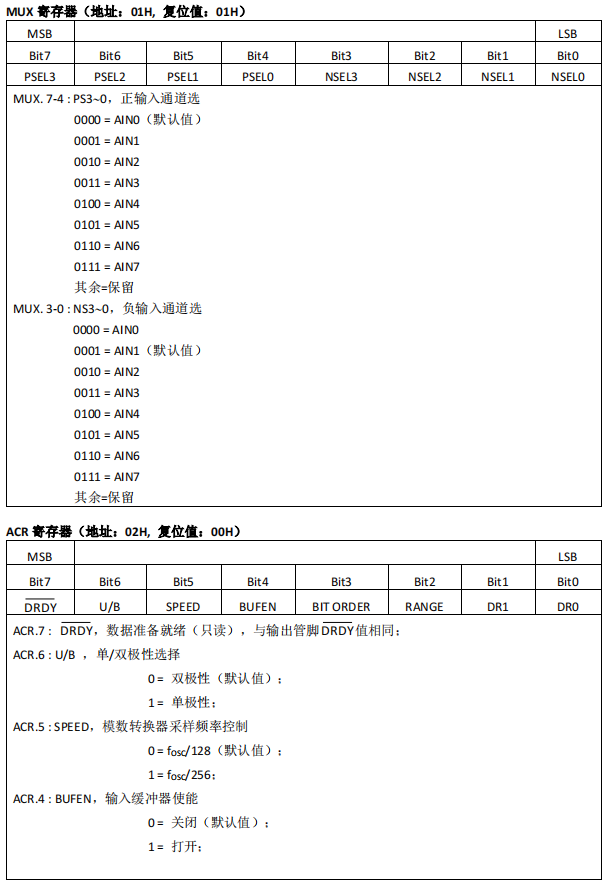

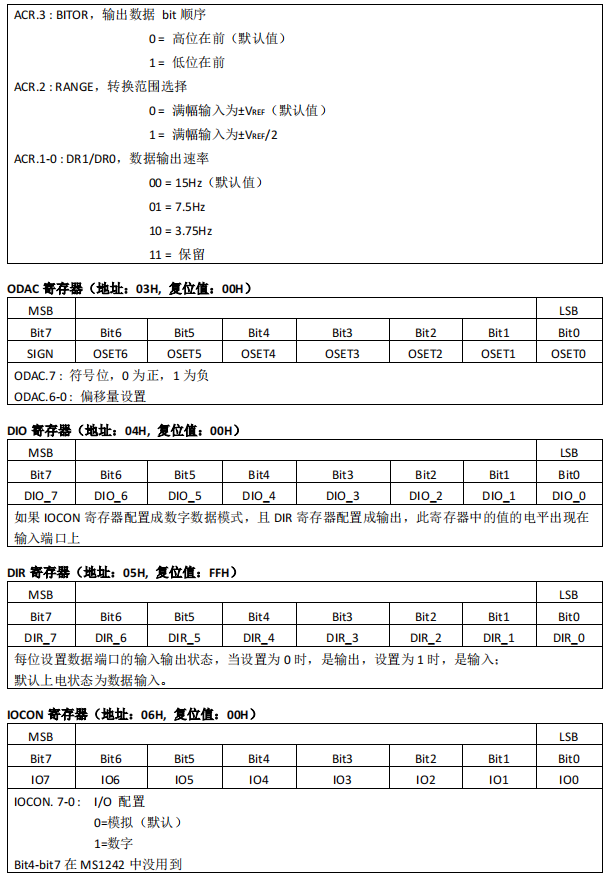

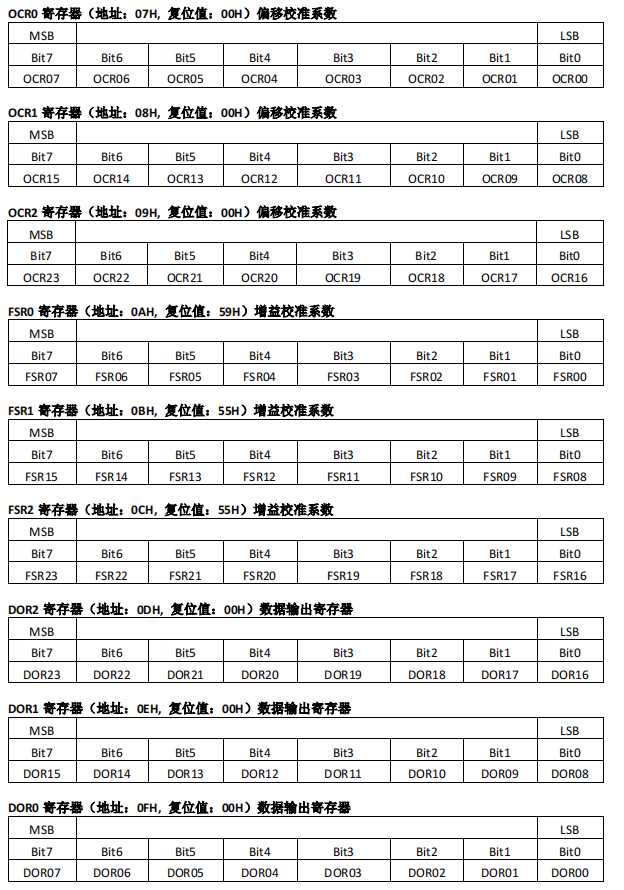

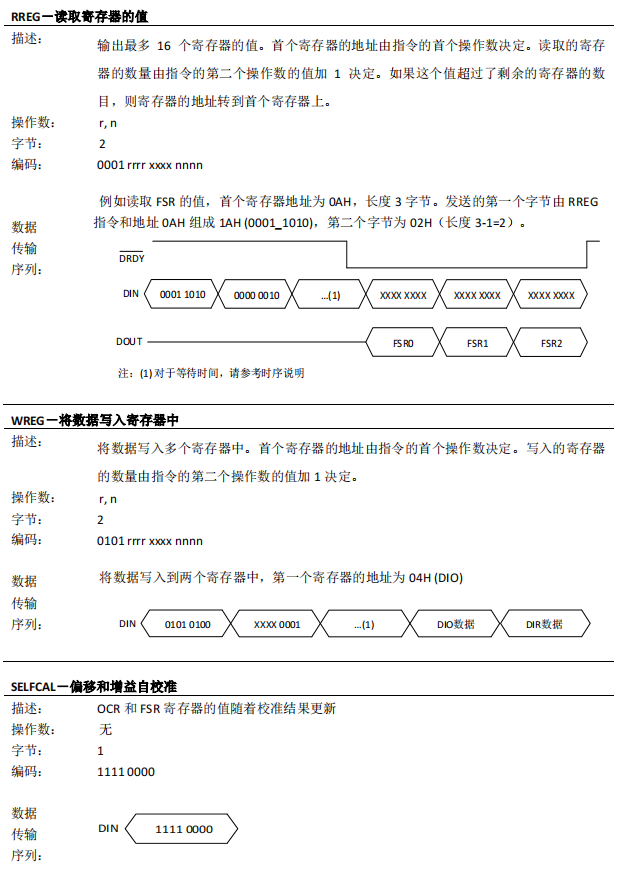

3. 寄存器描述

MS1242/MS1243 通過控制寄存器來配置工作方式。

3.1 寄存器列表

MS1242/MS1243 內部寄存器詳細列表如下表所示:

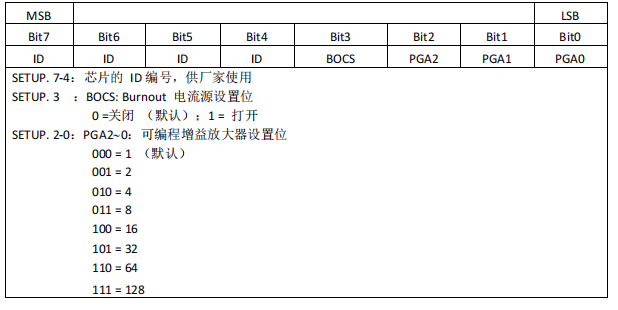

3.2 寄存器詳細描述

SETUP 寄存器(地址:00H, 復位值:X0H)

如有需求請聯系——三亞微科技王子文(16620966594)

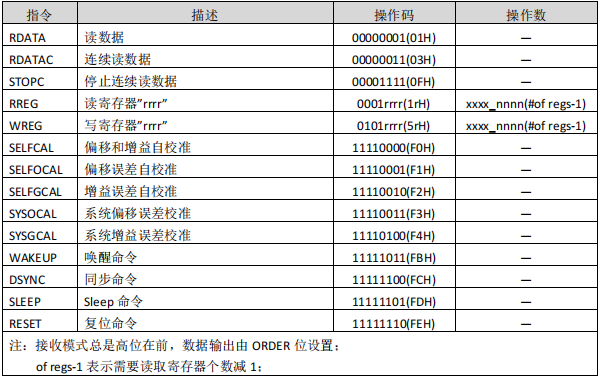

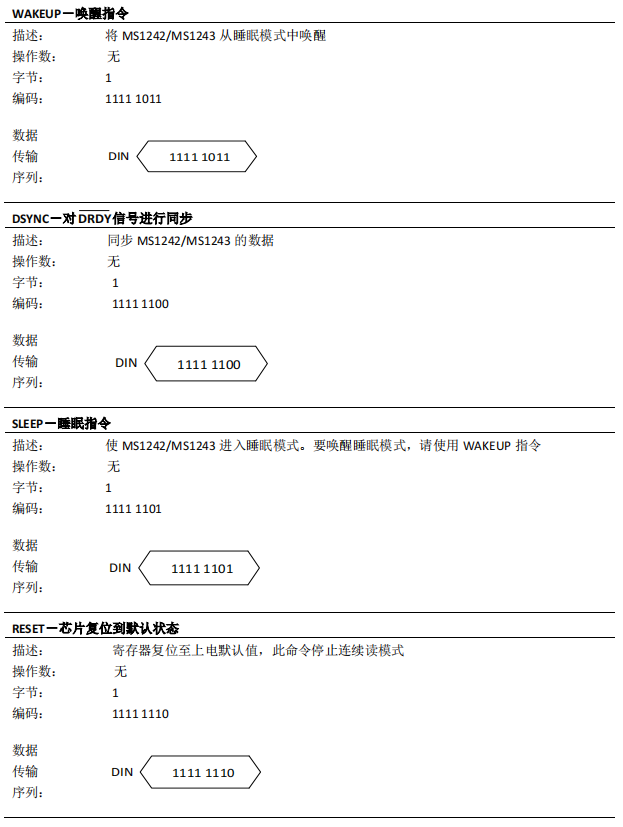

4. MS1242/MS1243 指令描述

MS1242/MS1243 使用了一系列指令,這些指令中有些是單條的(比如 RESET),有些則需要另外

的操作數(比如 WREG 等)。

操作數:

n = 數量 ( 0 到 127 )

r = 寄存器 ( 0 到 15 )

x = 任意值

指令列表

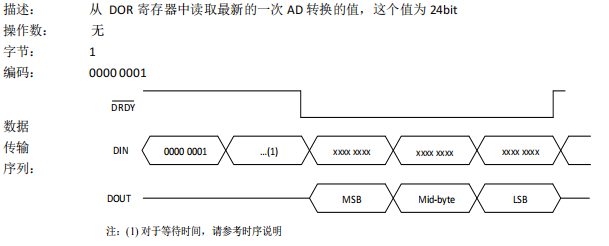

RDATA-讀數據模式

如有需求請聯系——三亞微科技王子文(16620966594)

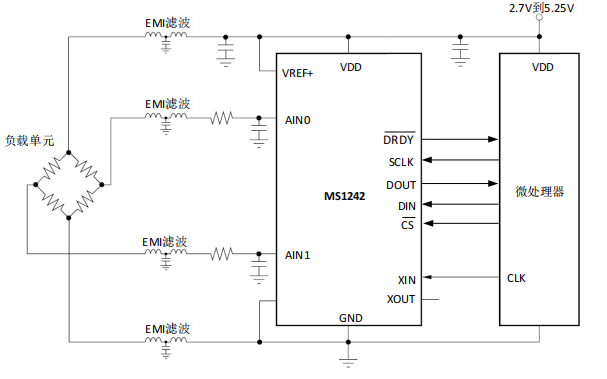

典型應用圖

下圖是 MS1242 在普通精度重量計的典型應用圖:

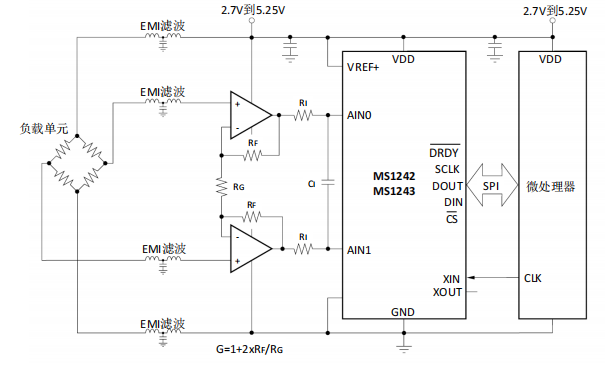

下圖是 MS1242/MS1243 在高精度重量計的典型應用圖:

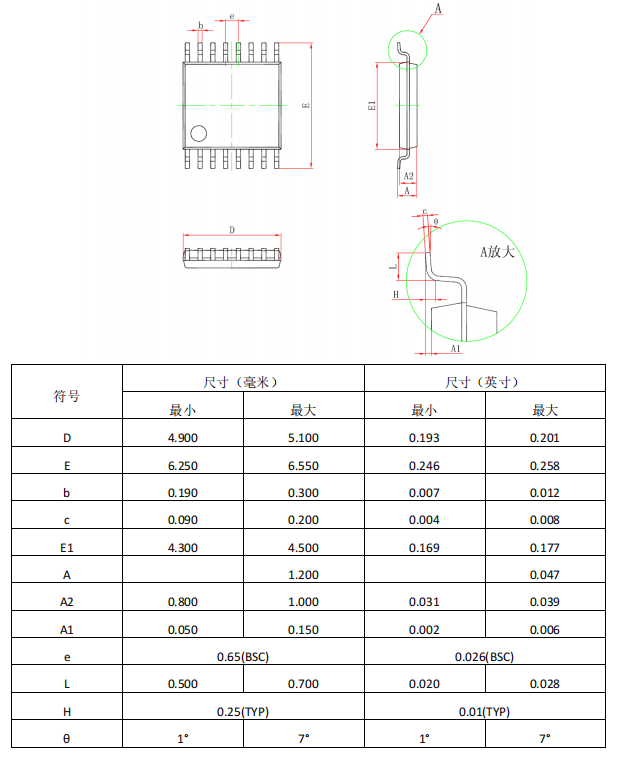

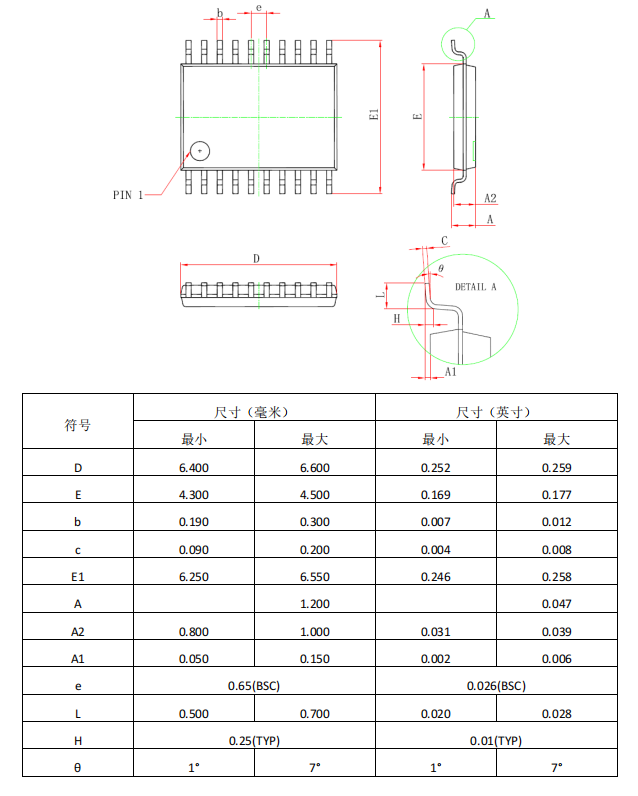

封裝外形圖

TSSOP16

TSSOP20

審核編輯 黃宇

——愛研究芯片的小王

-

高精度

+關注

關注

1文章

527瀏覽量

25526 -

模數轉換器

+關注

關注

26文章

3218瀏覽量

127014 -

低功耗

+關注

關注

10文章

2418瀏覽量

103895

發布評論請先 登錄

相關推薦

MS9280——10bit、35MSPS 模數轉換器

MS5185T——三通道、低噪聲、低功耗 20 位∑-Δ ADC

MS5180T——低噪聲、低功耗、24 位 ∑-Δ ADC

MS5110S——16-bit 內置基準模數轉換器

MS5112M——16-bit 多輸入內置基準模數轉換器

MS1112——16-bit 多輸入內置基準模數轉換器

MS1242/MS1243——24bit 高精度、低功耗模數轉換器

MS1242/MS1243——24bit 高精度、低功耗模數轉換器

評論