最近,科學(xué)家們首次制造出一種非硅制成的柔性可編程芯片。

據(jù)IEEE報(bào)道,英國(guó)Pragmatic Semiconductor 公司及其同事研發(fā)的新型超低功耗 32 位微處理器可以在彎曲時(shí)運(yùn)行,并可運(yùn)行機(jī)器學(xué)習(xí)工作負(fù)載。該微芯片的開(kāi)源 RISC-V 架構(gòu)表明其成本可能不到一美元,使其能夠?yàn)榭纱┐?a target="_blank">醫(yī)療電子產(chǎn)品、智能包裝標(biāo)簽和其他廉價(jià)物品供電,其發(fā)明者補(bǔ)充道。

例如,“我們可以開(kāi)發(fā)一種心電圖貼片,該貼片在胸部安裝有柔性電極,并在柔性電極上連接有柔性微處理器,通過(guò)處理患者的心電圖數(shù)據(jù)來(lái)對(duì)心律失常進(jìn)行分類(lèi),”英國(guó)劍橋柔性芯片制造商 Pragmatic 的處理器開(kāi)發(fā)高級(jí)總監(jiān) Emre Ozer 說(shuō)道。他表示,檢測(cè)正常心律與心律失常“是一項(xiàng)機(jī)器學(xué)習(xí)任務(wù),可以在柔性微處理器的軟件中運(yùn)行”。

柔性電子產(chǎn)品具有與軟材料相互作用的任何應(yīng)用的潛力,例如佩戴在身上或植入體內(nèi)的設(shè)備。這些應(yīng)用可能包括皮膚上的計(jì)算機(jī)、軟機(jī)器人和腦機(jī)接口。但是,傳統(tǒng)電子產(chǎn)品是由硅等剛性材料制成的。

開(kāi)源、靈活、速度足夠快

Pragmatic 公司致力于開(kāi)發(fā)一種柔性微芯片,其制造成本遠(yuǎn)低于硅處理器。這款新設(shè)備名為 Flex-RV,是一款基于金屬氧化物半導(dǎo)體氧化銦鎵鋅 (IGZO ) 的 32 位微處理器。

嘗試用硅制造柔性設(shè)備需要對(duì)易碎的微芯片進(jìn)行特殊封裝,以保護(hù)它們免受彎曲和拉伸的機(jī)械應(yīng)力。相比之下,用 IGZO 制成的柔性薄膜晶體管可以直接在低溫下在柔性塑料上制造,從而降低成本。

新的微芯片基于RISC-V指令集。(RISC 代表精簡(jiǎn)指令集計(jì)算機(jī)。)RISC-V 于 2010 年首次推出,旨在通過(guò)精簡(jiǎn)處理器可執(zhí)行的核心指令集來(lái)實(shí)現(xiàn)更小、更低功耗、性能更好的處理器。

“我們的最終目標(biāo)是通過(guò)開(kāi)發(fā)免許可的微處理器來(lái)實(shí)現(xiàn)計(jì)算的普及,”O(jiān)zer說(shuō)。

RISC-V 既免費(fèi)又開(kāi)源,讓芯片設(shè)計(jì)人員可以避免與 x86 和 Arm 等專(zhuān)有架構(gòu)相關(guān)的昂貴許可費(fèi)用。此外,專(zhuān)有架構(gòu)提供的定制機(jī)會(huì)有限,因?yàn)樘砑有轮噶钔ǔJ艿较拗啤O啾戎拢琑ISC-V 鼓勵(lì)這種改變。

“我們?cè)谠O(shè)計(jì) Flex-RV 時(shí)選擇了Olof Kindgren 設(shè)計(jì)的Serv ... 作為開(kāi)源 32 位 RISC-V CPU,”O(jiān)zer 說(shuō)道。“Serv 是開(kāi)源社區(qū)中最小的 RISC-V 處理器。”

其他處理器也采用柔性半導(dǎo)體制造,例如 Pragmatic 的 32 位PlasticARM以及由伊利諾伊州工程師設(shè)計(jì)的超廉價(jià)微控制器。與這些早期設(shè)備不同,F(xiàn)lex-RV 是可編程的,可以運(yùn)行用 C 等高級(jí)語(yǔ)言編寫(xiě)的編譯程序。此外,RISC-V 的開(kāi)源性質(zhì)還讓研究人員為 Flex-RV 配備了可編程的機(jī)器學(xué)習(xí)硬件加速器,從而實(shí)現(xiàn)人工智能應(yīng)用。

每個(gè) Flex-RV 微處理器都有一個(gè) 17.5 平方毫米的核心和大約 12,600 個(gè)邏輯門(mén)。研究小組發(fā)現(xiàn) Flex-RV 的運(yùn)行速度可以達(dá)到 60 千赫茲,而功耗卻不到 6 毫瓦。

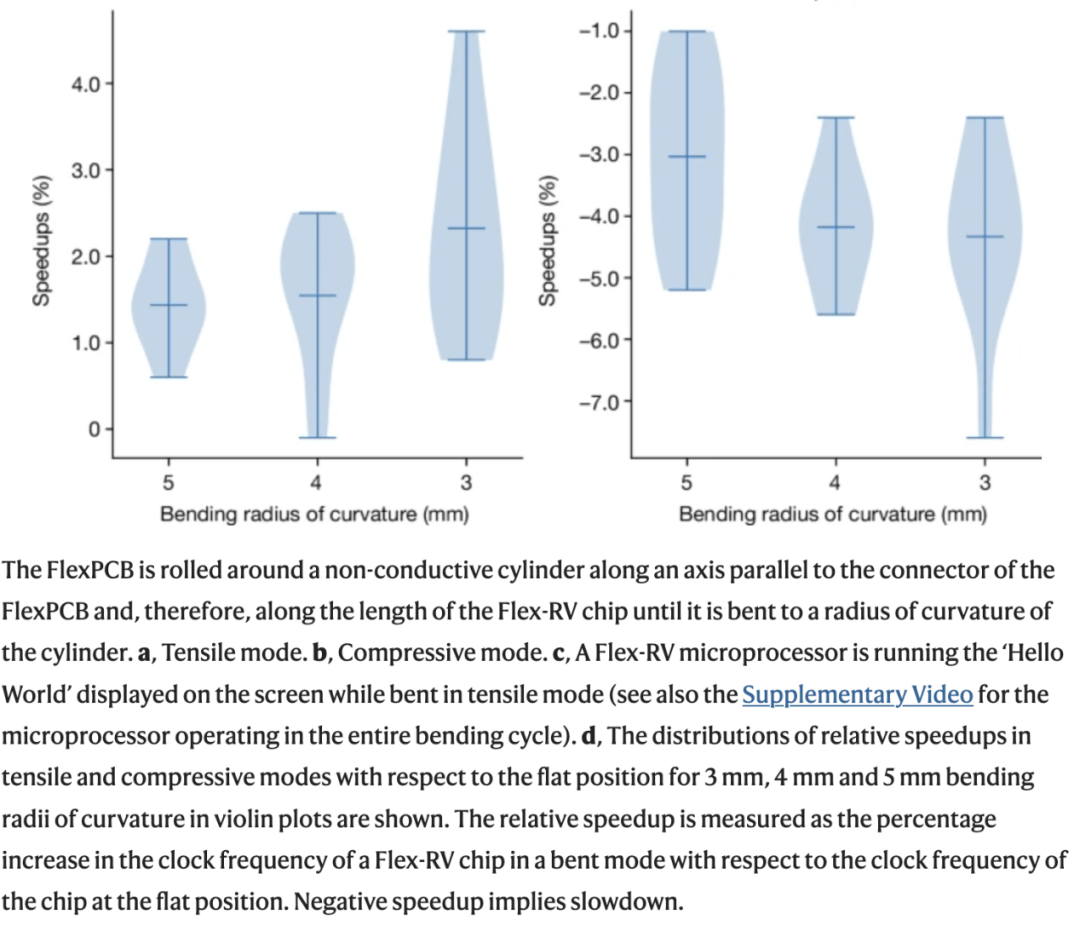

所有之前的柔性非硅微處理器都是在制造它們的晶圓上進(jìn)行測(cè)試的。相比之下,F(xiàn)lex-RV 是在柔性印刷電路板上進(jìn)行測(cè)試的,這讓研究人員能夠看到它在彎曲時(shí)的表現(xiàn)如何。Pragmatic 團(tuán)隊(duì)發(fā)現(xiàn),當(dāng)彎曲到半徑為 3 毫米的曲線時(shí),F(xiàn)lex-RV 仍然可以正確執(zhí)行程序。根據(jù)彎曲方式的不同,性能在 4.3% 的減速到 2.3% 的加速之間變化。“需要進(jìn)一步研究,以了解方向、方位和角度等彎曲條件如何影響宏觀和微觀尺度上的性能,”O(jiān)zer 說(shuō)。

硅微芯片可以以千兆赫的速度運(yùn)行,比 Flex-RV 快得多,但 Ozer 表示這應(yīng)該不是問(wèn)題。“柔性電子領(lǐng)域的許多傳感器(例如溫度、壓力、氣味、濕度、pH 值等)通常以赫茲或千赫茲的頻率運(yùn)行,運(yùn)行速度非常慢,”他說(shuō)。“這些傳感器用于智能包裝、標(biāo)簽和可穿戴醫(yī)療電子產(chǎn)品,這些是柔性微處理器將大有裨益的新興應(yīng)用。以 60 kHz 的頻率運(yùn)行微處理器足以滿(mǎn)足這些應(yīng)用的要求。”

Ozer 和他的團(tuán)隊(duì)認(rèn)為,每臺(tái) Flex-RV 的成本可能不到一美元。盡管 Ozer 不愿透露成本可能低于一美元多少,但他表示,他們相信如此低的成本是可能的,“這要?dú)w功于 Pragmatic 的低成本柔性芯片制造技術(shù)和免許可的 RISC-V 技術(shù)。”

以下為關(guān)于這項(xiàng)技術(shù)的論文全文翻譯:

半導(dǎo)體已經(jīng)對(duì)社會(huì)產(chǎn)生了非常深遠(yuǎn)的影響,加速了科學(xué)研究并推動(dòng)了更大的連通性。未來(lái)的半導(dǎo)體硬件將在量子計(jì)算、人工智能和邊緣計(jì)算方面開(kāi)辟新的可能性,用于網(wǎng)絡(luò)安全和個(gè)性化醫(yī)療等應(yīng)用。就其精神而言,開(kāi)放硬件為教育、學(xué)術(shù)研究和行業(yè)之間的更大合作和創(chuàng)新提供了機(jī)會(huì)。

這里我們介紹了 Flex-RV,這是一款基于開(kāi)放 RISC-V指令集的 32 位微處理器,采用銦鎵氧化鋅薄膜晶體管在柔性聚酰亞胺基板上制造,可實(shí)現(xiàn)超低成本可彎曲微處理器。Flex-RV 還在微處理器內(nèi)部集成了可編程機(jī)器學(xué)習(xí) (ML) 硬件加速器,并演示了擴(kuò)展 RISC-V 指令集以運(yùn)行 ML 工作負(fù)載的新指令。它經(jīng)過(guò)實(shí)現(xiàn)、制造和演示,運(yùn)行頻率為 60 kHz,功耗不到 6 mW。其組裝到柔性印刷電路板上時(shí)的功能在平坦和緊密彎曲條件下執(zhí)行程序時(shí)得到驗(yàn)證,平均性能變化不低于 4.3%。

Flex-RV 開(kāi)創(chuàng)了低于 1 美元的開(kāi)放標(biāo)準(zhǔn)非硅 32 位微處理器時(shí)代,并將使計(jì)算訪問(wèn)變得普及化,并解鎖可穿戴設(shè)備、醫(yī)療保健設(shè)備和智能包裝中的新興應(yīng)用。

文章重點(diǎn)

我們推出了 Flex-RV,這是一款基于開(kāi)源 32 位 RISC-V 中央處理單元 (CPU) 的 32 位 RISC-V 微處理器,并擴(kuò)展了機(jī)器學(xué)習(xí) (ML) 功能,采用銦鎵氧化鋅 (IGZO) 薄膜晶體管 (TFT) 制造,可為新興應(yīng)用提供超低成本且適應(yīng)性強(qiáng)的微處理器。

新興應(yīng)用尚未嵌入微處理器,例如快速消費(fèi)品(例如智能標(biāo)簽和包裝)、醫(yī)療保健可穿戴設(shè)備(例如智能貼片和敷料)、一次性醫(yī)療保健植入物(例如神經(jīng)接口)和一次性醫(yī)療保健測(cè)試條(例如橫向流動(dòng)測(cè)試、微流體)主要是因?yàn)槌杀竞屯庑纬叽纭3杀臼菍?shí)現(xiàn)這些應(yīng)用的決定性因素,特別是在智能標(biāo)簽和商品包裝中。

此外,就物理靈活性和可彎曲性而言,外形尺寸對(duì)于醫(yī)療保健可穿戴設(shè)備和植入物非常重要。這些新興應(yīng)用對(duì)速度和通信帶寬的計(jì)算要求并不高。這些應(yīng)用中的傳感器所需的數(shù)據(jù)采樣率不高于 200 Hz;在某些情況下,采樣率可以高達(dá) 1 kHz,因此以低時(shí)鐘頻率(例如 <100 kHz)工作的微處理器可以滿(mǎn)足應(yīng)用的計(jì)算要求。

50 多年來(lái),硅 (Si) 一直是開(kāi)發(fā)微處理器的基礎(chǔ)半導(dǎo)體技術(shù),在其發(fā)展道路上不斷改進(jìn)性能、面積、功耗和成本,這主要受到摩爾定律的推動(dòng)。在此期間,微處理器的速度從 kHz 提高到 GHz,因?yàn)榫w管的幾何尺寸從幾微米縮小到今天的 2-3 納米,低端微控制器的單位成本高達(dá)幾美元。然而,對(duì)于許多新興應(yīng)用來(lái)說(shuō),微處理器幾美元的單位成本是行不通的。單位成本無(wú)法降至不到 1 美元的水平有三個(gè)主要原因:(1) Si 晶圓廠的資本成本;(2) CPU 指令集、知識(shí)產(chǎn)權(quán) (IP) 許可和非經(jīng)常性工程 (NRE) 成本;以及 (3) 微處理器芯片封裝成本。

1.硅晶圓廠資本:

最先進(jìn)的硅制造廠需要數(shù)百萬(wàn)的資本投資,主要專(zhuān)注于先進(jìn)節(jié)點(diǎn)的高端微處理器(例如 2-3 納米)。低端微處理器(如嵌入式系統(tǒng)的微控制器)可以在較舊的傳統(tǒng)晶圓廠(>65 納米)中生產(chǎn),以最大限度地降低投資成本。然而,工廠在傳統(tǒng)晶圓廠的投資相對(duì)較少,這會(huì)導(dǎo)致運(yùn)營(yíng)和合規(guī)成本隨著時(shí)間的推移而增加,同時(shí)還會(huì)帶來(lái)環(huán)境問(wèn)題。

2.IP 許可和 NRE 成本:

每個(gè)微處理器都有一個(gè) CPU,它根據(jù)其特定的指令集架構(gòu) (ISA) 執(zhí)行程序,該架構(gòu)可以是專(zhuān)有的(例如,Intel 和 AMD 的 x86、Arm 的 ARMvX)或開(kāi)源的(即 RISC-V)。專(zhuān)有 ISA 提供了成熟的生態(tài)系統(tǒng),但許可成本高昂,并且由于添加新指令通常受到限制,因此提供的定制有限。替代方案包括許可現(xiàn)有 CPU(會(huì)產(chǎn)生前期 IP 成本),或開(kāi)發(fā)新的專(zhuān)有 ISA,這需要 CPU 設(shè)計(jì) NRE 成本和軟件工具集開(kāi)發(fā)費(fèi)用,這兩者都會(huì)增加單位成本。

3.芯片封裝:

硅芯片對(duì)環(huán)境條件(包括機(jī)械應(yīng)力)敏感。它們易碎,需要組裝到單獨(dú)的封裝(例如塑料、陶瓷)上以保護(hù)它們免受環(huán)境影響。芯片連接、組裝、封裝材料和封裝芯片測(cè)試的成本增加了微處理器的名義單位成本。此外,將剛性硅微處理器嵌入這些可穿戴或可植入設(shè)備之一具有挑戰(zhàn)性,因?yàn)槲⑻幚砥鞯男酒庋b將限制設(shè)備在剛性和厚度方面的能力。必須消除剛性芯片封裝材料,以降低微處理器的成本并使其在新興應(yīng)用中具有適應(yīng)性。

我們需要一種超低成本、可適應(yīng)并提供可接受性能的微處理器,以滿(mǎn)足新興應(yīng)用的要求。為了實(shí)現(xiàn)價(jià)格低于 1 美元且物理上靈活的微處理器,兩種支持技術(shù)可以幫助我們克服以前的限制:

1.RISC-V ISA:

必須將低于 1 美元的微處理器中 CPU 的 NRE 成本降至最低(例如,ISA/IP 許可)。RISC-V是一種開(kāi)放且免費(fèi)的 ISA 標(biāo)準(zhǔn),允許任何人開(kāi)發(fā)實(shí)現(xiàn) ISA 的 CPU,從而消除了 ISA 許可費(fèi),從而消除了微處理器開(kāi)發(fā)的 NRE 成本。此外,RISC-V 生態(tài)系統(tǒng)鼓勵(lì)創(chuàng)新,不限制修改或擴(kuò)展(例如,新指令),使設(shè)計(jì)人員能夠定制微處理器以滿(mǎn)足定制或應(yīng)用需求,而無(wú)需承擔(dān)額外成本或限制性許可的負(fù)擔(dān)。

2.IGZO TFT:

低于 1 美元的微處理器必須采用替代 Si 的半導(dǎo)體技術(shù)在比 Si 晶圓廠(包括傳統(tǒng)晶圓廠)便宜幾個(gè)數(shù)量級(jí)且碳足跡更少的晶圓廠中制造,其中的碳足跡是指芯片設(shè)計(jì)和制造過(guò)程中的二氧化碳排放量。

IGZO 是一種金屬氧化物半導(dǎo)體材料,可用于使用低溫光刻工藝在柔性聚酰亞胺基板上開(kāi)發(fā) TFT 。TFT 是通過(guò)在絕緣體基板上沉積半導(dǎo)體、電介質(zhì)和電極來(lái)制造的,而不是在剛性硅晶片上使用摻雜 Si 來(lái)開(kāi)發(fā) MOSFET(金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管)。

Pragmatic的FlexLogic晶圓廠可以制造由 IGZO TFT 制成的柔性芯片或 FlexIC ,與同等 Si 晶圓廠相比,每個(gè) FlexIC 的碳足跡要低幾個(gè)數(shù)量級(jí)。此外,F(xiàn)lexIC 不需要像 Si 芯片那樣使用額外的芯片封裝(例如塑料、陶瓷)來(lái)保護(hù)它們免受機(jī)械應(yīng)力,因?yàn)樗鼈儾灰姿椋梢缘挚箯澢葯C(jī)械應(yīng)力。這可以將微處理器的單位成本進(jìn)一步降低到低于 1 美元的水平,同時(shí)還具有彎曲功能。

之前曾有過(guò)基于柔性基板的非硅微處理器原型。早期的研究基于使用低溫多晶硅 TFT 和有機(jī)、混合氧化物和金屬氧化物 TFT 的 8 位 CPU 。在下文中,作者?介紹了 PlasticARM -第一款基于專(zhuān)有ARM ISA 的 32 位微處理器,該 ISA 使用基于 IGZO 的TFT。

PlasticARM不是可編程微處理器,其片上只讀存儲(chǔ)器中只運(yùn)行三個(gè)硬連線程序。雖然不是基于柔性基板,但展示了一種源自 RISC-V ISA 的 16 位 CPU,該 CPU 使用互補(bǔ)碳納米管晶體管在傳統(tǒng)硅晶片上構(gòu)建。除了非硅微處理器外,先前的研究已經(jīng)展示了使用在柔性基板上制造的 IGZO TFT 設(shè)計(jì)和實(shí)現(xiàn)的幾種ML ASIC(專(zhuān)用集成電路)。

Flex-RV 在三個(gè)方面不同于之前的非硅微處理器:(1)32 位微處理器是可編程的,可以運(yùn)行用高級(jí)語(yǔ)言(例如 C)編寫(xiě)的任意編譯程序。(2)RISC-V 的開(kāi)源性質(zhì)允許使用新指令擴(kuò)展 ISA,因此 Flex-RV 還具有可編程 ML 加速器,該加速器與 CPU 緊密耦合,并添加了自定義 RISC-V 指令。(3)我們通過(guò)使用為此工作開(kāi)發(fā)的創(chuàng)新技術(shù)(稱(chēng)為邊緣印刷或 OEP)將微處理器裸片組裝到柔性印刷電路板 (FlexPCB) 上,展示了微處理器在晶圓級(jí)測(cè)試之外的功能,而所有其他以前的工作都是在晶圓級(jí)上演示的,無(wú)需從玻璃載體上釋放并切割。

這樣,我們就可以在運(yùn)行程序的同時(shí)對(duì) Flex-RV 進(jìn)行物理彎曲測(cè)試,以驗(yàn)證其在機(jī)械應(yīng)力下的功能。我們演示了組裝到 FlexPCB 上的 Flex-RV 的功能,并在多個(gè)測(cè)試程序中量化了其性能。我們的結(jié)果表明,組裝在 FlexPCB 上的 Flex-RV 可以以高達(dá) 60 kHz 的速度運(yùn)行,同時(shí)功耗不到 6 mW,并且可以彎曲到曲率半徑小于 5 mm 時(shí)仍能正確執(zhí)行程序。

這項(xiàng)工作開(kāi)啟了下一代智能、普適計(jì)算的大門(mén),其中靈活、可編程的處理器與 ML 功能的集成將智能感知嵌入到日常物品中。

Flex-RV 系統(tǒng)架構(gòu)

我們使用開(kāi)源 Serv RISC-V CPU 來(lái)實(shí)現(xiàn)微處理器,這是迄今為止開(kāi)發(fā)的最小的開(kāi)源 RISC-V CPU 之一。Serv 是一種位串行 CPU,其中 32 位計(jì)算是逐位執(zhí)行的,而不是像更典型的 CPU 那樣并行執(zhí)行。這以犧牲性能為代價(jià)降低了 32 位 RISC-V 處理器的設(shè)計(jì)復(fù)雜性,其低設(shè)計(jì)復(fù)雜性是選擇 Serv 作為 Flex-RV 的 CPU 的主要原因。我們圍繞 Serv CPU 設(shè)計(jì)了一個(gè)簡(jiǎn)單的片上系統(tǒng) (SOC),以開(kāi)發(fā)可以與外界通信的微處理器。

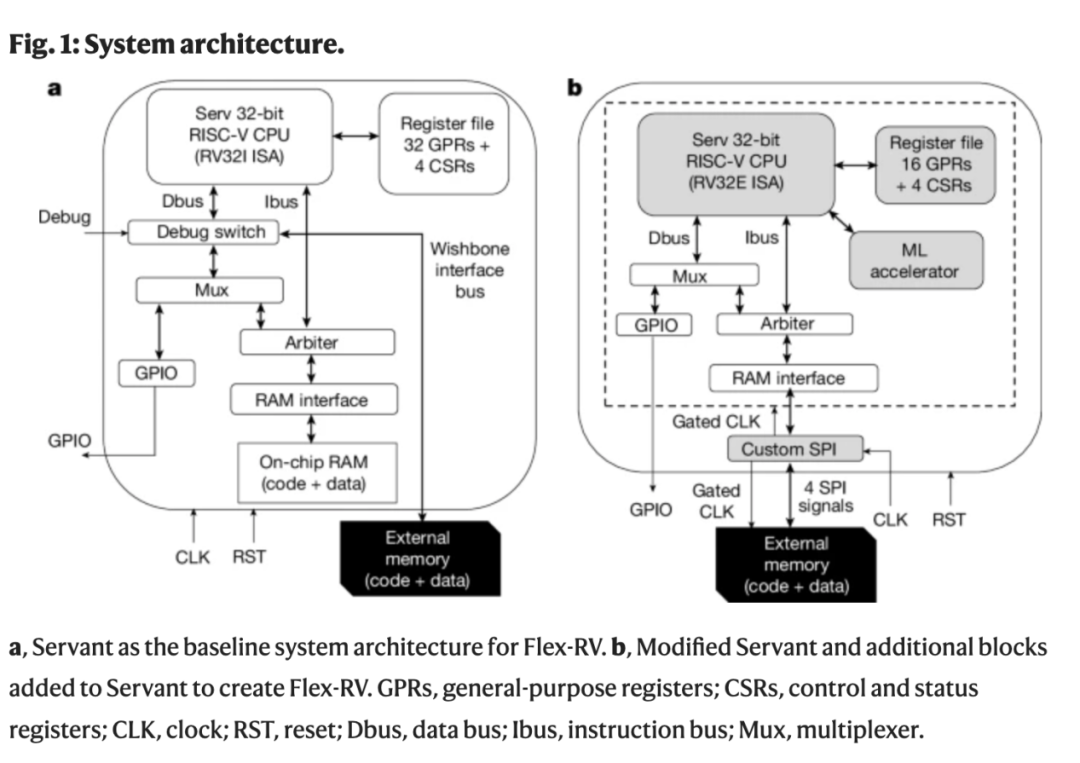

Flex-RV 被設(shè)計(jì)為一個(gè)簡(jiǎn)單的 SOC,由一個(gè) Serv RISC-V CPU 和附加外設(shè)組成。作為 Serv 參考平臺(tái)開(kāi)發(fā)的 Servant SOC 被用作 Flex-RV 的起點(diǎn)。如圖1a所示,Servant 包含 Serv CPU、寄存器文件 (RF)、調(diào)試開(kāi)關(guān)、多路復(fù)用器開(kāi)關(guān)、仲裁器、隨機(jī)存取存儲(chǔ)器 (RAM) 接口、片上 RAM 塊和通用輸入/輸出 (GPIO) 接口。Serv 支持 RISC-V RV32I ISA,它具有 32 個(gè)通用寄存器和 4 個(gè)額外的控制和狀態(tài)寄存器。代碼和數(shù)據(jù)通過(guò)調(diào)試開(kāi)關(guān)從外部存儲(chǔ)器加載到片上 RAM 中。GPIO 接口可用于與外部世界通信(例如顯示器)。

我們修改了 Servant 中的某些功能來(lái)開(kāi)發(fā) Flex-RV,如圖1b所示。例如,Serv 經(jīng)過(guò)修改以支持 RV32E ISA,它支持與 RV32I 相同的指令集,但僅使用前 16 個(gè)寄存器。我們刪除了調(diào)試開(kāi)關(guān)和片上 RAM。由于當(dāng)前的 FlexIC 技術(shù)出于面積/功率原因不允許我們放置相當(dāng)大的片上存儲(chǔ)器(例如,>1kB SRAM),我們選擇使用片外存儲(chǔ)器來(lái)訪問(wèn)代碼和數(shù)據(jù),因此添加了自定義串行外設(shè)接口 (SPI) 或 C-SPI 塊來(lái)與外部存儲(chǔ)器通信。C-SPI 塊從外部存儲(chǔ)器獲取 32 位 RISC-V 指令,并對(duì)存儲(chǔ)器執(zhí)行 32 位數(shù)據(jù)加載/存儲(chǔ)操作。使用 C-SPI 與外部存儲(chǔ)器通信而不是使用并行數(shù)據(jù)、地址和控制總線訪問(wèn)它的主要原因是為了減少片外焊盤(pán)的數(shù)量,從而簡(jiǎn)化將 Flex-RV 組裝到 FlexPCB 上的過(guò)程。C-SPI 塊的詳細(xì)信息(包括內(nèi)存事務(wù))可在方法中找到。

我們還設(shè)計(jì)了一個(gè)可編程的 ML 加速器,它是一個(gè) SIMD(單指令多數(shù)據(jù))引擎,用于加速當(dāng)代 ML 算法中常用的矩陣乘法和后處理操作。ML 加速器作為自定義功能單元 (CFU) 與 Serv 緊密耦合,并在 RV32E ISA 中添加了四條新指令,以便可以對(duì)加速器進(jìn)行編程。方法中描述了 ML 模型、加速器架構(gòu)、四條新指令和編程接口的詳細(xì)信息。

Flex-RV 已使用 RISC-V 架構(gòu)合規(guī)套件針對(duì) RV32E ISA 進(jìn)行了驗(yàn)證。還開(kāi)發(fā)了幾個(gè)測(cè)試基準(zhǔn)來(lái)驗(yàn)證其功能,這些基準(zhǔn)是用 C 語(yǔ)言編寫(xiě)的(帶有一些內(nèi)聯(lián)匯編代碼),并使用 RISC-V GNU 編譯器工具進(jìn)行編譯。測(cè)試基準(zhǔn)和編譯環(huán)境的詳細(xì)信息可以在方法中找到。

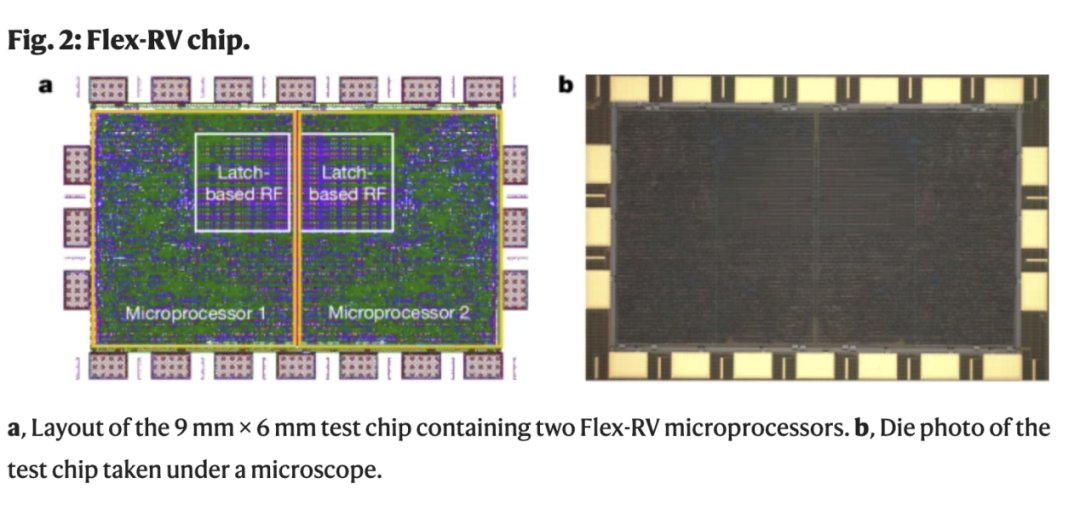

我們使用 Pragmatic 的 0.6 μm FlexIC 技術(shù)實(shí)現(xiàn) Flex-RV,該技術(shù)采用由 n 型 IGZO TFT 和電阻上拉組成的單極邏輯。芯片實(shí)現(xiàn)(即綜合、布局布線、靜態(tài)時(shí)序分析、布局布線后仿真和簽核)是使用商用電子設(shè)計(jì)自動(dòng)化 (EDA) 工具執(zhí)行的。RF 是一個(gè)雙端口陣列,具有一個(gè)讀端口和一個(gè)寫(xiě)端口,陣列大小為 20 × 32 位(或 80 字節(jié))。它使用布局鄰接方法通過(guò)鎖存器實(shí)現(xiàn),以增加陣列的密度(詳情請(qǐng)參閱方法 )。芯片的布局和芯片照片如圖2所示。測(cè)試芯片的芯片尺寸為 9 mm × 6 mm,有 20 個(gè)引腳,芯片中裝有兩個(gè) Flex-RV 微處理器。每個(gè) Flex-RV 微處理器的核心面積為 17.5 mm2 , NAND等效門(mén)數(shù)為 12,596,3 V 時(shí)的功耗為 5.8 mW。由于電阻上拉邏輯,5.8 mW 功耗主要是靜態(tài)的 (99%)。

測(cè)試芯片是在 Pragmatic 的 FlexLogic 晶圓廠中制造的,采用薄膜沉積工藝,在厚度為 30 μm 的 200 毫米聚酰亞胺晶圓上制造的,該工藝可創(chuàng)建金屬氧化物 TFT 和電阻器的圖案層,具有四個(gè)可布線的金屬層和一個(gè)額外的 RDL(重新分布層),用于將芯片的核心焊盤(pán)重新布線到將成為與外部世界接口的外圍焊盤(pán)。

測(cè)試基礎(chǔ)設(shè)施和結(jié)果

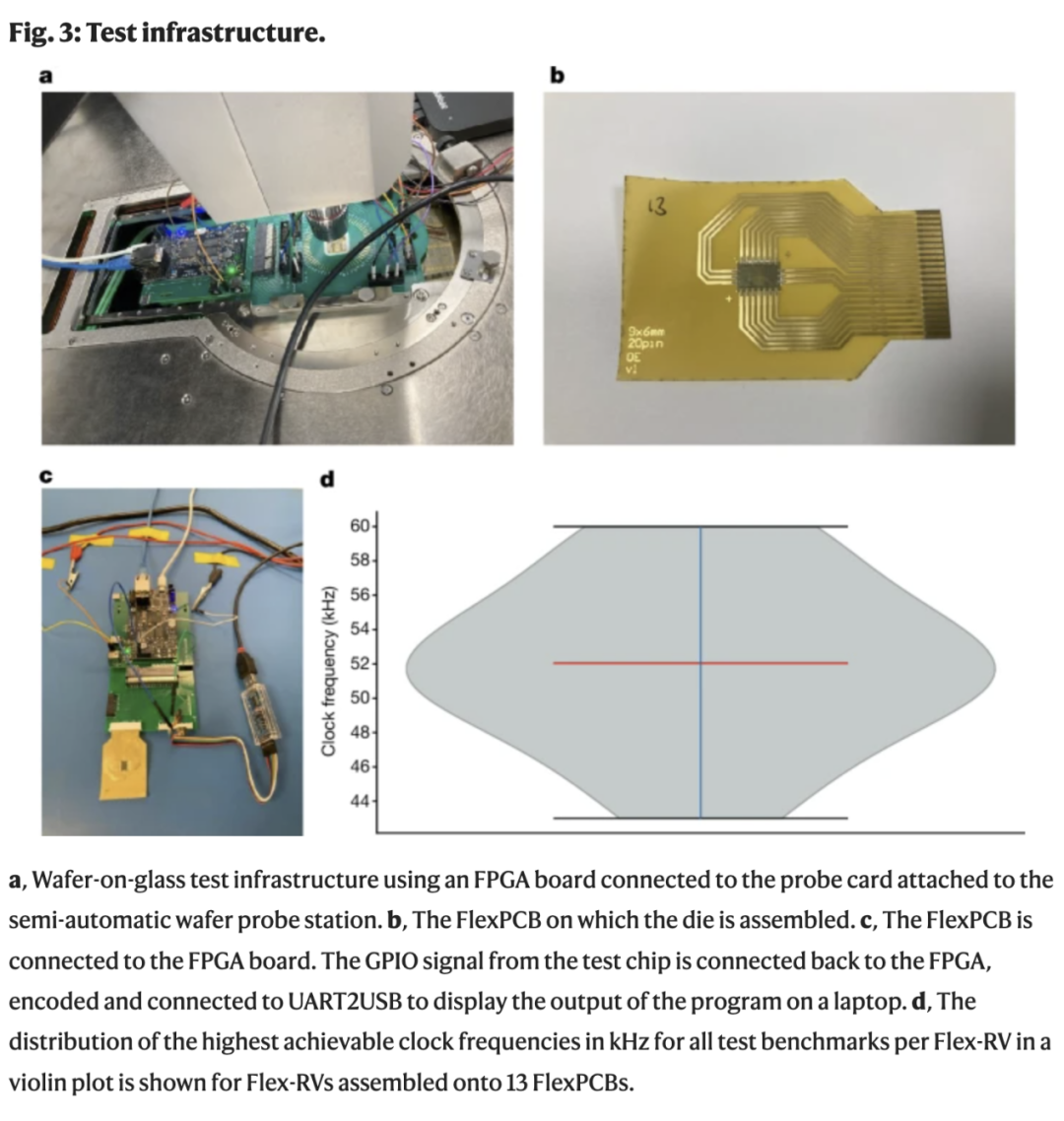

測(cè)試基礎(chǔ)設(shè)施由兩個(gè)完整階段組成:(1)玻璃晶圓測(cè)試和(2)FlexPCB 測(cè)試。

MicroZed Zynq-7000 現(xiàn)場(chǎng)可編程門(mén)陣列 (FPGA) 板用于測(cè)試 Flex-RV。FPGA 芯片經(jīng)過(guò)編程以模擬外部存儲(chǔ)器,并通過(guò)同樣在 FPGA 上實(shí)現(xiàn)的 SPI 塊與晶圓上的 Flex-RV 通信。編譯后的測(cè)試基準(zhǔn)的二進(jìn)制文件被加載到 FPGA 上的內(nèi)存中,F(xiàn)PGA 板重置測(cè)試芯片中的每個(gè) Flex-RV,然后它們開(kāi)始執(zhí)行每個(gè)內(nèi)核。測(cè)試基準(zhǔn)的結(jié)果通過(guò)每個(gè) Flex-RV 的 GPIO 引腳傳輸,該引腳通過(guò) FPGA 連接到個(gè)人計(jì)算機(jī) (PC) 的通用異步接收器-發(fā)送器 (UART) 接口,以在屏幕上顯示結(jié)果。FPGA 板還為每個(gè)測(cè)試芯片提供電源、時(shí)鐘和復(fù)位信號(hào)。

在第一階段,使用半自動(dòng)晶圓探針臺(tái)(圖3a)對(duì)晶圓上的測(cè)試芯片進(jìn)行功能測(cè)試,以識(shí)別功能正常的 Flex-RV。在第二階段,使用 OEP(一種為這項(xiàng)工作開(kāi)發(fā)的新組裝方法)將第一階段識(shí)別的功能正常的 Flex-RV 組裝到 FlexPCB 上(圖3b)。然后,組裝好的 FlexPCB 通過(guò) FPC 連接器連接到 FPGA 板(圖3c)。基于 FPGA 的測(cè)試基礎(chǔ)設(shè)施和 OEP 組裝過(guò)程的詳細(xì)信息可以在方法中找到。

圖3d顯示了測(cè)試芯片中的 Flex-RV 微處理器在 13 個(gè)組裝的 FlexPCB 上運(yùn)行所有測(cè)試基準(zhǔn)時(shí)可達(dá)到的最高時(shí)鐘頻率(以千赫茲 (kHz) 為單位)的分布。13 個(gè) FlexPCB 上的平均和最大時(shí)鐘頻率分別為 52 kHz 和 60 kHz。

最后,我們?cè)跈C(jī)械應(yīng)力下驗(yàn)證了 Flex-RV 組裝的 FlexPCB 的功能,并測(cè)量了最高可實(shí)現(xiàn)時(shí)鐘頻率的變化。機(jī)械應(yīng)力是通過(guò)將每個(gè) FlexPCB 沿著與 FlexPCB 連接器平行的軸(也沿著 Flex-RV 的長(zhǎng)度)滾動(dòng)在非導(dǎo)電圓柱體上來(lái)實(shí)現(xiàn)的,直到測(cè)試芯片彎曲到圓柱體的曲率半徑。已知 IGZO TFT 可以彎曲到 3 毫米的曲率半徑而不會(huì)損壞,并且器件參數(shù)(例如遷移率和閾值電壓)在不同的應(yīng)變情況下會(huì)發(fā)生變化。但是,這些測(cè)試針對(duì)的是單個(gè) IGZO TFT 器件,而我們主要研究 FlexIC 級(jí)別的可彎曲性公差。

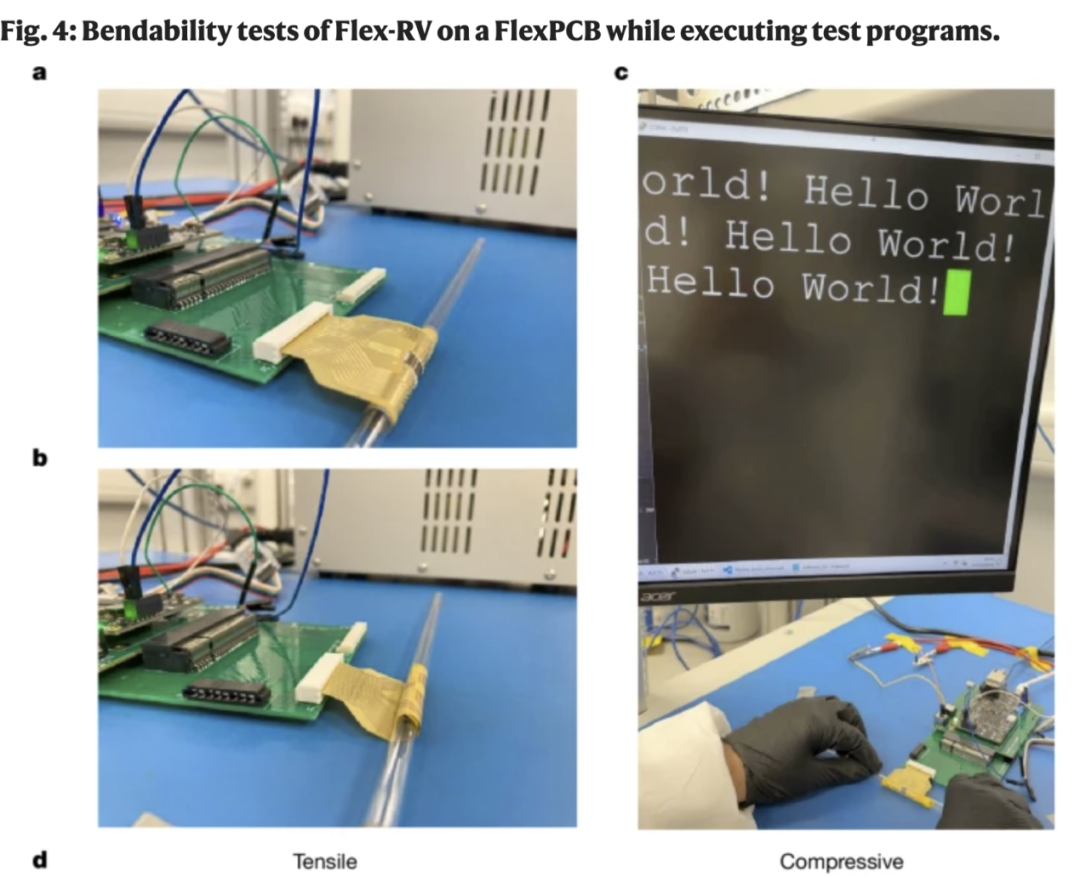

目前尚未有研究證明像 Flex-RV 這樣的復(fù)雜 FlexIC 單獨(dú)或在 FlexPCB 上組裝時(shí)通電運(yùn)行時(shí)的可彎曲性。我們使用三個(gè)不同的圓柱體(半徑分別為 3 毫米、4 毫米和 5 毫米)證明了組裝在 FlexPCB 上的 Flex-RV 的可彎曲性,并在拉伸(即芯片的曲率向外)和壓縮(即芯片的曲率向內(nèi))模式下對(duì)其進(jìn)行測(cè)試,如圖4a、b分別所示。總共對(duì)包含九個(gè) Flex-RV 微處理器的七個(gè)組裝 FlexPCB 進(jìn)行了可彎曲性分析測(cè)試。這是一個(gè)動(dòng)態(tài)可彎曲性測(cè)試,因?yàn)樵谛酒械膬蓚€(gè) Flex-RV 微處理器都在運(yùn)行測(cè)試基準(zhǔn)時(shí),會(huì)滾動(dòng) FlexPCB 并彎曲 Flex-RV 芯片——圖4c中顯示了一個(gè)示例。

當(dāng) FlexPCB 平放時(shí),測(cè)試基準(zhǔn)開(kāi)始在微處理器上運(yùn)行。在程序運(yùn)行時(shí),F(xiàn)lexPCB/Flex-RV 會(huì)繞圓柱體彎曲至拉伸模式,然后恢復(fù)至平坦?fàn)顟B(tài)。接下來(lái),它們會(huì)彎曲至壓縮模式,然后再恢復(fù)至平坦?fàn)顟B(tài)。每個(gè) FlexPCB 上的 Flex-RV 微處理器都會(huì)重復(fù)此操作兩次。

圖4d顯示了在三個(gè)不同彎曲半徑下彎曲實(shí)驗(yàn)的加速結(jié)果。在動(dòng)態(tài)彎曲測(cè)試期間,當(dāng)芯片處于拉伸或壓縮模式時(shí),在每個(gè) Flex-RV 微處理器上運(yùn)行測(cè)試基準(zhǔn)直至完成。我們?cè)诶旎驂嚎s模式下測(cè)量 Flex-RV 微處理器在所有測(cè)試基準(zhǔn)中可實(shí)現(xiàn)的最高時(shí)鐘頻率,并將其與平坦時(shí)可實(shí)現(xiàn)的最高時(shí)鐘頻率進(jìn)行比較,即時(shí)鐘頻率的加速。我們的結(jié)果表明,當(dāng)每個(gè)微處理器回到其最高可實(shí)現(xiàn)時(shí)鐘頻率時(shí),即在兩個(gè)平坦位置、兩個(gè)拉伸和壓縮模式之間,F(xiàn)lex-RV 微處理器表現(xiàn)出靈活性。

我們還觀察到兩種趨勢(shì):(1) Flex-RV 在拉伸模式下運(yùn)行速度更快,但在壓縮模式下運(yùn)行速度更慢,這歸因于設(shè)備(即 TFT 和電阻器)和導(dǎo)線參數(shù)(例如電阻和電容)的變化。(2) 隨著曲率半徑的減小,其在拉伸模式下的性能會(huì)提高。這是因?yàn)殡S著芯片的拉伸力增加,器件和導(dǎo)線參數(shù)會(huì)按比例變化,從而提高 Flex-RV 的性能,而在壓縮模式下則相反。彎曲實(shí)驗(yàn)表明,F(xiàn)lex-RV 在 3 毫米的彎曲半徑下可以正常工作,并且平均而言,與平坦位置相比,F(xiàn)lex-RV 在拉伸模式下的運(yùn)行速度可以提高 2.3%,在壓縮模式下的運(yùn)行速度可以降低 4.3%。

結(jié)論

我們開(kāi)發(fā)了一款低于 1 美元、可彎曲且靈活的微處理器 Flex-RV,它采用基于 0.6 μm IGZO TFT 技術(shù)的非硅技術(shù),并支持開(kāi)放的 RISC-V 指令集。此外,我們?cè)?Flex-RV 中加入了可編程硬件加速器,以支持 ML 應(yīng)用。Flex-RV 在低成本、低環(huán)境足跡的 FlexLogic 晶圓廠中在厚度為 30 μm 的聚酰亞胺基板上制造,然后組裝到厚度為 45 μm 的 FlexPCB 上,構(gòu)建超薄計(jì)算系統(tǒng)。我們的實(shí)驗(yàn)結(jié)果表明,F(xiàn)lex-RV 的運(yùn)行速度可以高達(dá) 60 kHz,總功耗不到 6 mW,并且可以在低至 3 mm 的彎曲曲率半徑內(nèi)正常運(yùn)行,運(yùn)行程序時(shí)的性能變化范圍平均為加速 2.3% 到減速 4.3%。因此,它可以滿(mǎn)足快速消費(fèi)品、可穿戴設(shè)備和醫(yī)療保健設(shè)備中許多新興應(yīng)用的需求。

Flex-RV是構(gòu)建不依賴(lài)任何傳統(tǒng)電子元件的超低成本可彎曲計(jì)算機(jī)的重要里程碑。

-

芯片

+關(guān)注

關(guān)注

456文章

51164瀏覽量

427200 -

RISC-V

+關(guān)注

關(guān)注

45文章

2322瀏覽量

46586 -

柔性芯片

+關(guān)注

關(guān)注

0文章

6瀏覽量

3272

原文標(biāo)題:一款顛覆性的RISC-V芯片

文章出處:【微信號(hào):HXSLH1010101010,微信公眾號(hào):FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

關(guān)于RISC-V芯片的應(yīng)用學(xué)習(xí)總結(jié)

risc-v芯片在電機(jī)領(lǐng)域的應(yīng)用展望

基于risc-v架構(gòu)的芯片與linux系統(tǒng)兼容性討論

求推薦一款入門(mén)級(jí)risc-v開(kāi)發(fā)板

RISC-V Summit China 2024 青稞RISC-V+接口PHY,賦能RISC-V高效落地

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

rIsc-v的缺的是什么?

【RISC-V信息速遞】反X86和ARM壟斷?很多人低估了RISC-V的顛覆性

risc-v的mcu對(duì)RTOS兼容性如何

國(guó)產(chǎn)RISC-V芯片性能穩(wěn)定嗎?

為何什么risc-v芯片比arm的效率高

國(guó)產(chǎn)RISC-V MCU推薦

字節(jié)跳動(dòng)推出一款顛覆性視頻模型—Boximator

一款顛覆性的RISC-V芯片

一款顛覆性的RISC-V芯片

評(píng)論