學(xué)習(xí)如何在 MYIR 的 ZU3EG FPGA 開(kāi)發(fā)板上部署 Tiny YOLO v4,對(duì)比 FPGA、GPU、CPU 的性能,助力 AIoT 邊緣計(jì)算應(yīng)用。

一、為什么選擇 FPGA:應(yīng)對(duì) 7nm 制程與 AI 限制

在全球半導(dǎo)體制程限制和高端 GPU 受限的大環(huán)境下,F(xiàn)PGA 成為了中國(guó)企業(yè)發(fā)展的重要路徑之一。它可支持靈活的 AIoT 應(yīng)用,其靈活性與可編程性使其可以在國(guó)內(nèi)成熟的 28nm 工藝甚至更低節(jié)點(diǎn)的制程下實(shí)現(xiàn)高效的硬件加速。

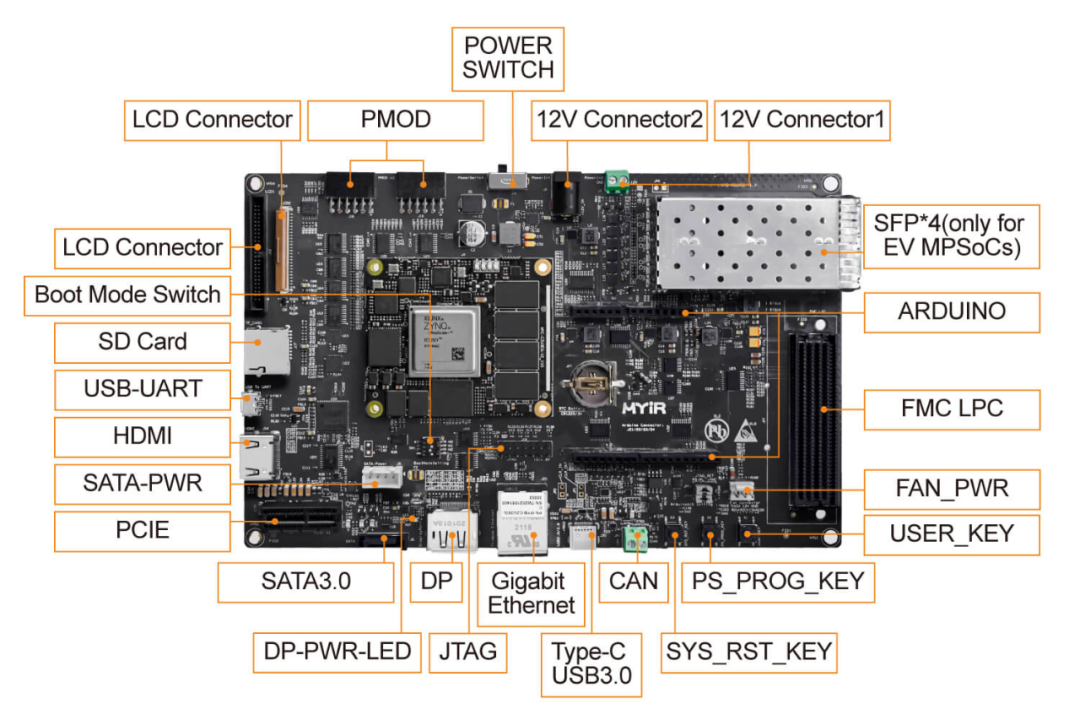

米爾的 ZU3EG 開(kāi)發(fā)板憑借其可重構(gòu)架構(gòu)為 AI 和計(jì)算密集型任務(wù)提供了支持,同時(shí)避免了 7nm 工藝對(duì)國(guó)產(chǎn)芯片設(shè)計(jì)的制約。通過(guò)在 ZU3EG 上部署 Tiny YOLO V4,我們可以為智能家居、智慧城市等 AIoT 應(yīng)用提供高效的解決方案。

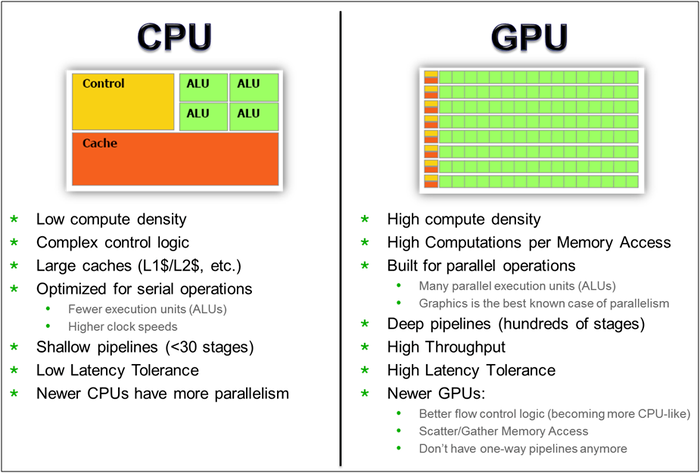

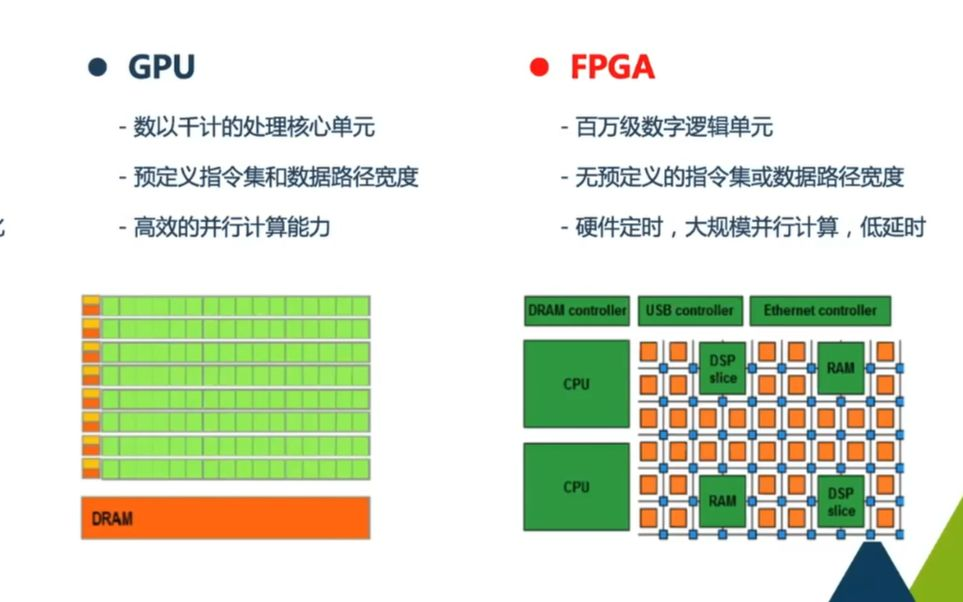

CPU GPU FPGA 架構(gòu)對(duì)比

二、了解 Tiny YOLO 模型及其適用性

YOLO(You Only Look Once)是一種實(shí)時(shí)物體檢測(cè)模型,它通過(guò)一次性掃描整個(gè)圖像,實(shí)現(xiàn)高效的對(duì)象識(shí)別。

而其簡(jiǎn)化版 Tiny YOLO V4 更適合嵌入式設(shè)備,具有較少的層數(shù)和參數(shù)。其輕量化特性更適合在資源受限的設(shè)備上運(yùn)行,尤其在低功耗、實(shí)時(shí)檢測(cè)的邊緣計(jì)算設(shè)備中表現(xiàn)出色。

相比傳統(tǒng) GPU,F(xiàn)PGA 能在小面積和低功耗下實(shí)現(xiàn)類(lèi)似的推理性能,非常契合 AIoT 應(yīng)用。像米爾 ZU3EG 這樣的 FPGA 開(kāi)發(fā)板,通過(guò)底板和豐富接口的載板設(shè)計(jì),非常適合高效的嵌入式低功耗數(shù)據(jù)處理。

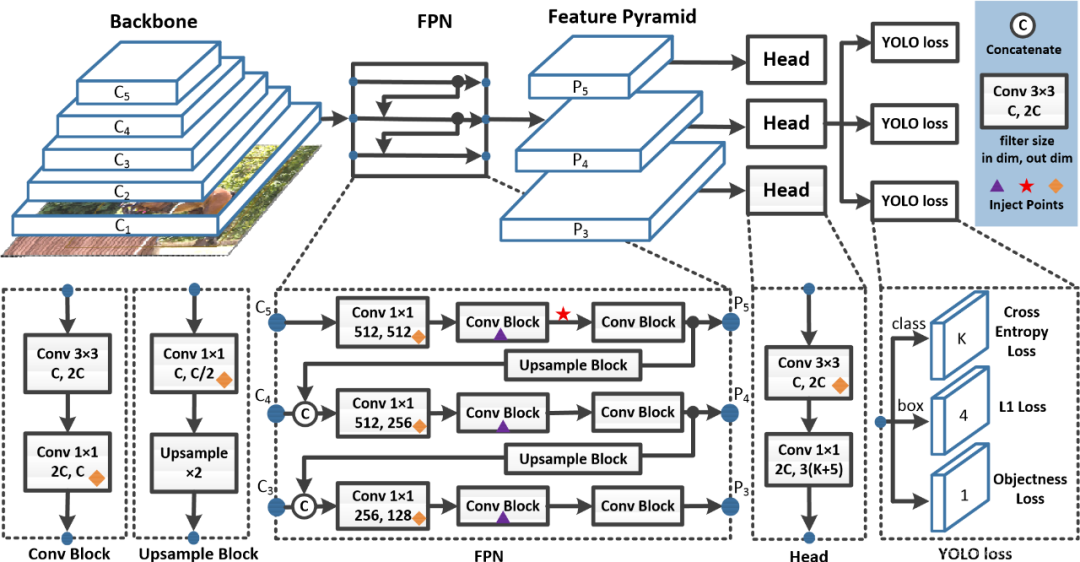

Yolo V4 網(wǎng)絡(luò)結(jié)構(gòu)圖

Tiny Yolo V4 網(wǎng)絡(luò)結(jié)構(gòu)圖

(通過(guò)優(yōu)化網(wǎng)絡(luò)結(jié)構(gòu)和參數(shù),保持較高檢測(cè)精度的同時(shí),降低模型的計(jì)算量和內(nèi)存占用)

三、獲取數(shù)據(jù)集和模型

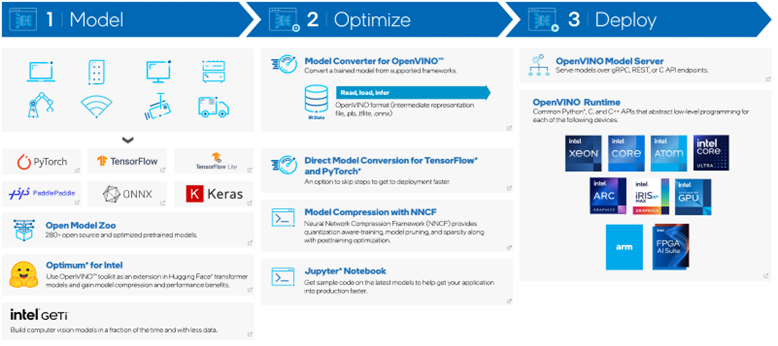

可下載開(kāi)源訓(xùn)練集或預(yù)訓(xùn)練模型。為了確保兼容性,建議將模型轉(zhuǎn)換為 ONNX 格式,以便后續(xù)能在 FPGA 上完成優(yōu)化。

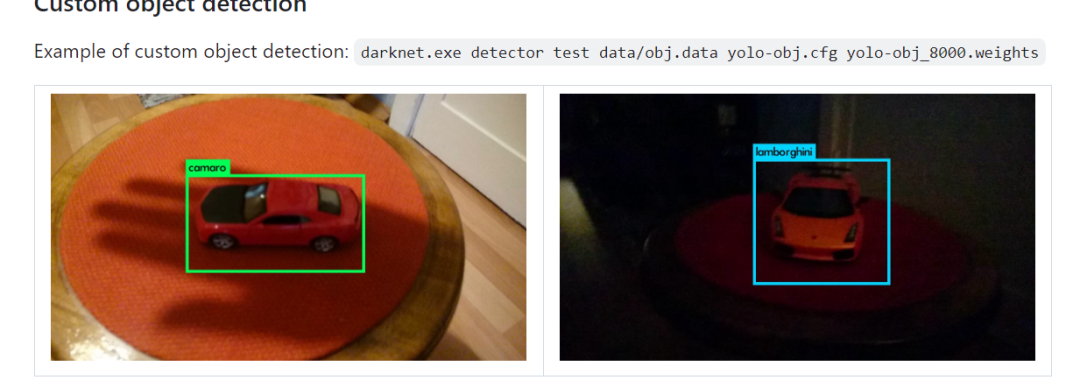

1.下載 Tiny YOLO V4 模型:從Darknet 的 GitHub 倉(cāng)庫(kù)獲取 Tiny YOLO 的預(yù)訓(xùn)練權(quán)重,或者在 COCO 等數(shù)據(jù)集上自行訓(xùn)練模型。自定義的模型適用于特定應(yīng)用場(chǎng)景(如車(chē)輛檢測(cè)、人臉檢測(cè)等)。

2.數(shù)據(jù)準(zhǔn)備:若要自定義模型,可使用 LabelImg 等工具對(duì)數(shù)據(jù)集進(jìn)行標(biāo)注,將數(shù)據(jù)轉(zhuǎn)為 YOLO 格式。之后,可將 YOLO 格式轉(zhuǎn)換為 ONNX 格式,以便兼容 FPGA 優(yōu)化工具鏈。

Tiny YOLO 在 Darknet 上訓(xùn)練的截圖

四、通過(guò) Vivado HLS 為 FPGA 準(zhǔn)備模型

要將模型部署到 FPGA,需要將神經(jīng)網(wǎng)絡(luò)操作轉(zhuǎn)換為硬件級(jí)描述。使用 Xilinx 的 Vitis HLS(高級(jí)綜合)可以將 Tiny YOLO v4 的 C++ 模型代碼的轉(zhuǎn)化為 Verilog RTL(寄存器傳輸級(jí))代碼,從而將模型從軟件世界帶入硬件實(shí)現(xiàn)。

詳細(xì)步驟:

1.模型層映射和優(yōu)化:

- 將 YOLO 的每一層(如卷積層、池化層)映射為硬件友好的 C/C++ 結(jié)構(gòu)。例如,將卷積映射為乘累加(MAC)數(shù)組,通過(guò)流水線實(shí)現(xiàn)并行化。

2.算子加速與指令優(yōu)化:

- 流水線(Pipelining):利用流水線來(lái)處理多項(xiàng)操作并行,減少延遲。

- 循環(huán)展開(kāi)(Loop Unrolling):展開(kāi)循環(huán),以每周期處理更多數(shù)據(jù),尤其在卷積操作中有效。

- 設(shè)置 DATAFLOW指令,使層間獨(dú)立處理。

3.量化與位寬調(diào)整:

- 將激活值和權(quán)重量化為定點(diǎn)精度(例如 INT8),而非浮點(diǎn)數(shù)。這在維持準(zhǔn)確度的同時(shí)顯著降低計(jì)算量,尤其適合 FPGA 的固定點(diǎn)運(yùn)算支持。

Tiny YOLO 模型在 Vivado HLS 中的層層轉(zhuǎn)化流程圖

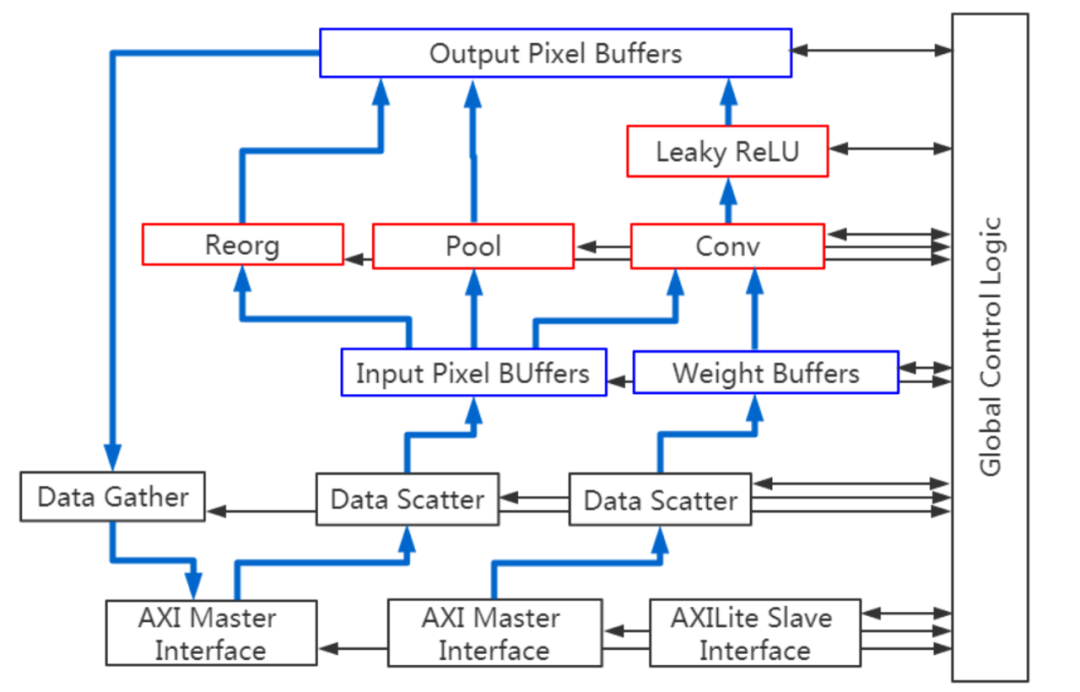

五、使用 Vivado 綜合與部署 Verilog 到 米爾的ZU3EG FPGA開(kāi)發(fā)板

當(dāng) HLS 生成的 RTL 代碼準(zhǔn)備就緒后,可以使用 Vivado 將模型部署到 FPGA。

1.Vivado 中的設(shè)置:

將 HLS 輸出的 RTL 文件導(dǎo)入 Vivado。

在 Vivado 中創(chuàng)建模塊設(shè)計(jì),包括連接AXI 接口與 ZU3EG 的 ARM 核連接。

2.I/O 約束與時(shí)序:

定義 FPGA 的 I/O 引腳約束,以匹配 ZU3EG 板的特定管腳配置。配置時(shí)鐘約束以滿足合適的數(shù)據(jù)速率(如視頻數(shù)據(jù) 100-200 MHz)。

進(jìn)行時(shí)序分析,確保延遲和響應(yīng)速度達(dá)到實(shí)時(shí)要求。

3.生成比特流并下載到 ZU3EG:

生成的比特流可以直接通過(guò) JTAG 或以太網(wǎng)接口下載到 ZU3EG。

將 Tiny YOLO 處理模塊連接到 米爾ZU3EG開(kāi)發(fā)板 的外設(shè)和接口

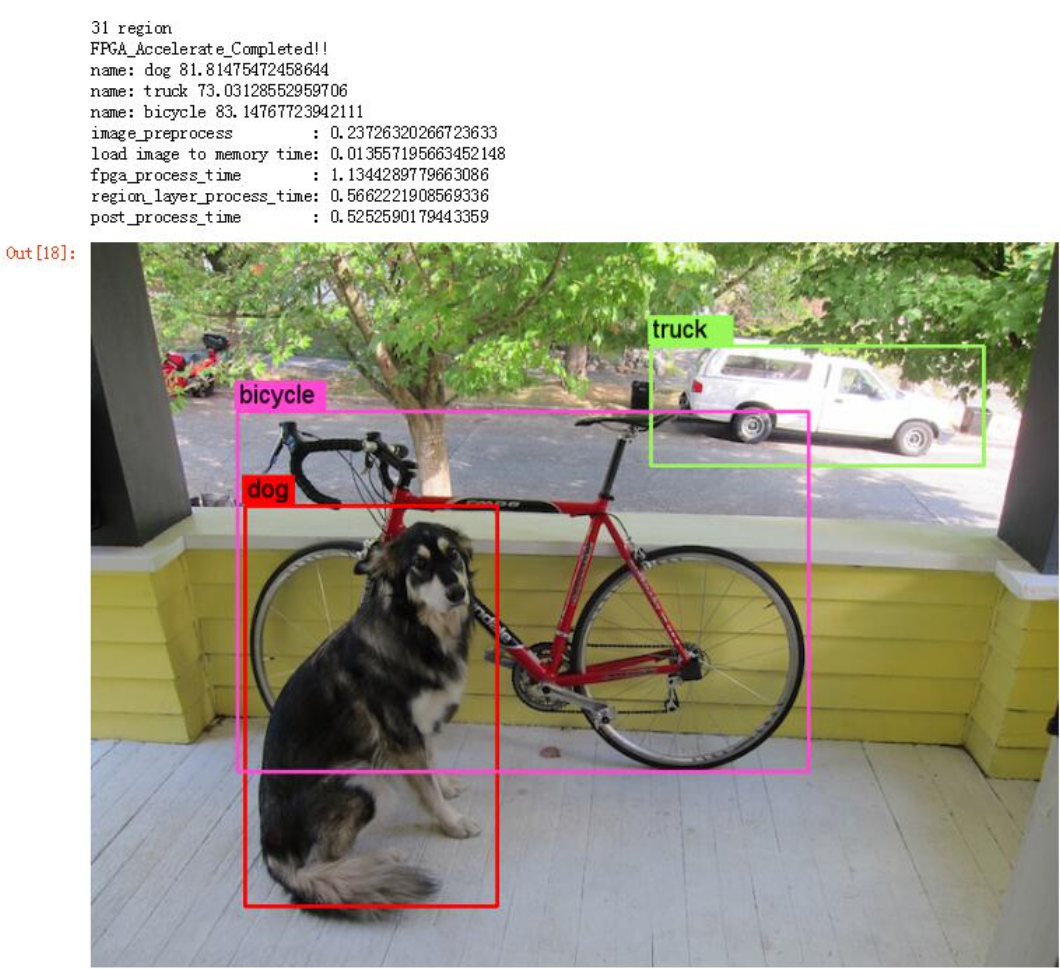

六、在 FPGA 上測(cè)試并運(yùn)行推理

現(xiàn)在 Tiny YOLO 已部署,可以驗(yàn)證其實(shí)時(shí)對(duì)象檢測(cè)性能。

1.數(shù)據(jù)采集:

- 通過(guò)連接的相機(jī)模塊捕捉圖像或視頻幀,或者使用存儲(chǔ)的測(cè)試視頻。

- 使用 ZU3EG 的 ARM 核上的 OpenCV 對(duì)幀進(jìn)行預(yù)處理,再將它們傳入 FPGA 預(yù)處理后進(jìn)行推理。

2.后處理與顯示:

- 模型檢測(cè)對(duì)象后,輸出邊框和類(lèi)別標(biāo)簽。使用 OpenCV 將邊框映射回原始幀,并在每個(gè)檢測(cè)到的對(duì)象周?chē)@示類(lèi)別和置信度。

3.性能測(cè)試:

- 測(cè)量幀速率(FPS)和檢測(cè)準(zhǔn)確度。微調(diào)量化位寬或數(shù)據(jù)流參數(shù),以優(yōu)化實(shí)時(shí)需求。

Tiny YOLO 模型在 ZU3EG 上顯示檢測(cè)結(jié)果的實(shí)時(shí)輸出,視頻幀中標(biāo)注了檢測(cè)到的對(duì)象

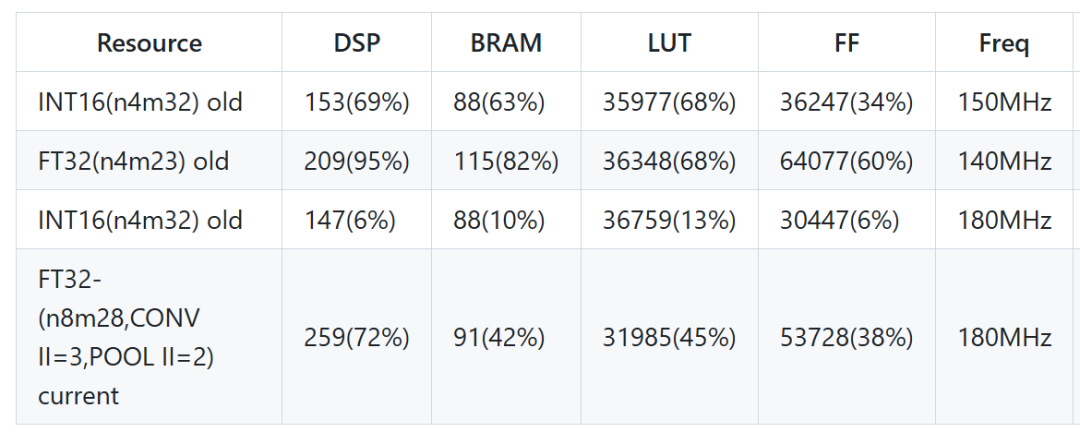

七、性能優(yōu)化與調(diào)試技巧

為提高性能,可以進(jìn)行以下調(diào)整:

- 內(nèi)存訪問(wèn):設(shè)計(jì)數(shù)據(jù)存儲(chǔ)方式,最大限度利用緩存并減少數(shù)據(jù)傳輸,降低內(nèi)存瓶頸。

- 降低延遲:重新評(píng)估關(guān)鍵路徑延遲。若延遲過(guò)高,調(diào)整 Vitis HLS 中的流水線深度,并驗(yàn)證層間的數(shù)據(jù)依賴性。

- 量化改進(jìn):嘗試 INT8 量化。Xilinx 的 Vitis AI 可幫助微調(diào)量化參數(shù),以平衡準(zhǔn)確性與速度。

不同優(yōu)化配置對(duì)資源使用的影響

米爾MYC-CZU3EG/4EV/5EV-V2核心板及開(kāi)發(fā)板

在MYIR 的 ZU3EG 開(kāi)發(fā)平臺(tái)上提供了一種高效的解決方案。利用 FPGA 獨(dú)特的靈活性和低功耗優(yōu)勢(shì),助力未來(lái) AIoT 設(shè)備的普及和智能升級(jí)。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605973 -

AIoT

+關(guān)注

關(guān)注

8文章

1418瀏覽量

30948 -

米爾電子

+關(guān)注

關(guān)注

0文章

113瀏覽量

498

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

米爾國(guó)產(chǎn)FPGA SoC芯選擇,安路飛龍DR1M90核心板重磅發(fā)布

國(guó)產(chǎn)高性能CPU--米爾瑞芯微RK3576賦能AIoT、工業(yè)、智能顯示終端

ADC12D1800RFRB開(kāi)發(fā)板上有一塊V4的FPGA,請(qǐng)問(wèn)此FPGA是負(fù)責(zé)AD數(shù)據(jù)采集嗎?

助力AIoT應(yīng)用:在米爾FPGA開(kāi)發(fā)板上實(shí)現(xiàn)Tiny YOLO V4

《DNK210使用指南 -CanMV版 V1.0》第四十一章 YOLO2物體檢測(cè)實(shí)驗(yàn)

《DNK210使用指南 -CanMV版 V1.0》第三十九章 YOLO2人臉檢測(cè)實(shí)驗(yàn)

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】+01.開(kāi)箱(zmj)

摩爾斯微電子榮獲2024年WBA行業(yè)大獎(jiǎng)最佳Wi-Fi創(chuàng)新獎(jiǎng)等多項(xiàng)殊榮

高密度互連,引爆后摩爾技術(shù)革命

使用OpenVINO C# API部署YOLO-World實(shí)現(xiàn)實(shí)時(shí)開(kāi)放詞匯對(duì)象檢測(cè)

特斯拉正積極測(cè)試其V4超級(jí)充電樁

在多FPGA集群上實(shí)現(xiàn)高級(jí)并行編程

“自我實(shí)現(xiàn)的預(yù)言”摩爾定律,如何繼續(xù)引領(lǐng)創(chuàng)新

X-CUBE-CRYPTOLIB V4庫(kù)文件無(wú)法添加,鏈接錯(cuò)誤的原因?

STM32 x 米爾共同推動(dòng)工業(yè)行業(yè)應(yīng)用創(chuàng)新

后摩爾時(shí)代的創(chuàng)新:在米爾FPGA上實(shí)現(xiàn)Tiny YOLO V4,助力AIoT應(yīng)用

后摩爾時(shí)代的創(chuàng)新:在米爾FPGA上實(shí)現(xiàn)Tiny YOLO V4,助力AIoT應(yīng)用

評(píng)論