人工智能(AI)近年來(lái)已廣泛應(yīng)用,并迅速成為一項(xiàng)具有變革性的技術(shù)。AI依托于機(jī)器學(xué)習(xí)(ML)算法,而這些算法需要強(qiáng)大的計(jì)算能力。傳統(tǒng)上,開(kāi)發(fā)者們依賴圖形處理器(GPU)來(lái)運(yùn)行這些ML算法。GPU最初為圖形渲染而設(shè)計(jì),但已證明在執(zhí)行人工智能所需的矩陣和向量運(yùn)算方面非常有效。然而,AI硬件領(lǐng)域的格局正在經(jīng)歷巨大變革。計(jì)算需求的日益復(fù)雜和對(duì)能效提升的需求促使一些專注于特定領(lǐng)域AI處理器的初創(chuàng)公司涌現(xiàn)。這些公司開(kāi)發(fā)的AI處理器針對(duì)ML算法進(jìn)行了架構(gòu)優(yōu)化,與通用GPU相比,它們的性能功耗比顯著提高。

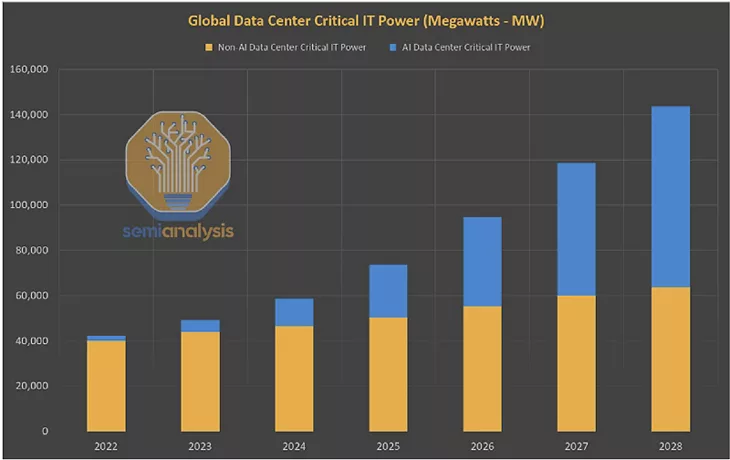

隨著AI技術(shù)的不斷發(fā)展,對(duì)更強(qiáng)計(jì)算能力和更高能效的需求將持續(xù)上升。根據(jù)Semianalysis的分析,預(yù)計(jì)到2028年,AI數(shù)據(jù)中心的電力需求將超過(guò)非AI數(shù)據(jù)中心,占全球數(shù)據(jù)中心總電力消耗的一半以上,而目前這一比例還不到20%。

▲圖1AI數(shù)據(jù)中心和非AI數(shù)據(jù)中心的電力需求

數(shù)據(jù)中心行業(yè)正在努力減輕電力負(fù)荷,逐步摒棄傳統(tǒng)的空氣冷卻方式,轉(zhuǎn)而采用成本較高但效果顯著的液冷技術(shù)。然而,單靠外部冷卻技術(shù)的進(jìn)步遠(yuǎn)遠(yuǎn)不夠。為了應(yīng)對(duì)不斷攀升的電力需求,人工智能硬件開(kāi)發(fā)商還需在系統(tǒng)設(shè)計(jì)層面進(jìn)行創(chuàng)新,深入挖掘全面的電力優(yōu)化策略。

新思科技Foundation IP如何推動(dòng)低功耗開(kāi)發(fā)

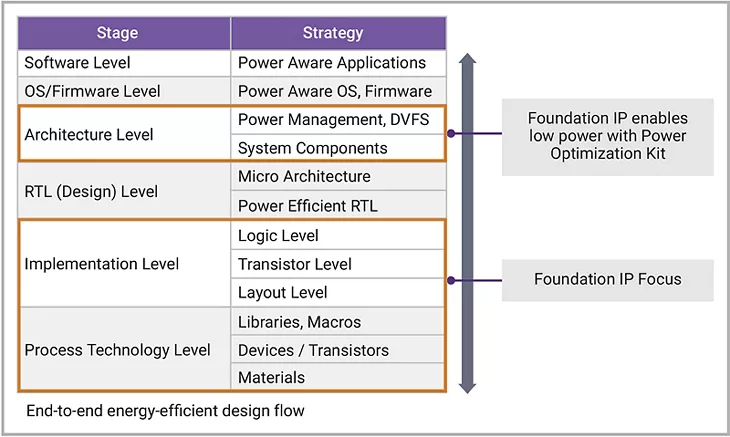

在設(shè)計(jì)系統(tǒng)級(jí)芯片(SoC)時(shí),開(kāi)發(fā)者可以在設(shè)計(jì)的不同階段,包括架構(gòu)層次、實(shí)現(xiàn)層次以及底層技術(shù)層次,進(jìn)行功耗優(yōu)化。新思科技Foundation IP能夠助力開(kāi)發(fā)者針對(duì)這些關(guān)鍵領(lǐng)域進(jìn)行優(yōu)化。SoC的功耗主要源于電路切換引起的動(dòng)態(tài)功耗以及漏電(或稱靜態(tài))功耗。動(dòng)態(tài)功耗在處理器執(zhí)行指令任務(wù)時(shí)產(chǎn)生,與CV2f成正比,這里的C代表開(kāi)關(guān)電容,V為工作電壓,f是電路時(shí)鐘頻率。無(wú)論處理器處于空閑還是活躍狀態(tài),漏電功耗都會(huì)發(fā)生,并且隨閾值電壓、晶體管尺寸和溫度而變化。在架構(gòu)層面,通過(guò)采用電源門(mén)控、動(dòng)態(tài)電壓頻率調(diào)整(DVFS)等電源管理技術(shù)來(lái)降低整體功耗。在實(shí)現(xiàn)和工藝技術(shù)層面,通過(guò)設(shè)計(jì)優(yōu)化以及對(duì)邏輯單元和嵌入式存儲(chǔ)器操作條件的精細(xì)管理,直接影響功耗。讓邏輯單元和存儲(chǔ)器在維持所需性能的前提下盡可能在更低電壓下工作,同時(shí)通過(guò)專門(mén)設(shè)計(jì)的單元減少活躍節(jié)點(diǎn)上的電容,這些都能顯著促進(jìn)功耗的降低。

新思科技憑借多代Foundation IP優(yōu)化積累的深厚經(jīng)驗(yàn)和強(qiáng)大能力,在AI SoC的功耗優(yōu)化中扮演著關(guān)鍵角色。新思科技Foundation IP提供的先進(jìn)解決方案包括經(jīng)過(guò)硅驗(yàn)證的高度優(yōu)化的邏輯庫(kù)、通用輸入輸出(GPIO)及嵌入式存儲(chǔ)器。新思科技的邏輯庫(kù)和IO與新思科技的電子設(shè)計(jì)自動(dòng)化(EDA)工具協(xié)同優(yōu)化,充分利用工藝技術(shù)的優(yōu)勢(shì),以實(shí)現(xiàn)功耗、性能和面積(PPA)的最佳平衡。新思科技的存儲(chǔ)器集成了針對(duì)機(jī)器學(xué)習(xí)算法的關(guān)鍵特性,為AI芯片帶來(lái)了顯著的面積及功耗節(jié)省。

▲圖2端到端的能效設(shè)計(jì)流程

讓我們深入探討新思科技Foundation IP如何幫助降低功耗,特別是針對(duì)AI處理器。

針對(duì)AI處理器的專用邏輯單元與新思科技存儲(chǔ)器的間距匹配

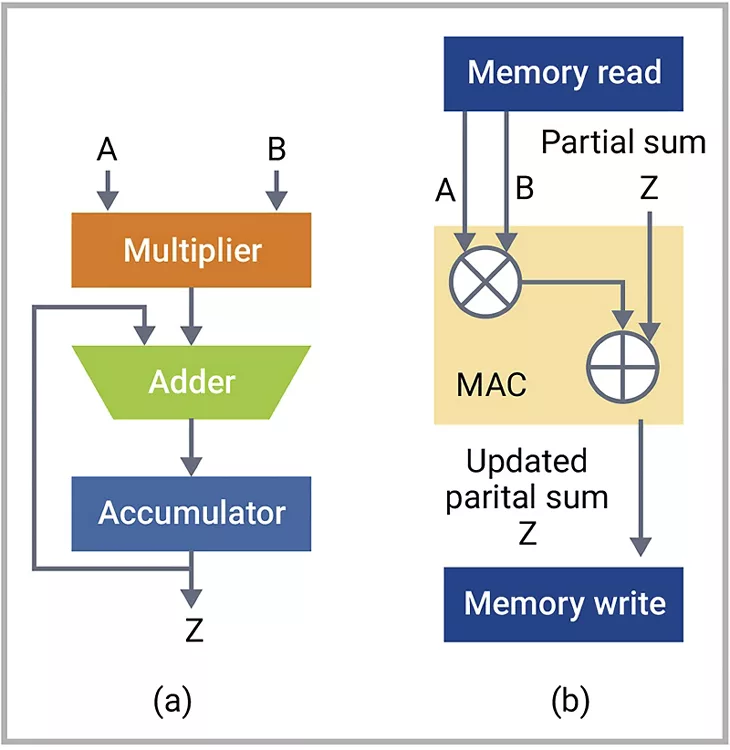

在AI處理器中,無(wú)論是訓(xùn)練還是推理任務(wù),大量的計(jì)算活動(dòng)(70-90%或更多)都致力于乘累加(MAC)操作,這是矩陣乘法和卷積的基礎(chǔ)。新思科技提供的邏輯庫(kù)包含了專為AI處理器設(shè)計(jì)的復(fù)雜邏輯,支持MAC功能。這些單元具備如融合乘加能力等特性,有助于減少設(shè)計(jì)的凈長(zhǎng)度和整體電容,從而顯著降低動(dòng)態(tài)功耗。對(duì)于AI芯片而言,集成高效能存儲(chǔ)器同樣重要。在機(jī)器學(xué)習(xí)模型中,特別是在推理任務(wù)中,參數(shù)權(quán)重存儲(chǔ)在存儲(chǔ)器中,并頻繁被MAC單元訪問(wèn)以進(jìn)行計(jì)算(見(jiàn)圖3)。新思科技提供了與MAC單元間距匹配的嵌入式存儲(chǔ)器。這意味著存儲(chǔ)器和邏輯單元的物理布局在尺寸和間距上進(jìn)行了協(xié)同優(yōu)化。這種集成設(shè)計(jì)策略帶來(lái)了更短的互連,某些應(yīng)用中已證明能減少33%的功耗。

▲圖3(a)MAC單元框圖(b)MAC單元的存儲(chǔ)器讀寫(xiě)

可定制的超低電壓庫(kù)

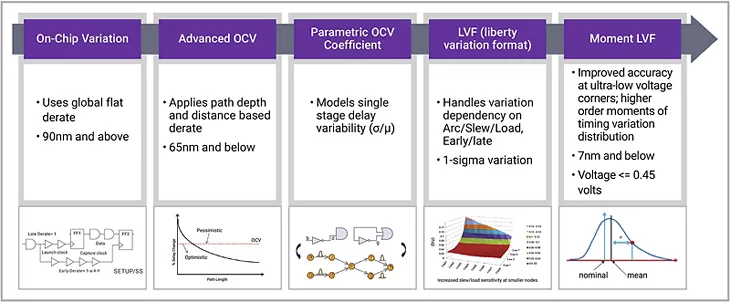

在先進(jìn)技術(shù)中,設(shè)計(jì)在超低供電電壓下運(yùn)行的芯片,特別是在0.5V以下,極具挑戰(zhàn)性,需要非常細(xì)致的設(shè)計(jì)和驗(yàn)證。然而,使用低供電電壓的功耗效益可能是巨大的,因?yàn)榻档碗妷簳?huì)對(duì)動(dòng)態(tài)功耗產(chǎn)生二次方減少效應(yīng)。AI處理器通常依賴于巨大的并行性來(lái)提高性能,不需要在高頻下運(yùn)行。它們特別可以從使用超低電壓庫(kù)中受益。新思科技通過(guò)其可定制的超低電壓邏輯庫(kù)支持低功耗芯片設(shè)計(jì)。這些庫(kù)基于高質(zhì)量和詳盡的驗(yàn)證,采用先進(jìn)的表征技術(shù),在廣泛的工藝、電壓和溫度(PVT)條件下進(jìn)行測(cè)試。低電壓帶來(lái)的挑戰(zhàn)包括降低的噪聲裕度和對(duì)制造變異的敏感性增加。隨著供電電壓的降低,信號(hào)改變電路下一階段狀態(tài)的能力減弱。這可能導(dǎo)致信號(hào)更像脈沖,通過(guò)電路傳播的時(shí)間更長(zhǎng)。這種延遲可能會(huì)影響電路的關(guān)鍵時(shí)序方面,包括建立時(shí)間和保持時(shí)間。為了解決這個(gè)問(wèn)題,開(kāi)發(fā)者應(yīng)考慮額外的因素,如軌到軌脈沖檢查、針對(duì)芯片內(nèi)變異(OCV)的額外時(shí)序裕度、保持時(shí)序的高西格瑪要求以及時(shí)鐘偏斜建議。新思科技Foundation IP的開(kāi)發(fā)者在開(kāi)發(fā)單元時(shí)會(huì)考慮到這些變異,單元會(huì)經(jīng)過(guò)高西格瑪蒙特卡羅模擬以進(jìn)行穩(wěn)健性驗(yàn)證,而謹(jǐn)慎使用基于矩的庫(kù)變異格式(LVF)允許對(duì)制造變異的概率特性進(jìn)行精確和詳細(xì)的建模

▲圖4低供電電壓導(dǎo)致的片上變異復(fù)雜性提升

具有分?jǐn)?shù)驅(qū)動(dòng)強(qiáng)度的邏輯單元

具有更高驅(qū)動(dòng)強(qiáng)度的邏輯單元消耗更多功耗,并且由于其更大的晶體管而傾向于有更高的漏電。對(duì)于非關(guān)鍵路徑,已經(jīng)通過(guò)使用高閾值電壓(VT)單元進(jìn)行了功耗優(yōu)化,可以通過(guò)使用具有分?jǐn)?shù)驅(qū)動(dòng)強(qiáng)度的單元來(lái)進(jìn)一步降低功耗。新思科技邏輯庫(kù)組合包括一系列這樣的分?jǐn)?shù)驅(qū)動(dòng)強(qiáng)度單元,包括驅(qū)動(dòng)強(qiáng)度小于一的單元。

功耗優(yōu)化套件

為了增強(qiáng)功耗節(jié)省,新思科技在其標(biāo)準(zhǔn)單元平臺(tái)中提供了功率優(yōu)化套件(POK)。該套件包括各種專用邏輯單元,旨在實(shí)現(xiàn)先進(jìn)的電源管理技術(shù)。這包括幫助減少靜態(tài)功耗的電源開(kāi)關(guān)和隔離單元,通過(guò)在不需要時(shí)啟用塊關(guān)閉。該套件還包括電平轉(zhuǎn)換器,通過(guò)允許不同塊根據(jù)其性能要求在不同的電壓下運(yùn)行,協(xié)助動(dòng)態(tài)功耗降低。此外,POK還具有多比特版本的隔離單元、保持觸發(fā)器和電平轉(zhuǎn)換器,有助于減少凈長(zhǎng)度和整體單元面積。

超低漏電IO

在具有AI芯片的SoC中,雖然片上組件在低電壓下運(yùn)行,但這些需要連接到在更高電壓下運(yùn)行的片外組件。設(shè)計(jì)支持如此電壓范圍的GPIO極具挑戰(zhàn)性,大多數(shù)公司轉(zhuǎn)而使用電平轉(zhuǎn)換器,給設(shè)計(jì)增加了不必要的面積和功耗。新思科技提供了一套全面的超低漏電IO,支持低至0.5V的電壓。這些相同的IO還支持1.8V IO供電,提高整體系統(tǒng)可靠性。具有AI芯片的SoC也更大,需要嚴(yán)格的靜電放電(ESD)保護(hù)標(biāo)準(zhǔn)。新思科技提供的IO解決方案包括強(qiáng)大的ESD保護(hù),能夠處理高達(dá)CDM 7A的電流。這轉(zhuǎn)化為更高效、可靠和具有成本效益的AI SoC設(shè)計(jì)。

非易失性存儲(chǔ)器和基于鎖存的存儲(chǔ)器

新思科技提供了一系列先進(jìn)的內(nèi)存解決方案,包括嵌入式磁阻隨機(jī)存取存儲(chǔ)器(MRAM)和電阻隨機(jī)存取存儲(chǔ)器(RRAM),它們提供的密度顯著高于傳統(tǒng)的SRAM。對(duì)于以讀取為主的應(yīng)用,例如存儲(chǔ)訓(xùn)練數(shù)據(jù),用MRAM或RRAM替換SRAM或片外DRAM可以顯著提高系統(tǒng)級(jí)PPA。這些非易失性存儲(chǔ)器(NVM)減少了硅面積和所需組件的數(shù)量。此外,由于它們不需要恒定功率來(lái)維持其數(shù)據(jù)狀態(tài)──與DRAM不同──它們消除了頻繁刷新周期的需要,從而降低了靜態(tài)功耗并減少了漏電流。新思科技還提供基于鎖存的存儲(chǔ)器,為較小的內(nèi)存實(shí)例節(jié)省了大量面積。這些對(duì)于特定的AI功能特別有用,如激活和池化,這些功能需要許多小的內(nèi)存實(shí)例。此外,新思科技提供了專門(mén)的多端口存儲(chǔ)器,能夠同時(shí)處理多個(gè)內(nèi)存訪問(wèn)請(qǐng)求,有助于緩解內(nèi)存瓶頸并提高整體性能。

存儲(chǔ)器中的稀疏性和轉(zhuǎn)置支持

在許多機(jī)器學(xué)習(xí)模型中,要計(jì)算的數(shù)據(jù)中有相當(dāng)一部分是零值字,可以在讀/寫(xiě)操作期間跳過(guò)以節(jié)省功率。為了利用這種數(shù)據(jù)稀疏性,新思科技在其存儲(chǔ)器中引入了一項(xiàng)名為WAZ(Word All Zero)的創(chuàng)新功能。該功能通過(guò)檢測(cè)并跳過(guò)零值,可以將功耗降低高達(dá)60%。此外,新思科技開(kāi)發(fā)了一種在存儲(chǔ)器中以轉(zhuǎn)置格式存儲(chǔ)數(shù)據(jù)的方法。這意味著矩陣元素在存儲(chǔ)器中對(duì)齊,以匹配其在計(jì)算期間的訪問(wèn)模式。結(jié)果,矩陣操作執(zhí)行更快,節(jié)省了能源,提高了整體效率。

總結(jié)

隨著應(yīng)用需求與AI技術(shù)的持續(xù)演進(jìn),開(kāi)發(fā)具備強(qiáng)大計(jì)算能力且高效節(jié)能的AI處理器已成為普遍需求。傳統(tǒng)的基于GPU架構(gòu)以及新興的優(yōu)化AI架構(gòu)正將能效推向極致。傳統(tǒng)上為CPU及早期GPU優(yōu)化的庫(kù)和存儲(chǔ)器方案,已難以滿足當(dāng)下AI SoC設(shè)計(jì)嚴(yán)苛且特定的需求。作為基礎(chǔ)IP領(lǐng)域的佼佼者,新思科技憑借二十余年的創(chuàng)新歷程,始終致力于最優(yōu)PPA的研發(fā),持續(xù)推出專業(yè)解決方案,以滿足半導(dǎo)體行業(yè)不斷變化且極具挑戰(zhàn)的設(shè)計(jì)需求。在強(qiáng)大的研發(fā)團(tuán)隊(duì)與技藝精湛的應(yīng)用工程師共同支持下,新思科技發(fā)揮其在邏輯庫(kù)、IO及嵌入式存儲(chǔ)器領(lǐng)域的深厚專長(zhǎng),提供獨(dú)具特色的可調(diào)解決方案,全面提升AI芯片的性能范疇。

-

處理器

+關(guān)注

關(guān)注

68文章

19404瀏覽量

231157 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7528瀏覽量

164335 -

AI

+關(guān)注

關(guān)注

87文章

31498瀏覽量

270296 -

人工智能

+關(guān)注

關(guān)注

1796文章

47643瀏覽量

240251

原文標(biāo)題:新思科技Foundation IP:AI芯片低功耗設(shè)計(jì)必選項(xiàng)

文章出處:【微信號(hào):Synopsys_CN,微信公眾號(hào):新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AN-1111: 使用ADuCM360/ADuCM361時(shí)的降低功耗選項(xiàng)

低功耗SOC芯片的優(yōu)勢(shì)

柵極驅(qū)動(dòng)芯片選型低功耗原因

新思科技發(fā)布全球領(lǐng)先的40G UCIe IP,助力多芯片系統(tǒng)設(shè)計(jì)全面提速

新思科技7月份行業(yè)事件

新思科技PCIe 7.0驗(yàn)證IP(VIP)的特性

新思科技攜手英特爾推出可量產(chǎn)Multi-Die芯片設(shè)計(jì)解決方案

新思科技面向英特爾代工推出可量產(chǎn)的多裸晶芯片設(shè)計(jì)參考流程,加速芯片創(chuàng)新

新思科技推出業(yè)界首款PCIe 7.0 IP解決方案

新思科技發(fā)布PCIe 7.0 IP解決方案,賦能AI與HPC前沿設(shè)計(jì)

新思科技推出業(yè)界首款PCIe 7.0 IP解決方案

TIDA-010053-使用原電池的智能儀表無(wú)線模塊低功耗選項(xiàng) PCB layout 設(shè)計(jì)

OTP低功耗語(yǔ)音芯片的工作原理與產(chǎn)品特性

新思科技Foundation IP:AI芯片低功耗設(shè)計(jì)必選項(xiàng)

新思科技Foundation IP:AI芯片低功耗設(shè)計(jì)必選項(xiàng)

評(píng)論