“Versal AI 引擎可以在降低功耗預(yù)算的情況下提高 DSP 計算密度,”高級產(chǎn)品營銷經(jīng)理 Udayan Sinha 表示。這種效率使 Versal AI 引擎能夠在嚴(yán)格的功耗預(yù)算內(nèi)處理最苛刻的 DSP 應(yīng)用。

AMD Versal AI 引擎使您能夠擴(kuò)展數(shù)字信號處理 (DSP) 計算和面向未來的設(shè)計,以適應(yīng)當(dāng)前和下一代計算密集型 DSP 應(yīng)用。借助 Versal AI 引擎,客戶可以期望以更低的功耗獲得高性能 DSP^1^以及更少的可編程邏輯資源。^2^

“Versal AI 引擎可以在降低功耗預(yù)算的情況下提高 DSP 計算密度,”高級產(chǎn)品營銷經(jīng)理 Udayan Sinha 表示。這種效率使 Versal AI 引擎能夠在嚴(yán)格的功耗預(yù)算內(nèi)處理最苛刻的 DSP 應(yīng)用。

可以從這些計算功能中受益的市場包括航空航天和國防、測試和測量、醫(yī)學(xué)成像/醫(yī)療保健,以及需要在 GSPS 吞吐量范圍內(nèi)運(yùn)行高吞吐量、實(shí)時 DSP 的其他市場。

利用 AMD Vitis? 統(tǒng)一軟件平臺,Versal AI 引擎設(shè)計可通過基于 C 語言的設(shè)計流程進(jìn)行編程。對于喜歡基于模型的流程的工程師,可以使用 Vitis Model Composer(MathWorks Simulink 的插件)。此外,一系列 DSP 庫函數(shù)、API 和增強(qiáng)型 IP 內(nèi)核支持快速開發(fā)高性能 DSP 設(shè)計。^?^

訪問 AMD GitHub,查看我們的 Versal AI 引擎 GitHub 設(shè)計教程和 DSP 庫。

從我們的網(wǎng)絡(luò)研討會系列開始,來自 AMD 的專家將介紹 Versal AI Engine 技術(shù),并演示如何使用它們來加速各種有價值的 DSP 算法。本網(wǎng)絡(luò)研討會系列的主題包括:

- Versal ACAP 和 AI 引擎技術(shù)簡介

- 使用 Versal AI 引擎加速多相通道選擇器設(shè)計

- 使用 Versal AI 引擎加速 FFT 算法

如需了解 Versal AI 引擎在頭對頭 DSP 基準(zhǔn)測試中與傳統(tǒng) HDL 實(shí)現(xiàn)方案的表現(xiàn),[請聯(lián)系您的銷售代表進(jìn)行基準(zhǔn)測試設(shè)計]。

總之,Versal AI 引擎可以通過降低動態(tài)功耗和可編程邏輯資源來加速高性能 DSP 應(yīng)用。如果您當(dāng)前的 DSP 應(yīng)用由于資源或功耗限制而遇到潛在的擴(kuò)展問題,那么 Versal AI 引擎是解鎖您當(dāng)前和下一代 DSP 計算能力的理想解決方案。

- 基于 AMD 于 2024 年 2 月委托進(jìn)行的第三方基準(zhǔn)測試,在信號處理應(yīng)用 FIR 實(shí)現(xiàn)中,對帶有 Vitis 的 Vitis 的 AMD Versal 自適應(yīng) SoC 與使用 Vivado 軟件和 Vitis Model Composer Tool 2023.1 版的傳統(tǒng)可編程邏輯進(jìn)行了比較。3 個設(shè)計的結(jié)果平均。結(jié)果會因設(shè)計規(guī)格而異。(版本 034)

- 基于 AMD 于 2024 年 2 月委托第三方進(jìn)行的基準(zhǔn)測試,在信號處理應(yīng)用 FIR 實(shí)現(xiàn)中,在采用 AMD Vitis 的 AMD Versal 自適應(yīng) SoC 上進(jìn)行 AI 設(shè)計工具,與使用 Vivado 軟件和 Vitis Model Composer 工具(2023.1 版)的傳統(tǒng)可編程軟件實(shí)現(xiàn)。4 個設(shè)計的結(jié)果平均。結(jié)果會因設(shè)計規(guī)格而異。(版本 035

-

dsp

+關(guān)注

關(guān)注

554文章

8059瀏覽量

350368 -

amd

+關(guān)注

關(guān)注

25文章

5492瀏覽量

134627 -

AI

+關(guān)注

關(guān)注

87文章

31498瀏覽量

270296 -

Versal

+關(guān)注

關(guān)注

1文章

163瀏覽量

7710

發(fā)布評論請先 登錄

相關(guān)推薦

貿(mào)澤開售適用于AI和機(jī)器學(xué)習(xí)應(yīng)用的 AMD Versal AI Edge VEK280評估套件

使用AMD Versal AI引擎加速高性能DSP應(yīng)用

AMD Alveo V80計算加速器網(wǎng)絡(luò)研討會

SpaceX星鏈衛(wèi)星終端用上AMD芯片,竟然還集成了Arm核心?

AMD第二代Versal自適應(yīng)SoC的主要特色

AMD發(fā)布第二代Versal自適應(yīng)SoC,AI嵌入式領(lǐng)域再提速

AMD Versal SoC刷新邊緣AI性能,單芯片方案驅(qū)動嵌入式系統(tǒng)

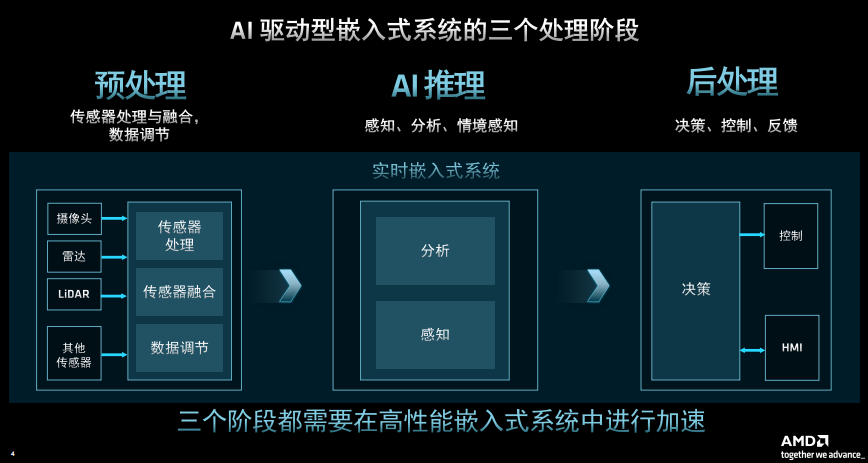

AMD推出第二代Versal器件,為AI驅(qū)動型嵌入式系統(tǒng)提供端到端加速

AMD Versal SoC全新升級邊緣AI性能,單芯片方案驅(qū)動嵌入式系統(tǒng)

AMD 以全新第二代 Versal 系列器件擴(kuò)展領(lǐng)先自適應(yīng) SoC 產(chǎn)品組合,為 AI 驅(qū)動型嵌入式系統(tǒng)提供端到端加速

在Vivado中構(gòu)建AMD Versal可擴(kuò)展嵌入式平臺示例設(shè)計流程

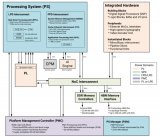

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計算加速平臺之 Versal 介紹(2)

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計算加速平臺之準(zhǔn)備工作(1)

AMD Versal AI Edge自適應(yīng)計算加速平臺之Versal介紹(2)

使用 AMD Versal AI 引擎釋放 DSP 計算的潛力

使用 AMD Versal AI 引擎釋放 DSP 計算的潛力

評論