歡迎來到《電源設計小貼士集錦》系列文章

本期,我們將聚焦于發生在 PFC 級的電流振蕩通過分析數字控制環路,了解潛在錯誤出現的原因并展示如何檢查控制固件中是否出現這種不穩定性。

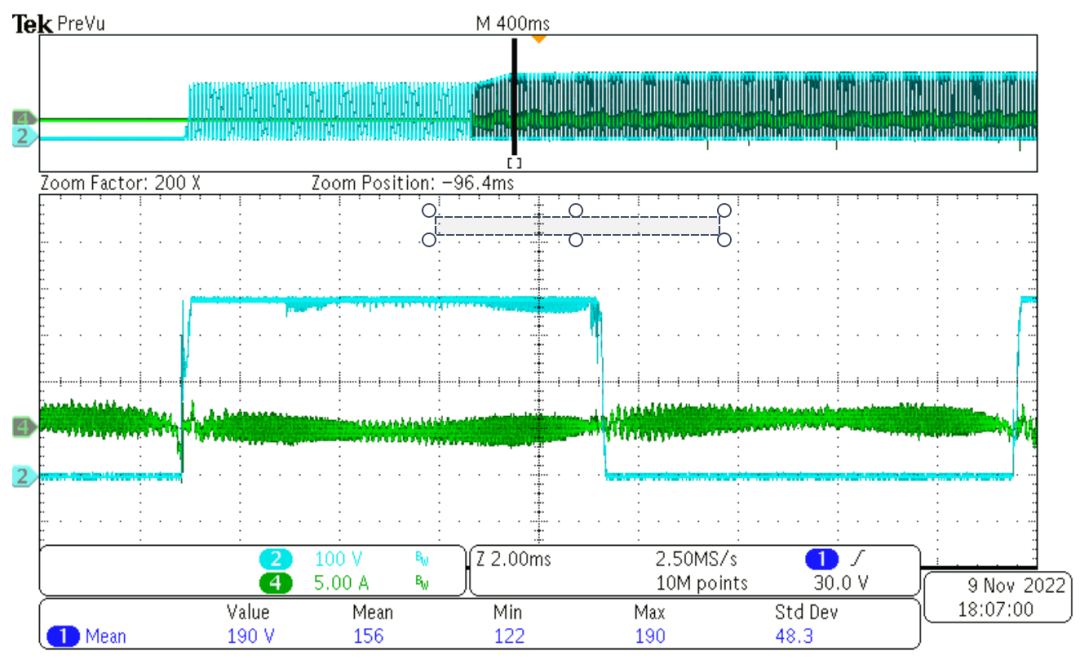

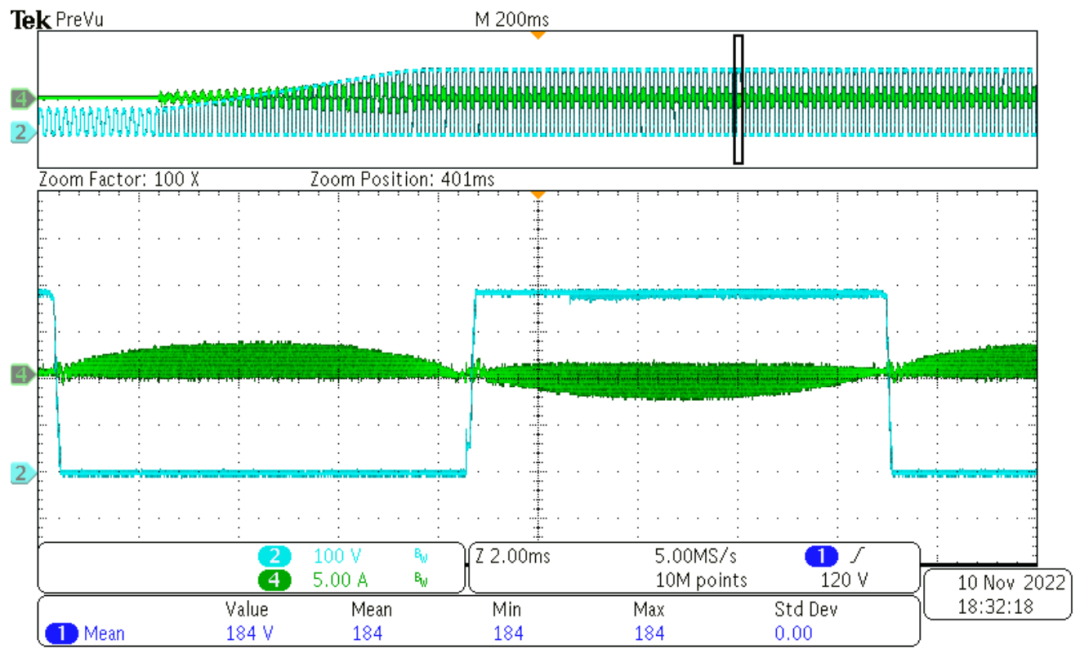

在設計諸如升壓功率因數校正 (PFC) 之類的數字電源時,您是否見過類似圖 1 中的電流振蕩?

圖 1.電流振蕩發生在 PFC 級

您可能認為這種不穩定振蕩由過快的控制帶引起,因此您減小比例積分 (PI) 控制器的比例增益 (Kp) 和積分增益(Ki),并顯著降低交叉頻率。振蕩就會消失。

但這是最佳解決方案嗎?較低的電流環路帶寬會降低控制速度,但您可能會發現總諧波失真 (THD) 測試將會失敗。有時,當源阻抗大一些時,振蕩會再次出現。

這種不穩定性是否可能有其他原因?如何以足夠的相位裕度實現最佳控制帶寬?下面我們來詳細分析一下數字控制環路,從而了解這一潛在的錯誤是如何引入的。我們還將向您展示如何檢查控制固件中是否出現這種不穩定性。

基于 MCU 的數字控制

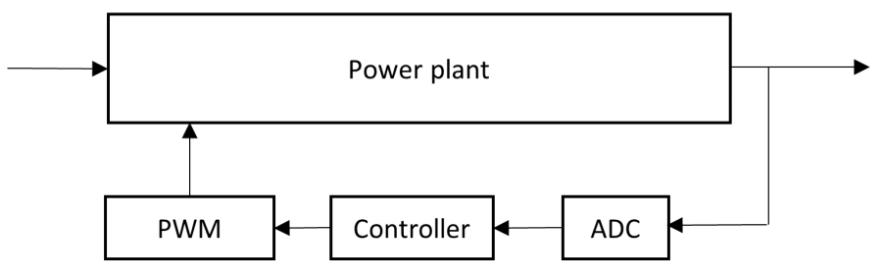

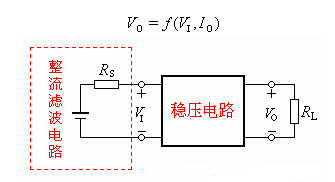

圖 2 展示了基于 MCU 的數字控制系統。

圖 2. 數字控制系統圍繞微控制器構建而成

控制環路包含一個模數轉換器 (ADC)用于進行對象電流/電壓采樣,一個數字控制器用于生成調整值,以及一個脈寬調制器 (PWM)用于執行調整,可通過更改占空比或頻率來改變目標電流/電壓。

開關模式電源 (SMPS) 中的 ADC 采樣通常位于兩個開關周期的中間點,這樣不僅可以避免開關產生的噪聲干擾,還可以獲取連續導通模式 (CCM) 下功率電感器的平均電流值。

數字控制器在中斷服務例程 (ISR) 中進行計算,可以與 PWM 輸出同步觸發。觸發事件可以是以下事件之一:PWM 的“COUNTER”等于“ZERO”、“PERIOD”或特定的值“CMP”。

控制器完成所有計算時無法立即更新 PWM,但 PWM 寄存器必須在一個專門時刻由影子寄存器加載,如 PWM 計數器等于“ZERO”或“PERIOD”時。如果 PWM 值在計數器上升或下降過程中發生變化,則很可能產生錯誤的 PWM 動作,導致脈沖丟失或脈沖重復。

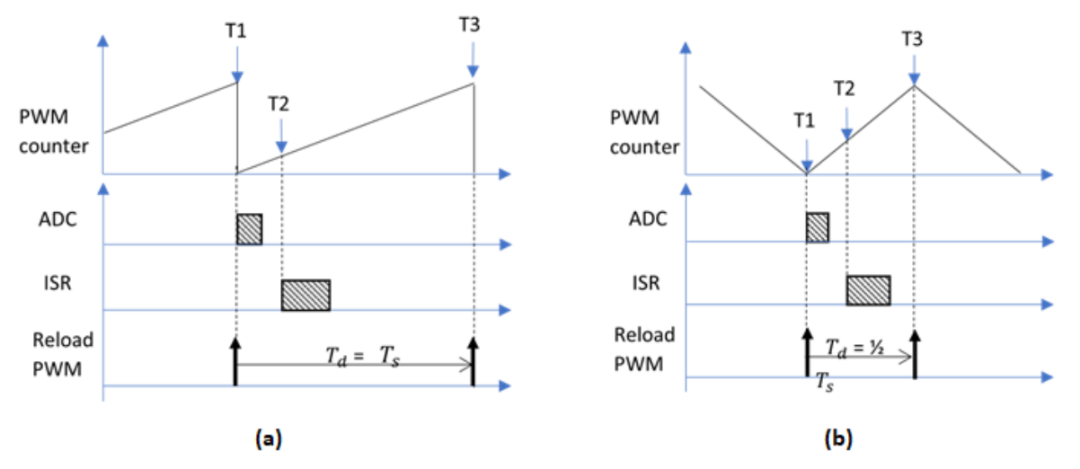

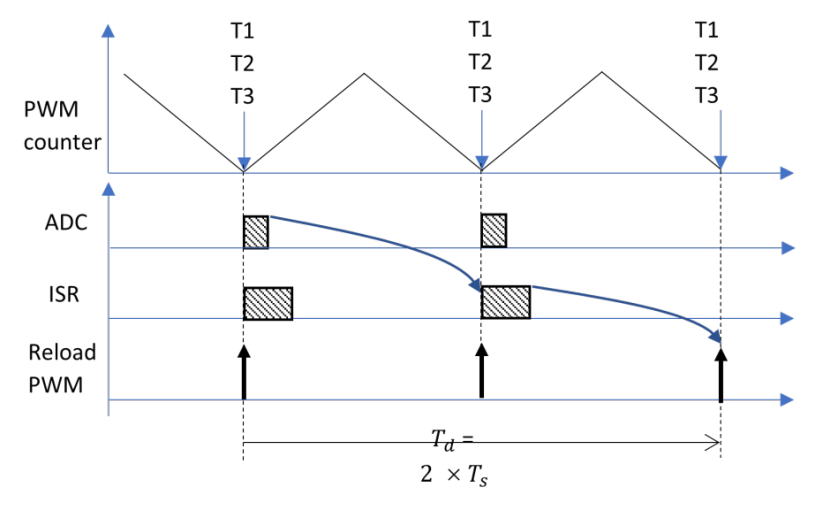

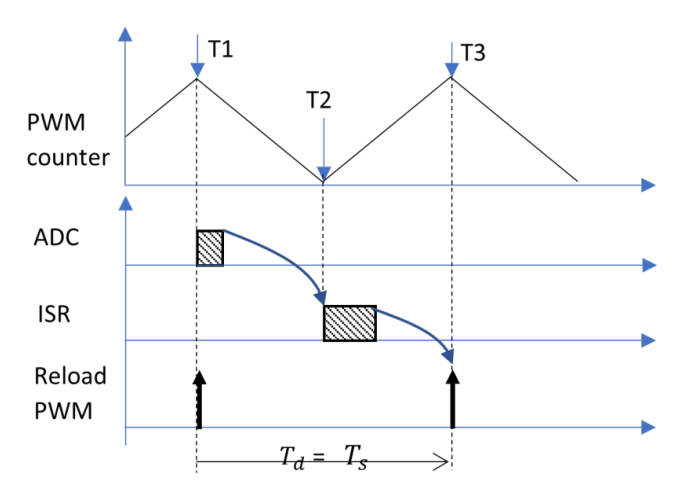

與模擬控制系統不同,數字控制按照采樣頻率來執行,并且從采樣到 PWM 重新載入新值必須有一個延遲時間 (Td)。PWM 修改通過調整翻轉時刻來實現,翻轉時刻在單邊沿調制時(遞增/遞減模式)發生一次,在雙邊沿調制時(先遞增后遞減模式)發生兩次。因此,最小 Td 將會是一個開關周期 Ts(如圖 3a 所示),或半個開關周期 Ts/2(如圖 3b 所示),具體取決于您選擇的調制重新加載頻率。

圖 3. 最小延遲時間通過 PWM 調整而引入

(a) 向上計數模式,(b) 上下計數模式

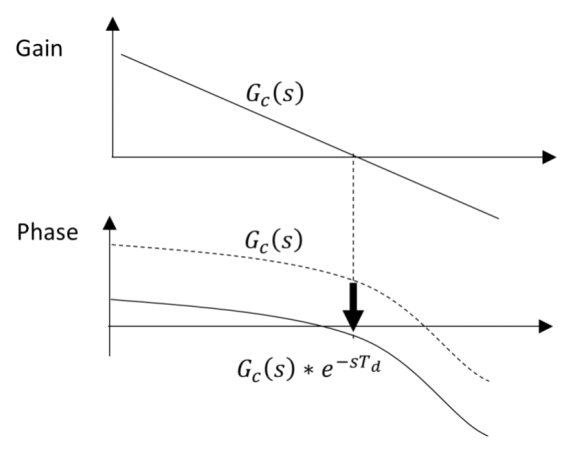

如圖 4 所示,Td 在其傳遞函數中表示為 e-sxTd,這將減少相位裕度。當然,當相位裕度小于 45 度時,系統將變得不穩定,并會發生振蕩。

圖 4. 波德圖中顯示了延時時間的影響

數字控制實現中的潛在代碼錯誤

在正確執行的情況下,最小 Td 為一個開關周期 Ts 或半個開關周期 Ts/2。但是,如果未考慮 ADC、ISR 和 PWM 重新加載的后果,則將控制延遲擴展到高于一個開關周期可能會減小相位裕度,導致不穩定。

例如,在圖 5 中,當 PWM 計數器等于零,ADC 的 ISR 觸發和 PWM 重新加載會同時啟動。

盡管所有塊都同時執行,但在這種情況下,您是否可以預期 Td 為零?當然不能!

圖 5. 此處是一個會引入較大延遲時間的錯誤代碼示例

這是因為 ADC 轉換和 ISR 計算所需的時間遠超一個 MCU 時鐘周期,當 ISR 讀取 ADC 結果時,ADC 轉換仍未完成。因此,ISR 將獲取“舊”采樣值進行計算,而最新值的計算將延遲到下一個開關周期。ISR 計算完成后,新 PWM 值僅寫入影子寄存器中,隨后將在下一個開關周期中重新加載。實際上,Td 的總控制延遲將為兩個開關周期,即 2 x Ts。

除了此處所示的示例之外,其他實現方案也可能會引入類似的擴展控制延遲,例如,在 ISR 代碼中將 ADC 值讀取放在控制器計算之后,或者在計算控制器之前添加 N 周期算法平均值。

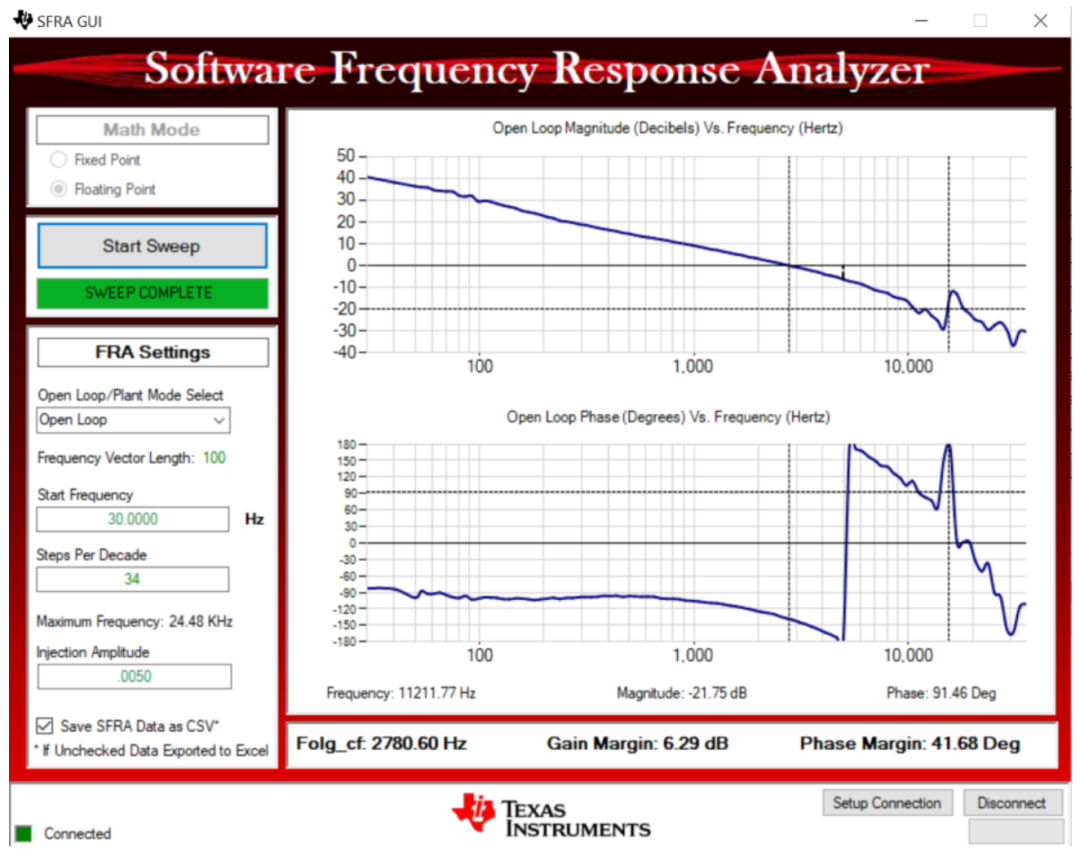

如圖 6 所示,在圖 5 的錯誤實現中,如果將 GAIN 交叉頻率設置在 3kHz 左右,則相位裕度為 41.68 度。此值小于 45 度,并且扼流電流有明顯的振蕩,比如圖 1 的波形,因此您被迫將交叉頻率降至低于 2kHz;然后 iTHD 更差,無法滿足要求。

圖 6. 錯誤代碼實現下的波德圖

設計解決方案

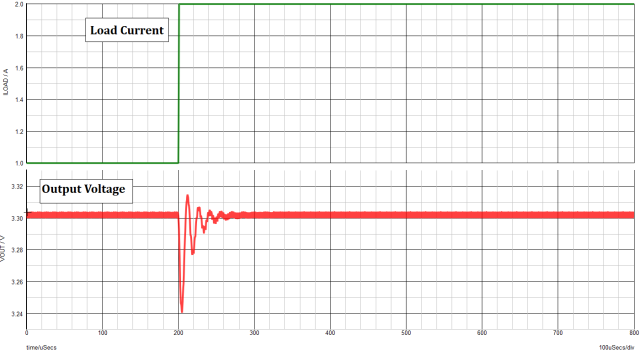

此問題可以輕松解決,只需將 ADC 轉換移動到 COUNTER = PERIOD 的時刻,并且使 PWM 重新加載在下一個 COUNTER = PERIOD 時刻發生,如圖 7 所示。

圖 7. 通過改進代碼可減少控制延遲

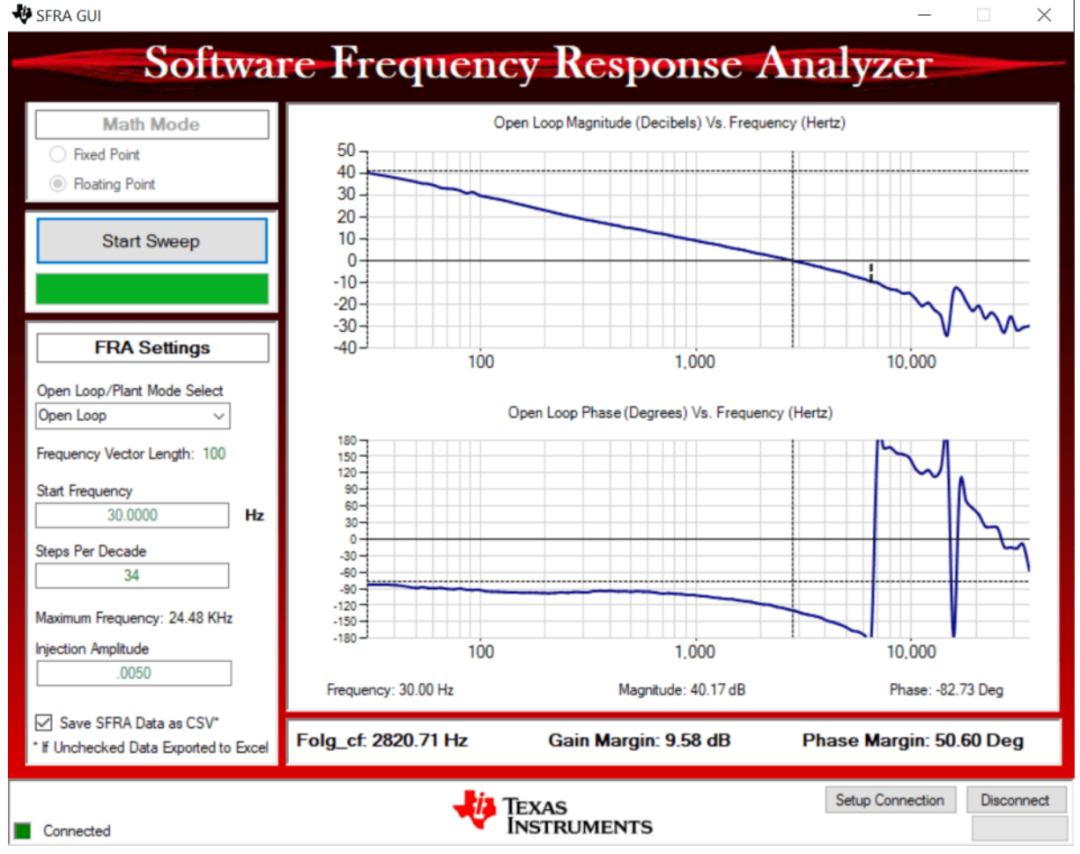

控制延遲將減少為一個開關周期。相位裕度顯著增加,電流振蕩消失,如圖 8 和圖 9 所示。

圖 8. 改進代碼后的波德圖

圖 9. 改進代碼后的波形

組織有序的控制方案

在數字實現中,從 ADC 采樣到 PWM 調整的控制延遲將減小相位裕度并導致振蕩。解決該問題時,應考慮 ADC 采樣、控制器計算和 PWM 重新加載的后果。組織有序的控制方案可以將延遲盡可能減少到半個或一個開關周期,從而增加相位裕度和環路帶寬。

-

mcu

+關注

關注

146文章

17317瀏覽量

352618 -

控制器

+關注

關注

112文章

16444瀏覽量

179423 -

德州儀器

+關注

關注

123文章

1733瀏覽量

140993 -

PFC

+關注

關注

47文章

977瀏覽量

106389 -

數字控制

+關注

關注

2文章

182瀏覽量

25881

原文標題:源來如此|潛在的固件錯誤可能是導致控制不穩定的幕后黑手!

文章出處:【微信號:tisemi,微信公眾號:德州儀器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

無線網絡不穩定因素分析

電壓不穩定的原因及解決辦法

不穩定燃燒主動控制系統的設計與實現

診斷和穩定不穩定開關電源的快速提示

數字控制環路不穩定的原因分析

數字控制環路不穩定的原因分析

評論