編輯語

集成電路占用面積的不斷縮小,正在將性能限制,從晶體管本身轉移到晶體管之間的互連工藝。互連的電阻-電容延遲,隨著器件密度的增加而惡化,因為互連路徑變長,導線變窄,并且隨著新材料集成到電路中,需要更多類型的連接。這一綜述,通過關注材料的載流子平均自由程和內聚能,回顧了開發更好互連的策略。

摘 要

在芯片上集成更多器件的半導體技術,目前達到了器件單獨縮放,已經不再是提高器件性能的有效方式。問題在于連接晶體管的互連工藝,隨著尺寸按比例縮小以匹配晶體管尺寸,金屬的電阻率呈指數增加。

因此,總信號處理延遲,主要是來自互連的電阻-電容resistance-capacitance (RC)延遲,而不是來自晶體管開關速度的延遲。這一技術瓶頸,需要探索替代材料和顛覆性器件結構。

近日,韓國三星電子綜合技術院(Samsung Advanced Institute of Technology)Joon-Seok Kim,Jeehwan Kim,Sang Won Kim等,在Science上發表綜述文章,從材料和器件兩個方面,提出了互連技術中,RC電阻-電容延遲的提升策略。

Addressing interconnect challenges for enhanced computing performance.

解決互連難題,以增強計算性能。

互連電阻-電容resistance-capacitance ,RC延遲是器件性能的瓶頸。

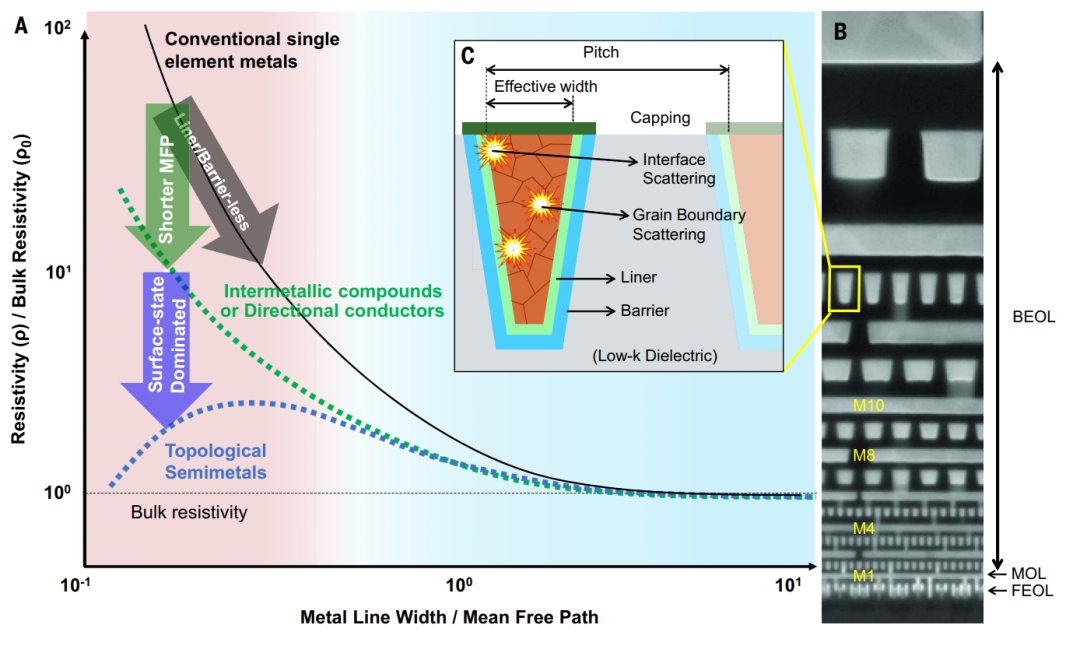

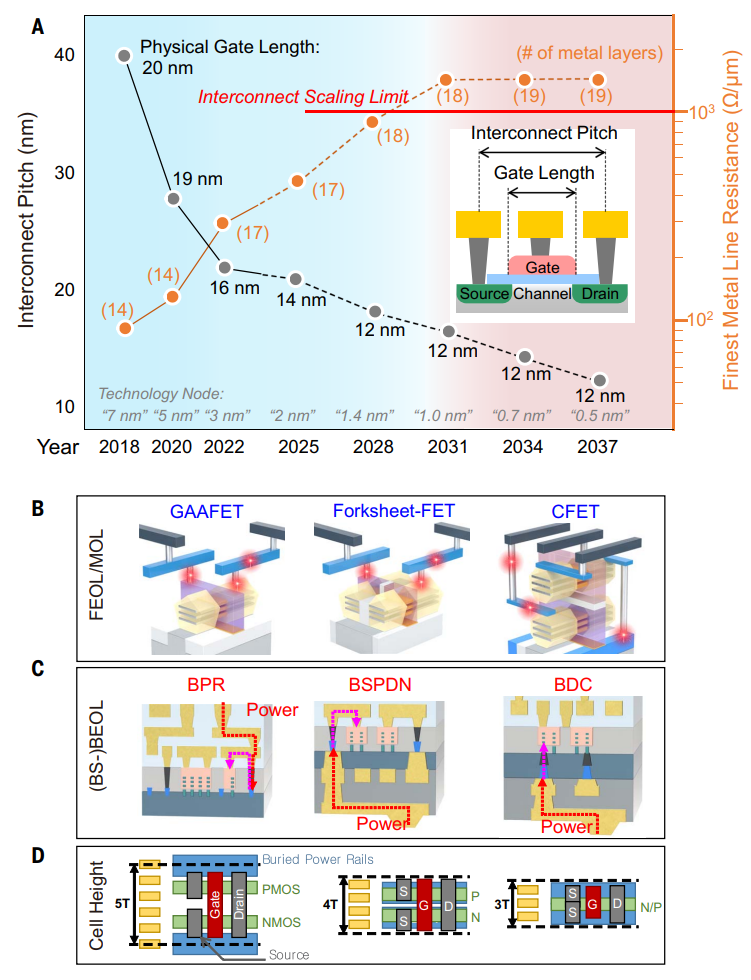

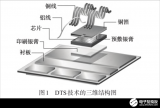

圖1. 電阻率增加的原因。

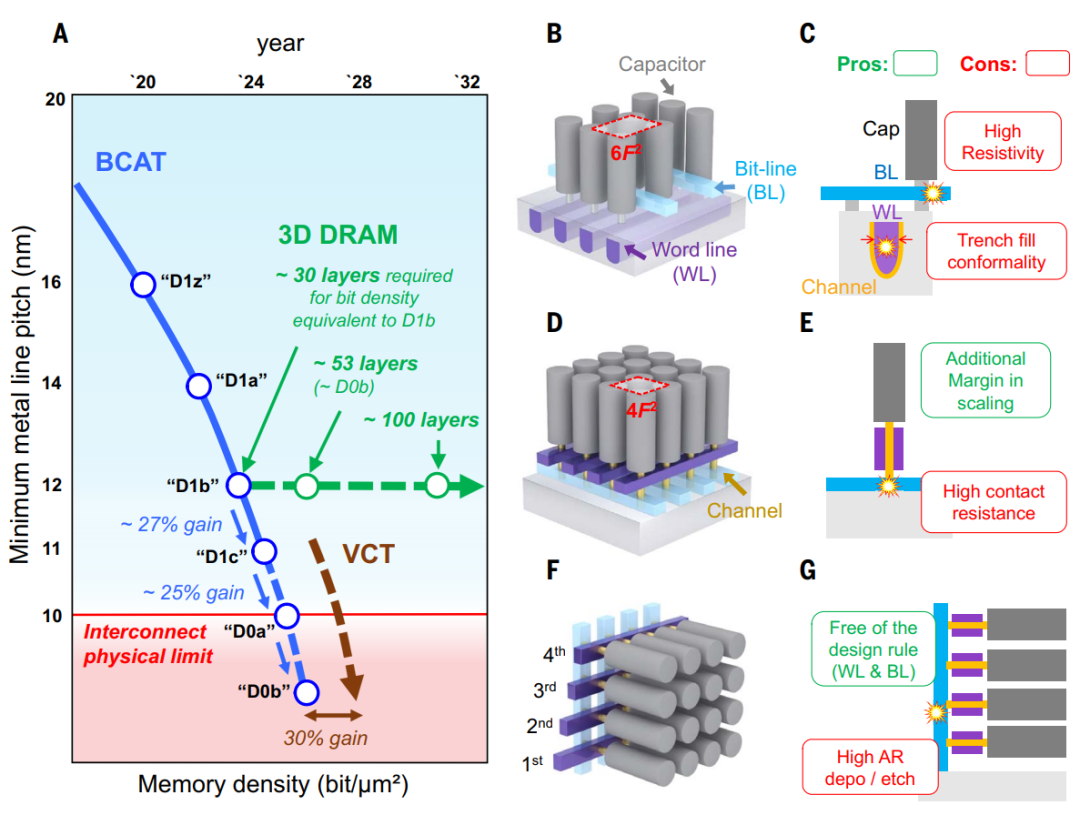

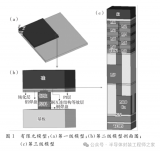

圖2. DRAM架構結構變化的擴展挑戰和進展。

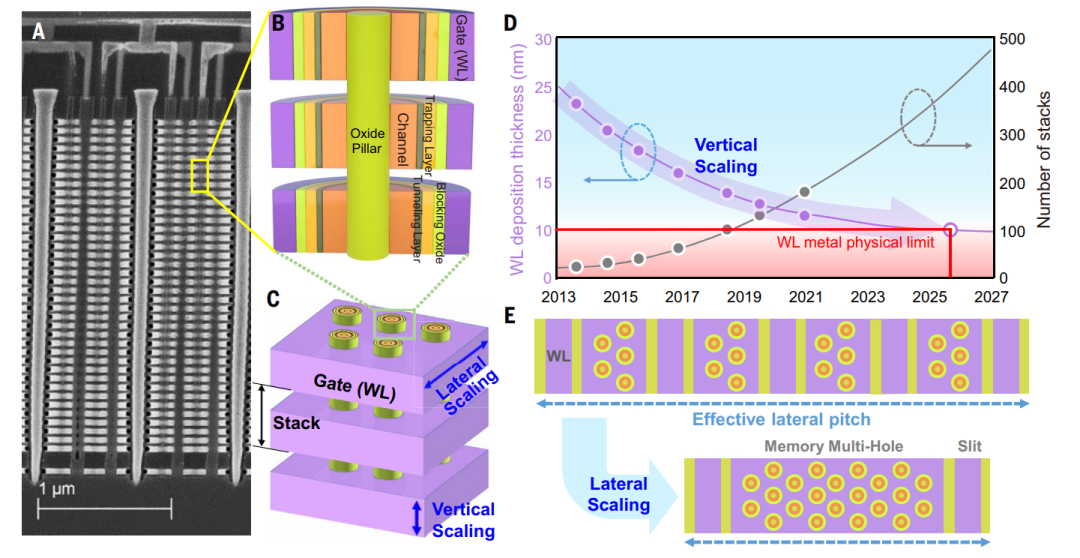

圖3. NAND閃存的擴展挑戰。

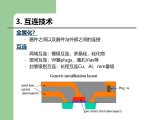

圖4. 邏輯器件的互連縮放和結構挑戰。

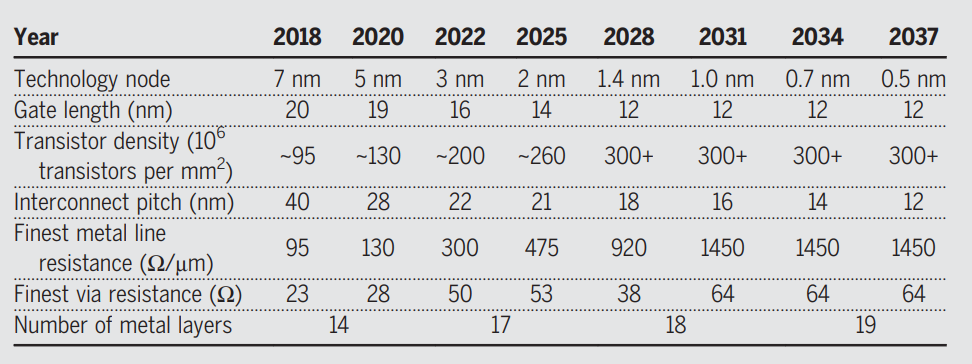

表2. 邏輯互連規范及其對技術節點的預測和要求。

研究進展

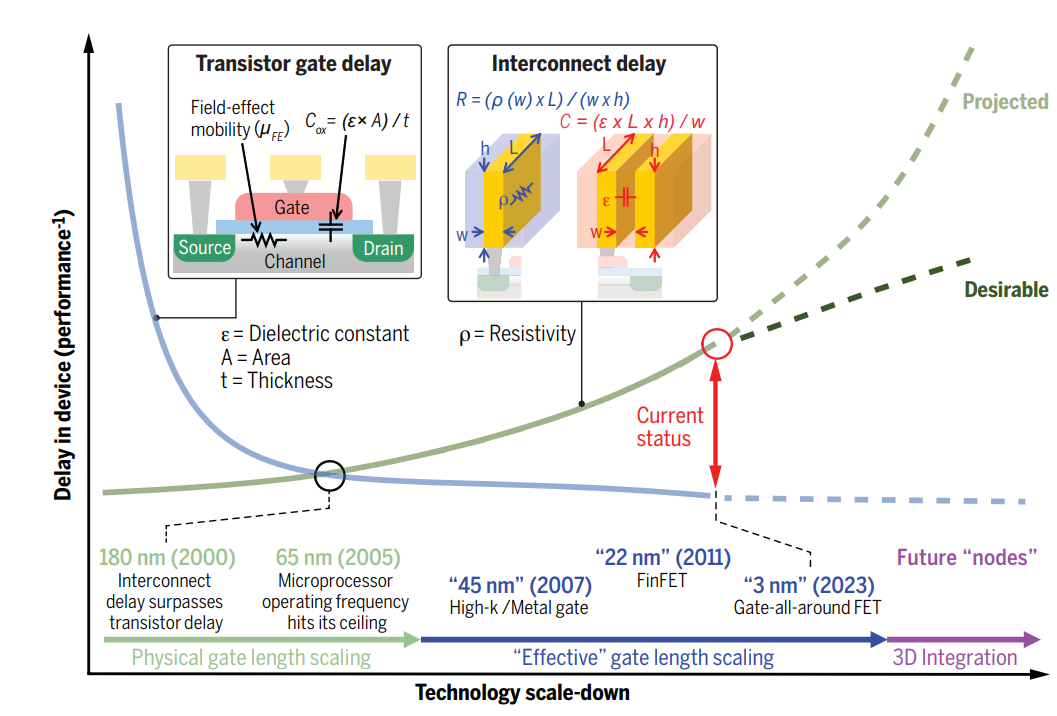

晶體管柵極延遲,取決晶體管柵極氧化物電容和溝道載流子遷移率,而互連RC延遲,則取決于金屬線電阻和電容決定。據報道,互連RC延遲已超過約180-nm節點時代的晶體管柵極延遲,并具有65-nm節點時代所能達到工作頻率上限。物理縮放之外的有效器件縮放方案,即高k/金屬柵極的引入和溝道結構的改變,增加了晶體管的密度,并提高晶體管的開關速度,但也導致互連RC延遲呈指數增長。隨著最近引入的垂直堆疊多個芯片策略,互連RC延遲,預計將以更快的速度增加,并對指數增長的計算需求,造成更嚴重的瓶頸。

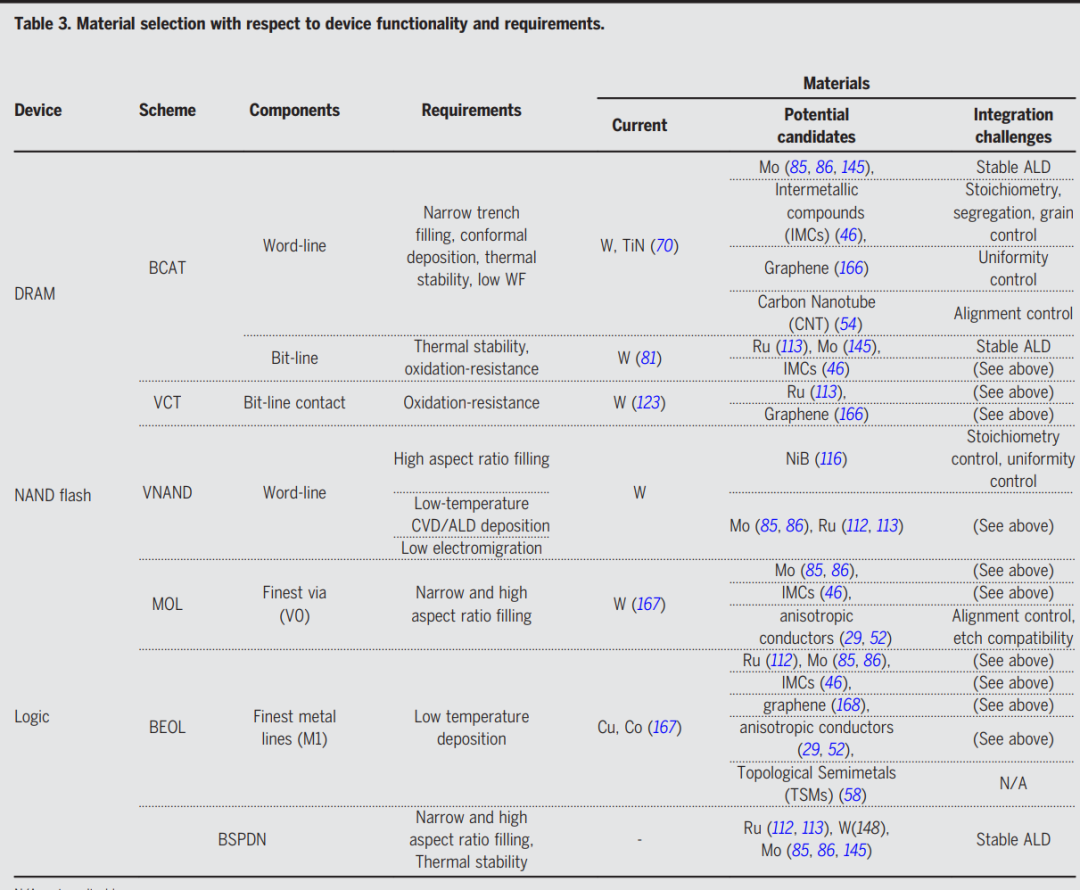

晶體管和存儲單元的橫向按比例縮小,迫使互連也按比例縮小到這樣的尺寸,其中導體的表面和晶界決定著電子散射,并導致電阻率的指數增加。未來互連的理想候選材料,應具有較短的平均自由程,從而使散射表現出較小的縮放效應,不需要襯層和勢壘層,并且具有表面態主導的導電性。就存儲器和邏輯器件的結構變化而言,由于朝著垂直集成結構的發展,以使面密度最大化,制造變得更具挑戰性。未來互連材料的研究,還應考慮兼容于最近開發的制造工藝。

在這篇綜述中,討論了當前互連技術的材料和器件挑戰,并討論了學術界和工業界未來研究的潛在方向。介紹了用于確定互連應用的合適材料,并評估其基本特性的方法,介紹了各種半導體器件中提出的結構進步,并建議基于器件功能和制造工藝的材料。最后,對半導體三維集成日益增長的重要性,提出了前瞻性的展望。

展望未來

用于互連的互補金屬氧化物半導體complementary metal-oxide semiconductor (CMOS)兼容導電材料的研究,業界通常是去優先化的,主要重點是提高半導體性能和增強高k電介質。這已經導致互連材料開發受挫,并且相比于半導體技術的其他方面,也受到較少的關注。在學術研究中,互連研究,通常強調選擇材料特性,而沒有全面考慮在實際器件架構中的適用性。為了解決這一關鍵差距,需要一種系統和協作的研究方法,建立一個強大的平臺,用于發現、合成、表征和實際驗證與下一代半導體技術兼容的互連材料。學術界和工業界之間這種共同努力,將促進互連解決方案的可行性開發,這些解決方案不僅在理論上很有前景,而且在功能與新興電子設備的苛刻性能和集成要求兼容。

文獻鏈接

Joon-Seok Kim et al. , Addressing interconnect challenges for enhanced computing performance. Science 386, eadk 6189 (2024)。

DOI:10.1126/science.adk6189

https://www.science.org/doi/10.1126/science.adk6189

本文譯自Science。

-

芯片

+關注

關注

456文章

51192瀏覽量

427352 -

集成電路

+關注

關注

5392文章

11624瀏覽量

363206 -

半導體

+關注

關注

334文章

27719瀏覽量

222708

原文標題:研究透視:芯片-互連材料 | Science

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

探索倒裝芯片互連:從原理到未來的全面剖析

集成電路的互連線材料及其發展

芯片和封裝級互連技術的最新進展

仁懋電子&amp;深圳先進材料研究院孫院長就芯片封裝行業友好交流

集成電路互連線材料進化史:從過去到未來的飛躍

實現異構集成與小芯片優勢的關鍵“互連”

OpenCV筑基之圖像的透視變換

淺談透視變換的硬件實現策略

SiC功率器件先進互連工藝研究

研究透視:芯片-互連材料

研究透視:芯片-互連材料

評論