在上期的芝識課堂中,我們介紹了一部分CMOS邏輯IC設(shè)計的常見問題以及處理辦法。本期課堂將繼續(xù)探討如何優(yōu)化CMOS邏輯IC的性能,特別是負(fù)載電容連接技巧和功耗計算,這些因素對于電路的設(shè)計極其重要。

負(fù)載電容和CMOS輸出引腳的連接問題

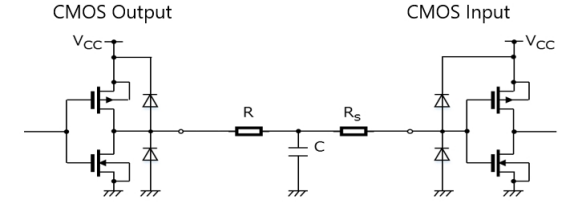

在將負(fù)載電容連接到CMOS集成電路(IC)的輸出引腳時,須謹(jǐn)慎選擇電容的大小。具體來說,大電容會增加CMOS輸出的傳輸延遲,并且電容的充/放電過程會增加進出的電流,這可能導(dǎo)致電路中的噪聲問題,甚至可能因電流過大而損壞連接引線。此外,由于電流在掉電時會流向輸出寄生二極管,因此大負(fù)載電容不可直接連接到CMOS IC上。

若需將電容器直接連接到CMOS IC的輸出端以增加其延遲時間或過濾噪聲,則應(yīng)選擇500pF或更小的電容。當(dāng)需要較大的電容時,應(yīng)在IC輸出端和電容器之間連接限流電阻(R)。具有輸出容限功能的CMOS IC不需要限流電阻(R)來斷電。但可能需要一個限流電阻(R)來限制進入電容的充電電流。

不僅如此,大負(fù)載電容也不應(yīng)直接連接到CMOS IC的輸入引腳。

當(dāng)電容由于掉電而放電時,電流流向內(nèi)部保護二極管,并通過輸入引腳返回到VCC。因此,大負(fù)載電容不能直接連接到輸入引腳。如果需要直接連接電容,推薦最高選擇500 pF的器件。如果需要更大的電容器,則應(yīng)在IC輸入端和電容器之間連接限流電阻(Rs)。

連接大負(fù)載電容

計算工作電流和功耗

如何計算通用邏輯IC的功耗?可通過獲取靜態(tài)電流和動態(tài)電流,然后將該電流乘以施加到IC的電壓來計算通用邏輯IC的功耗。

靜態(tài)功耗:PS

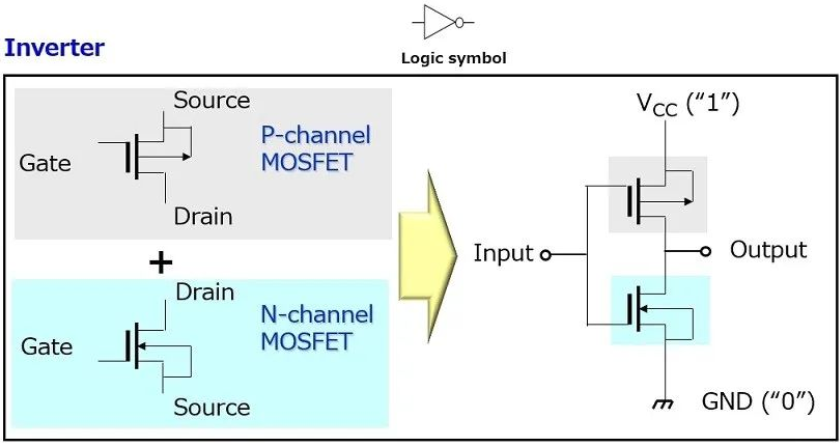

當(dāng)CMOS邏輯處于靜態(tài)(即當(dāng)其輸入電壓幾乎保持不變)時,除了流過內(nèi)部反向偏置pn結(jié)的微小漏電流(即靜態(tài)供電電流,ICC)以外,幾乎沒有電流流動。

靜態(tài)功耗是將ICC乘以供電電壓:PS=VCC×ICC

VCC:施加在邏輯IC上的電壓。

ICC:如數(shù)據(jù)表所示的靜態(tài)供電電流。

靜態(tài)功耗:PL+PPD

動態(tài)供電電流是指當(dāng)輸入在高電平和低電平之間轉(zhuǎn)換時流過CMOS邏輯IC的電流。該電流在電容充放電過程中流動。必須同時考慮寄生電容(內(nèi)部等效電容)和負(fù)載電容。

動態(tài)功耗是將動態(tài)供電電流乘以施加在p溝道或n溝道MOSFET上的電壓。為方便起見,以下計算將假定此電壓等于VCC,此時動態(tài)供電電流最大。

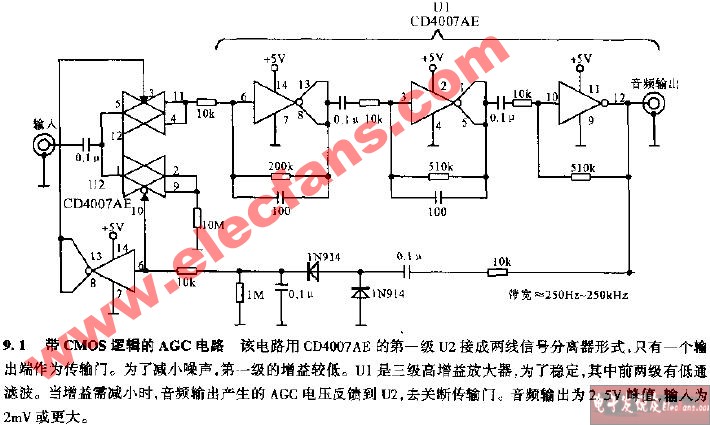

負(fù)載電容(CL)引起的動態(tài)功耗:PL

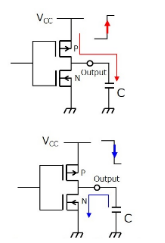

PL指外部負(fù)載充電和放電時的功耗,如右圖所示。

CL引起的動態(tài)功耗

存儲在負(fù)載電容上的電荷量(QL)計算為QL=CL×VCC,CL為負(fù)載電容。

設(shè)輸出信號頻率為fOUT(=1/TOUT),則平均電流(IL)表示為:IL=QL/T=CL×VCC×fOUT;因此,動態(tài)功耗(PL)為:PL=VCC×IL=CL×VCC2×fOUT;

如果一個IC有多個輸出,其動態(tài)功耗可計算如下:PL=VCC2×Σ(CLn×fOUTn)

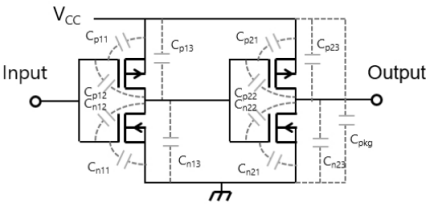

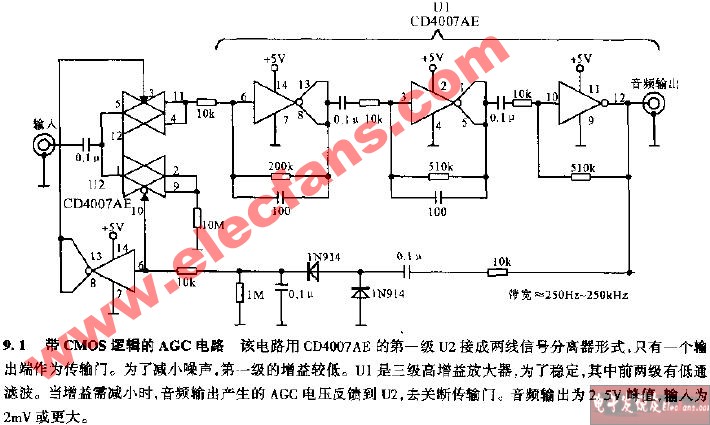

內(nèi)部等效電容(CPD)引起的動態(tài)功耗:PPD

CMOS邏輯IC具有各種寄生電容,如右圖所示。這些電容可等效地表示為CPD(實際上,CPD的基于零負(fù)載條件下相對較高頻率(1 MHz)時的功耗計算得出的)。

PPD是IC的等效電容消耗的功率,可按與PL相同的方式考慮。但請注意,PPD的計算是基于輸入頻率(fIN):PPD=VCC×IL=CPD×VCC2×fIN。

CPD引起的動態(tài)功耗

總功耗(PTTL)可以表示為靜態(tài)功耗(PS)和動態(tài)功耗(PL+PPD)之和:PTTL=PS+PL+PPD。

輸入容限功能可用于電平轉(zhuǎn)換

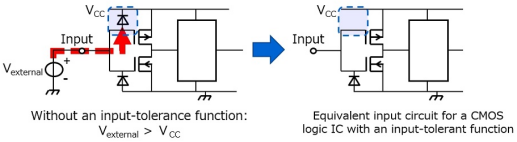

輸入容限功能允許在電源激活時或電壓為0 V時,向輸入端施加高達(dá)最大工作電壓的電壓,允許電平從較高電壓轉(zhuǎn)換為較低電壓。例如,東芝的74VHC和74LCX系列可用于將5 V轉(zhuǎn)換至3 V,74VCX系列可用于將3V轉(zhuǎn)換至1.2 V。

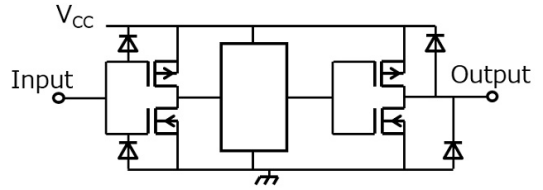

無輸入容限和掉電保護功能的CMOS邏輯IC的等效輸入/輸出電路

在輸入側(cè)插入二極管以進行ESD防護。如果施加的電壓高于VCC或在IC關(guān)斷時施加電壓,則輸入端和電源之間的二極管可能會導(dǎo)通。在本例中,IC可能會被產(chǎn)生的大電流破壞。因此,通過使用具有輸入容限功能的IC,即輸入端和電源之間無二極管的IC,可以防止器件損壞。

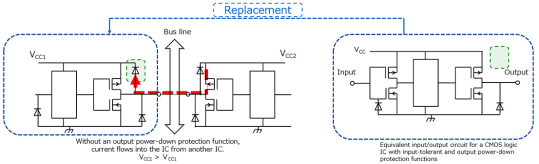

掉電保護功能應(yīng)用示例(局部掉電)

如果使用具有掉電保護功能的IC,則可以實現(xiàn)局部掉電。為降低功耗,具有兩個電壓范圍(VCC1和VCC2)的系統(tǒng)可以提供局部掉電模式。在該模式下,其中由VCC1運行的子系統(tǒng)將被關(guān)閉。例如,假設(shè)在電壓范圍VCC1使用74VHC系列。74VHC系列在輸出端和電源之間有一個非預(yù)期的寄生二極管。因此,當(dāng)VCC2>VCC1時,該寄生二極管導(dǎo)通。在這種情況下,IC可能會被產(chǎn)生的大電流破壞。使用既沒有輸入也沒有輸出寄生二極管的IC(如74VHCT、74LCX和74VCX系列)可以防止器件損壞。這些系列提供掉電保護。

東芝每個系列都具有輸入容限和輸出掉電保護功能:

其中,TC4049BF/BP,TC4050BF/BP,TC74HC4049BP/BF/BFT,74HC4049D,TTC74HC4050BP/BF/BFT和74HC4050D具有允許從較高電壓到較低電壓電平轉(zhuǎn)換的輸入容限功能。

除這些使用事項和功能外,在使用CMOS邏輯IC時也應(yīng)注意噪聲的危害。下期內(nèi)容我們將進入實際的應(yīng)用案例,學(xué)習(xí)電路設(shè)計中的噪聲以及應(yīng)對策略,歡迎關(guān)注!

關(guān)于東芝電子元件及存儲裝置株式會社

東芝電子元件及存儲裝置株式會社是先進的半導(dǎo)體和存儲解決方案的領(lǐng)先供應(yīng)商,公司累積了半個多世紀(jì)的經(jīng)驗和創(chuàng)新,為客戶和合作伙伴提供分立半導(dǎo)體、系統(tǒng)LSI和HDD領(lǐng)域的杰出解決方案。

東芝電子元件及存儲裝置株式會社十分注重與客戶的密切協(xié)作,旨在促進價值共創(chuàng),共同開拓新市場,期待為世界各地的人們建設(shè)更美好的未來并做出貢獻。

-

集成電路

+關(guān)注

關(guān)注

5388文章

11562瀏覽量

362040 -

CMOS

+關(guān)注

關(guān)注

58文章

5722瀏覽量

235635 -

二極管

+關(guān)注

關(guān)注

147文章

9653瀏覽量

166694 -

負(fù)載電容

+關(guān)注

關(guān)注

0文章

140瀏覽量

10449 -

邏輯IC

+關(guān)注

關(guān)注

0文章

25瀏覽量

6460

原文標(biāo)題:芝識課堂【CMOS邏輯IC的使用注意事項】—深入電子設(shè)計,需要這份指南(二)

文章出處:【微信號:toshiba_semicon,微信公眾號:東芝半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

CMOS邏輯IC的使用注意事項

TTL和CMOS邏輯門電路的幾點認(rèn)識

CMOS集成邏輯門的邏輯功能與參數(shù)測試

CMOS邏輯門電路

CMOS邏輯電路,CMOS邏輯電路是什么意思

CMOS邏輯門電路介紹

CMOS邏輯IC基礎(chǔ)知識:系統(tǒng)認(rèn)識CMOS邏輯IC

一起了解CMOS邏輯IC的基本操作

CMOS邏輯IC的基本操作流程

【CMOS邏輯IC基礎(chǔ)知識】——受歡迎的CMOS邏輯IC

CMOS邏輯IC基礎(chǔ)知識:解密組合邏輯背后的強大用途(上)

【CMOS邏輯IC基礎(chǔ)知識】—解密組合邏輯背后的強大用途!(上)

如何優(yōu)化CMOS邏輯IC的性能

如何優(yōu)化CMOS邏輯IC的性能

評論