在當今高速電子系統的設計與應用中,信號完整性已成為至關重要的考量因素。隨著電子設備的數據傳輸速率不斷攀升,信號在電路中傳輸時面臨著諸多挑戰,如反射、串擾、延遲等,這些問題會嚴重影響系統的性能和可靠性。

當信號沿著傳輸線傳播時,遇到阻抗不連續的點,就會發生反射現象。例如,在電路板上的走線寬度變化、過孔連接或者不同層間的介質差異等,都可能導致阻抗突變。反射回來的信號與原始信號疊加,會造成信號失真,使接收端難以準確識別信號的邏輯狀態。

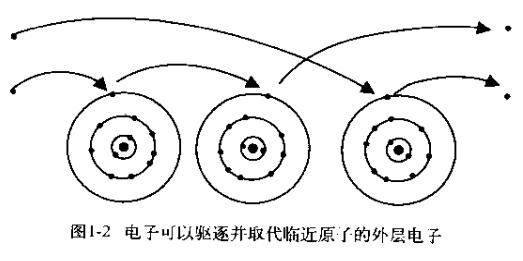

串擾則是指相鄰信號線路之間的電磁耦合,一條線路上的信號變化會在相鄰線路上感應出噪聲信號。在高密度布線的電路板中,這種現象尤為明顯。例如,在高速數字電路中,時鐘線與數據線相鄰時,時鐘信號的快速跳變可能會在數據線上產生串擾噪聲,導致數據傳輸錯誤。

延遲問題也不容忽視。信號在傳輸線中的傳播速度并非無限,而且不同長度和材質的傳輸線會產生不同的延遲。在同步電路系統中,如果信號延遲差異過大,可能會導致時序違規,使數據無法在正確的時鐘沿被采樣,從而引發系統故障。

為解決信號完整性問題,首先在電路設計階段要進行合理的拓撲規劃。對于多點連接的網絡,如總線結構,采用合適的拓撲(如星形、樹形或菊花鏈形)可以優化信號的分布和傳輸路徑,減少反射和延遲的影響。同時,要精確控制傳輸線的阻抗匹配,通過調整走線的寬度、間距以及介質的介電常數等參數,使傳輸線的特征阻抗與源端和負載端的阻抗相匹配,從而有效降低反射。

在 PCB 布局方面,要遵循一定的規則。將高速信號與低速信號分開布局,減少相互之間的串擾。對于敏感信號,如模擬信號和微弱的傳感器信號,要進行良好的屏蔽處理,防止受到其他強信號的干擾。此外,合理安排過孔的位置和數量,因為過孔會引入額外的電感和電容,影響信號的完整性,應盡量減少不必要的過孔使用。

在高速電路設計中,還可以采用一些信號完整性分析工具,如 HSPICE、ADS 等軟件進行仿真分析。在設計初期對電路進行建模和仿真,能夠提前預測信號完整性問題,并根據仿真結果對電路設計進行優化調整,大大提高設計的成功率和效率,降低硬件調試的成本和時間。

隨著電子技術的不斷發展,信號完整性問題將持續面臨新的挑戰,但通過不斷優化電路設計、PCB 布局以及借助先進的仿真分析工具,我們能夠有效地應對這些問題,確保電子系統的高性能和可靠性,推動電子技術在各個領域的廣泛應用和進一步發展。

-

信號完整性

+關注

關注

68文章

1417瀏覽量

95631 -

電子電路

+關注

關注

78文章

1227瀏覽量

67034 -

PCB

+關注

關注

1文章

1824瀏覽量

13204

發布評論請先 登錄

相關推薦

常見的信號完整性問題及解決方案

PCB設計中的信號完整性問題

探究電子電路中的信號完整性問題

探究電子電路中的信號完整性問題

評論