在現(xiàn)代高速電子系統(tǒng)中,電源完整性是指確保電子系統(tǒng)中所有元件都能穩(wěn)定、準(zhǔn)確地獲得電源電壓和電流,以確保系統(tǒng)穩(wěn)定運(yùn)行,避免受到雜訊或波動(dòng)的影響。電源完整性已成為系統(tǒng)性能和可靠性的關(guān)鍵因素,要達(dá)成這目標(biāo),需在設(shè)計(jì)初期利用模擬軟體進(jìn)行系統(tǒng)阻抗特性模擬,以確保電源品質(zhì)。但是,往往專案開發(fā)時(shí)程有限,如何在時(shí)間有限的情況下,完成大量電源設(shè)計(jì)的模擬需求,成為了優(yōu)化開發(fā)流程的關(guān)鍵課題。

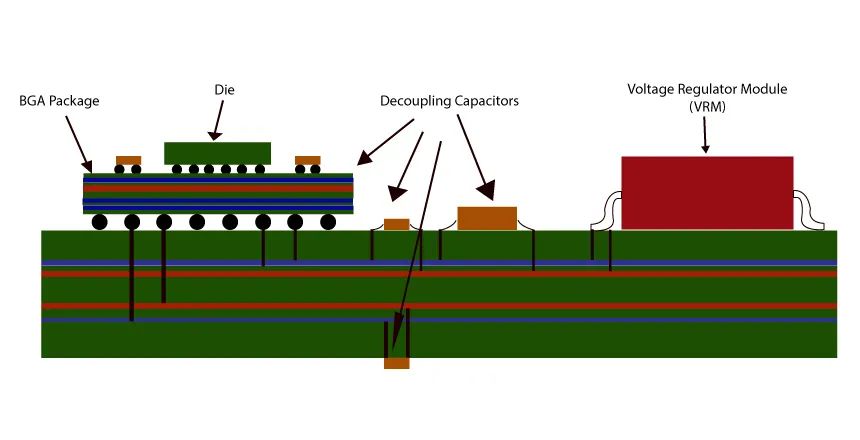

Figure 1. 電源網(wǎng)路 (Source from SIERRA CIRCUITS Proto Express)

Qualcomm、Intel、MTK等IC設(shè)計(jì)大廠規(guī)范多項(xiàng)PI模擬項(xiàng)目和設(shè)計(jì)目標(biāo),以確保其產(chǎn)品能在系統(tǒng)上穩(wěn)定工作。隨著時(shí)間推移,模擬項(xiàng)目數(shù)量顯著增加。這些要求使得電源完整性設(shè)計(jì)和驗(yàn)證成為硬體與模擬工程師的必須任務(wù)。

「電源完整性模擬」的開發(fā)挑戰(zhàn)

由于電源完整性需求的急速增長(zhǎng),硬體和模擬工程師面臨多種挑戰(zhàn):

時(shí)間與人力資源限制:傳統(tǒng)手動(dòng)模擬耗時(shí)且需要專業(yè)的模擬工程師參與,模擬項(xiàng)目逐漸增多延長(zhǎng)設(shè)計(jì)周期,影響產(chǎn)品上市時(shí)間。

錯(cuò)誤率與品質(zhì)不一致:模擬需求增加,手動(dòng)設(shè)置容易出錯(cuò),導(dǎo)致結(jié)果不一致性和重復(fù)模擬工作,浪費(fèi)資源。

大量模擬需求管理:各芯片有不同電源設(shè)計(jì)需求,模擬工程師需針對(duì)每個(gè)項(xiàng)目進(jìn)行特定的參數(shù)設(shè)定,如何有效管理這些設(shè)定成為挑戰(zhàn)。

設(shè)計(jì)復(fù)雜度提升:處理器性能提高對(duì)電源要求更嚴(yán)苛,工程師需考慮更多設(shè)計(jì)因素,如去耦電容設(shè)計(jì)和電源與接地平面完整性。隨著設(shè)計(jì)變得復(fù)雜,快速找到問題并優(yōu)化設(shè)計(jì)以減少資源和時(shí)間浪費(fèi)尤為重要。

有鑒于此,USI 環(huán)旭電子CE 研發(fā)團(tuán)隊(duì)開發(fā)出一套「電源完整性模擬系統(tǒng)」并建構(gòu)在前端設(shè)計(jì)及自動(dòng)化模擬平臺(tái)(FEDS),此款「自動(dòng)化」電源完整性模擬工具將能用于解決上述挑戰(zhàn)。

電源完整性模擬系統(tǒng) (Power Integrity Simulation)

此電源完整性模擬系統(tǒng)的核心技術(shù)在于自動(dòng)化工作流程,硬體工程師只需簡(jiǎn)單操作即可完成大量模擬任務(wù)。此系統(tǒng)減少手動(dòng)設(shè)置時(shí)間和人為錯(cuò)誤,提升效率。我們同時(shí)建立電源完整性優(yōu)化的手法,并透過內(nèi)部LMS課程培訓(xùn)工程師進(jìn)行設(shè)計(jì)優(yōu)化,推廣自動(dòng)化系統(tǒng)到工程師端,縮減跨部門操作,提升模擬效率和產(chǎn)出,使電源完整性設(shè)計(jì)在有限時(shí)間內(nèi)完成。

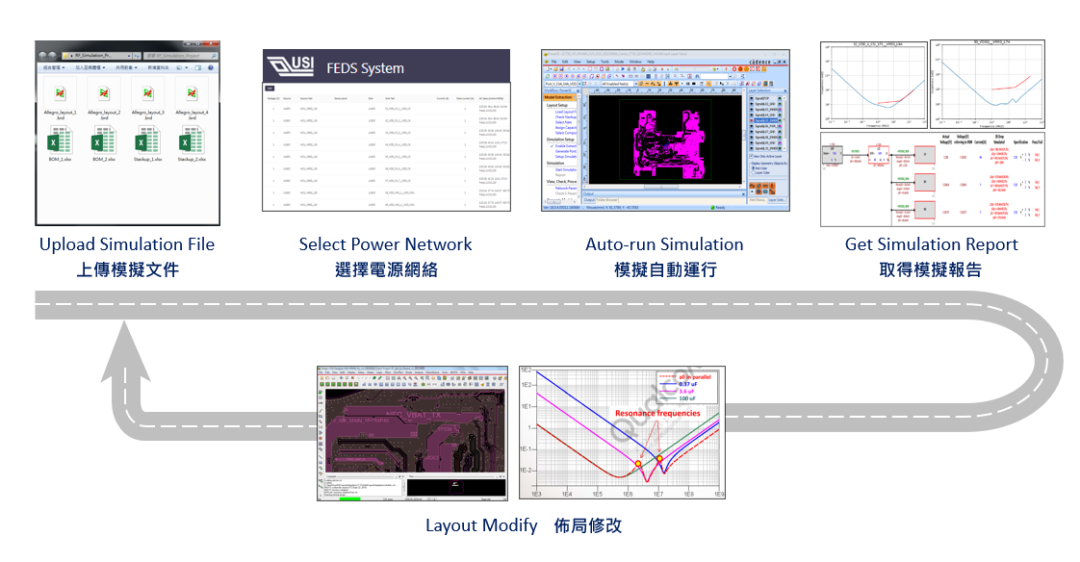

走進(jìn)FEDS-PI的工作流程

首先,硬體工程師準(zhǔn)備模擬資料(Layout/BOM/Stackup)并上傳至系統(tǒng)。

其次,選擇或編輯要模擬的電源網(wǎng)路,模擬工程師會(huì)依據(jù)晶片組的PI設(shè)計(jì)要求建立資料庫(kù)。

FEDS-PI系統(tǒng)自動(dòng)連結(jié)模擬軟體,將設(shè)定帶入執(zhí)行模擬,模擬完成后,系統(tǒng)生成報(bào)告并通知。

用戶可依報(bào)告結(jié)果進(jìn)行設(shè)計(jì)優(yōu)化,修改后再進(jìn)行模擬驗(yàn)證。

系統(tǒng)儲(chǔ)存模擬歷史紀(jì)錄,方便比較不同設(shè)計(jì)方案的改進(jìn)效果,以逐步優(yōu)化PI設(shè)計(jì)。

Figure2. 電源完整性模擬系統(tǒng)FEDS-PI 流程圖

實(shí)際應(yīng)用成效 (Results)

電源完整性模擬系統(tǒng)有效處理大量模擬需求,提供簡(jiǎn)單操作介面,工程師可自行完成模擬,無需復(fù)雜設(shè)置,節(jié)省人力成本。同時(shí),再結(jié)合優(yōu)化流程,快速診斷并解決電源問題,縮短工作周期并提升設(shè)計(jì)品質(zhì)。相比傳統(tǒng)手動(dòng)模擬方法,電源完整性模擬系統(tǒng)展現(xiàn)了以下三個(gè)顯著優(yōu)勢(shì):

時(shí)間效率:傳統(tǒng)手動(dòng)模擬耗時(shí),從設(shè)定到報(bào)告制作需12個(gè)小時(shí),F(xiàn)EDS-PI可將整個(gè)流程縮短至僅需2小時(shí),顯著提升了83%的專案執(zhí)行效率。

可靠性:手動(dòng)模擬易出錯(cuò),導(dǎo)致結(jié)果不穩(wěn)定。FEDS-PI的自動(dòng)化流程確保一致性和穩(wěn)定性,并內(nèi)建錯(cuò)誤檢查機(jī)制,能在上傳Layout后檢測(cè)潛在問題,如開路或短路,及時(shí)發(fā)出警告,大幅降低人為錯(cuò)誤風(fēng)險(xiǎn)。

模擬資源利用率:傳統(tǒng)方法每次模擬需工程師和軟體許可,而FEDS-PI只需上傳檔案并勾選模擬項(xiàng)目,系統(tǒng)即可自動(dòng)完成模擬并產(chǎn)生報(bào)告。FEDS-PI僅需一個(gè)軟體許可和一臺(tái)Server即可24小時(shí)運(yùn)行,提高資源利用率。

USI環(huán)旭電子所開發(fā)的FEDS平臺(tái),不僅是一套工具,更是以其高效、可靠、智能的特點(diǎn),正在引領(lǐng)電源完整性設(shè)計(jì)進(jìn)入一場(chǎng)效率革命。未來,隨著AI技術(shù)的進(jìn)一步發(fā)展,F(xiàn)EDS有望實(shí)現(xiàn)更智能化的自動(dòng)化,例如自動(dòng)識(shí)別設(shè)計(jì)缺陷、自動(dòng)生成優(yōu)化方案等。

透過其中的「電源完整性模擬系統(tǒng)」,加上電源設(shè)計(jì)的優(yōu)化攻略,可以明確找出電源問題的根本原因,修改后能快速模擬驗(yàn)證,整體縮短解決問題的工作周期,顯著提升整體模擬效率并提高產(chǎn)品設(shè)計(jì)品質(zhì),有效解決了傳統(tǒng)手動(dòng)模擬所面臨的時(shí)間、人力、錯(cuò)誤率等諸多挑戰(zhàn),為開發(fā)流程提供了一個(gè)高效、可靠的設(shè)計(jì)平臺(tái)。

-

IC設(shè)計(jì)

+關(guān)注

關(guān)注

38文章

1302瀏覽量

104280 -

電子系統(tǒng)

+關(guān)注

關(guān)注

0文章

438瀏覽量

31239 -

電源完整性

+關(guān)注

關(guān)注

9文章

211瀏覽量

20775

原文標(biāo)題:FEDS:從手動(dòng)到自動(dòng)化,破解電源完整性模擬難題!

文章出處:【微信號(hào):環(huán)旭電子 USI,微信公眾號(hào):環(huán)旭電子 USI】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

信號(hào)與電源完整性分析和設(shè)計(jì)培訓(xùn)

高速信號(hào)的電源完整性分析

信號(hào)完整性與電源完整性的仿真分析與設(shè)計(jì)

信號(hào)完整性與電源完整性的相關(guān)資料分享

信號(hào)完整性為什么寫電源完整性?

詳解信號(hào)完整性與電源完整性

信號(hào)完整性與電源完整性仿真分析

電源完整性分析與設(shè)計(jì)

信號(hào)完整性與電源完整性的仿真分析與設(shè)計(jì)

信號(hào)完整性與電源完整性的仿真

信號(hào)完整性與電源完整性的詳細(xì)分析

信號(hào)完整性和電源完整性的分析

如何利用全新互連系統(tǒng)提高電源完整性和信號(hào)完整性?

使用環(huán)旭電子FEDS平臺(tái)解決電源完整性模擬難題

使用環(huán)旭電子FEDS平臺(tái)解決電源完整性模擬難題

評(píng)論