人工智能、機器學習、云計算等應用的發(fā)展推動了智算/數(shù)據(jù)中心交換網(wǎng)絡數(shù)據(jù)傳輸速率的迅速增長,對高速有線收發(fā)機系統(tǒng)中的時鐘倍頻器的工作速度、抖動、面積和功耗等性能提出了更高的要求。基于環(huán)形振蕩器的注入鎖定時鐘倍頻器具有低抖動多相時鐘產(chǎn)生、緊湊布局、高能效和高魯棒性等優(yōu)勢,成為有線收發(fā)機系統(tǒng)中多相時鐘產(chǎn)生的有效解決方案。但注入鎖定時鐘倍頻器面臨固有注入相位誤差、最優(yōu)注入脈沖寬度及其隨PVT變化的漂移等挑戰(zhàn),限制了注入鎖定時鐘倍頻器性能的進一步提升和推廣應用。

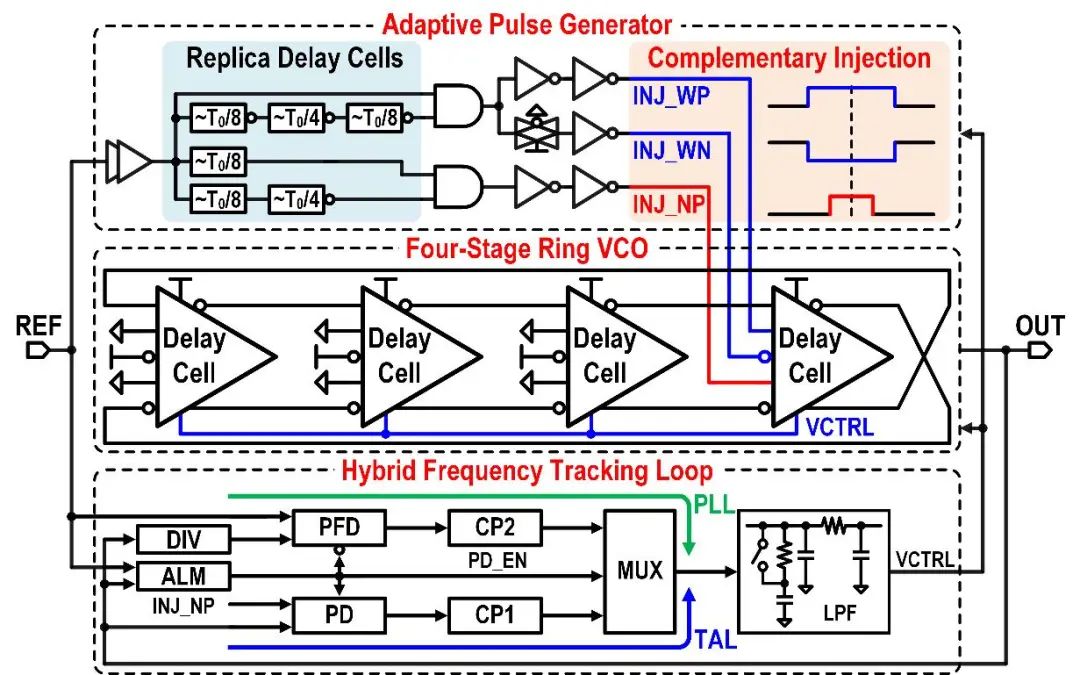

針對上述關(guān)鍵問題,微電子所高頻高壓中心劉新宇研究員/鄭旭強研究員團隊提出了一種新型基于環(huán)形振蕩器的注入鎖定時鐘倍頻器。團隊提出了寬脈沖注入和傳統(tǒng)窄脈沖注入相結(jié)合的互補注入方案,有效消除了窄脈沖注入引入的固有相位誤差,同時增強了相位噪聲抑制能力;設計了脈寬自適應注入脈沖產(chǎn)生電路,實現(xiàn)不同PVT下的最佳噪聲抑制;開發(fā)了基于失鎖檢測和環(huán)路選擇的頻率追蹤環(huán)路,擴展了頻率鎖定范圍。該注入鎖定振蕩器被集成到高速有線收發(fā)機,實現(xiàn)了112Gb/s PAM4調(diào)制數(shù)據(jù)傳輸。

研究成果以“A Low-Jitter and Low-Reference-SpurRing-VCO-Based Injection-Locked Clock Multiplier Utilizing aComplementary-Injection Scheme and an Adaptive Pulsewidth Adjustment”為題發(fā)表在集成電路設計領(lǐng)域頂級期刊Journal of Solid-State Circuits(JSSC)上,微電子所研究生王則棟為第一作者,微電子所鄭旭強研究員為通訊作者。該項研究得到了國家重點研發(fā)計劃和國家自然科學基金的支持。

論文鏈接:https://ieeexplore.ieee.org/document/10742924

圖1. 提出的基于環(huán)形振蕩器的注入鎖定時鐘倍頻器

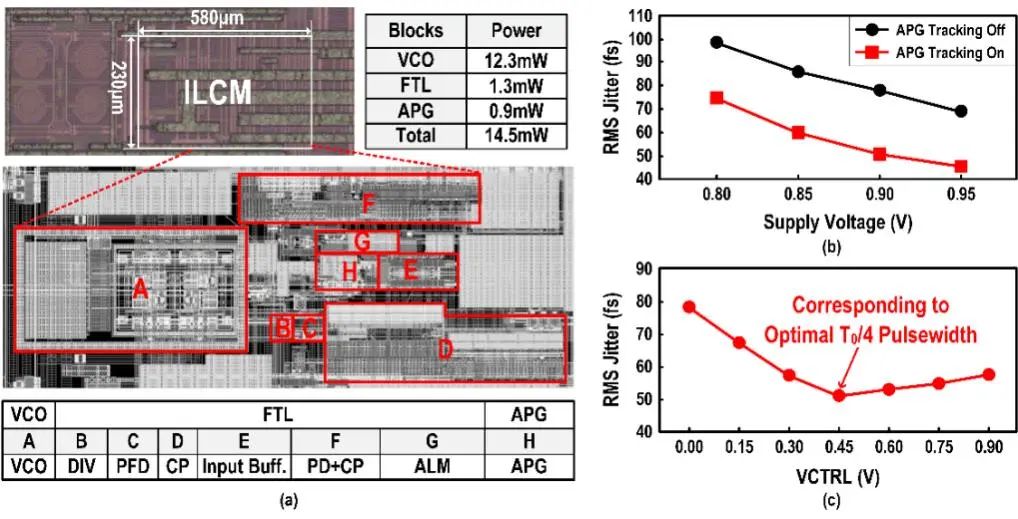

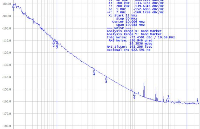

圖2. (a)芯片照片及各模塊功耗;(b)RMS抖動隨電源電壓變化圖;(c)RMS抖動隨VCO控制電壓變化圖

-

時鐘

+關(guān)注

關(guān)注

11文章

1746瀏覽量

131794 -

微電子

+關(guān)注

關(guān)注

18文章

388瀏覽量

41278 -

倍頻器

+關(guān)注

關(guān)注

8文章

80瀏覽量

35621

原文標題:微電子所在高性能注入鎖定時鐘倍頻器方面取得進展

文章出處:【微信號:中科院微電子研究所,微信公眾號:中科院微電子研究所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

倍頻器的作用是什么

射頻倍頻器與混頻器的區(qū)別

倍頻器的工作原理及作用

微電子所在超寬帶低噪聲集成電路設計領(lǐng)域取得新進展

倍頻器的技術(shù)原理和應用場景

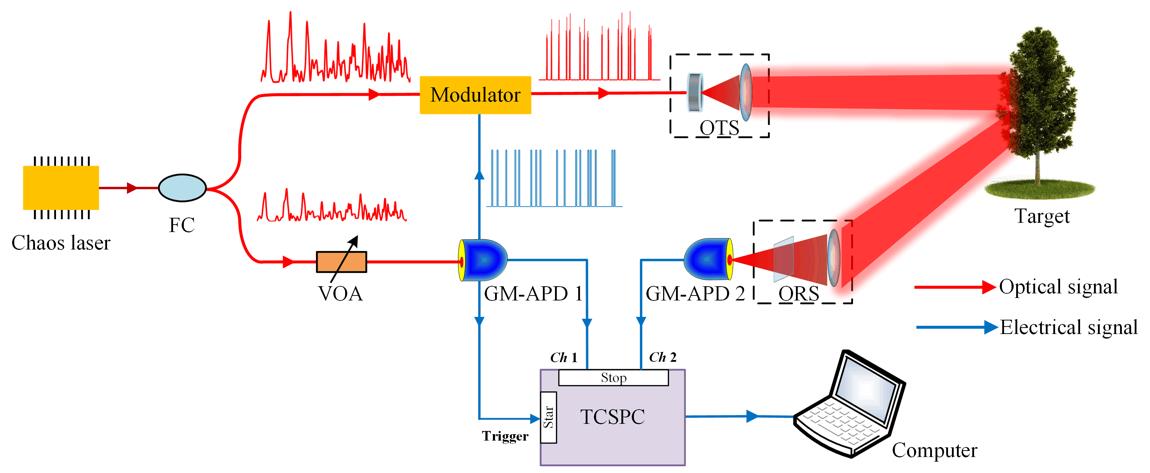

中科院微電子所在光子集成激光探感技術(shù)方面取得進展

左藍微電子高性能5G射頻濾波器項目啟動

外部倍頻器將LMX2820的工作頻率擴展至44GHz

帶內(nèi)部倍頻器的LMX2820與LMX2594

倍頻器與鎖相環(huán)的區(qū)別

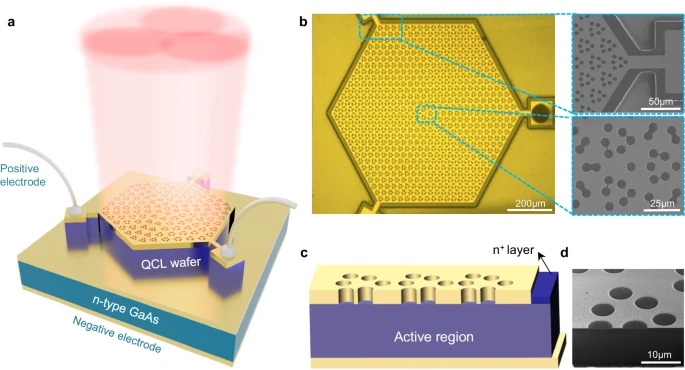

中科院半導體所在高性能電泵浦拓撲激光器研發(fā)方面獲進展

倍頻器的基本原理、分類及應用領(lǐng)域

上海微系統(tǒng)所在硅基磷化銦異質(zhì)集成片上光源方面取得重要進展

微電子所在高性能注入鎖定時鐘倍頻器方面取得進展

微電子所在高性能注入鎖定時鐘倍頻器方面取得進展

評論