您可點擊開發者分享|AMD Versal 自適應 SoC 器件 Advanced Flow 概覽(上)查看上篇文章。

新流程的使用指南

在 AMD Vivado DesignSuite 2024.2 版本中,Advanced Flow 自動為所有 AMD Versal 自適應 SoC器件啟用。請注意,Advanced Flow 不支持上一代 7 系列、AMD UltraScale FPGA 和 UltraScale plus 器件。

由于新流程包含在 Vivado 后端布局布線中并集成于用戶熟悉的 Vivado IDE,因此 Vivado 前端設計流程沒有變化,用戶無需學習新的設計環境。IP Integrator,IP 定制和 RTL 開發與舊流程相同。Project 和 non-project 流程以及相關的 Tcl 描述基本保持不變。

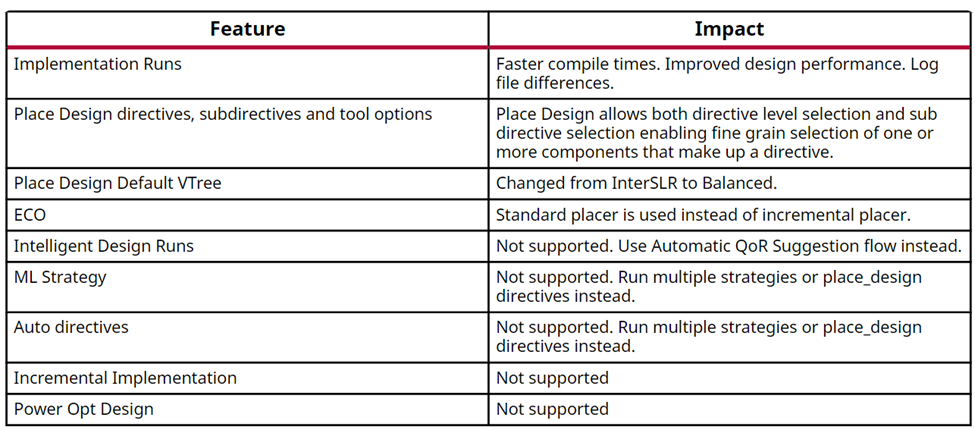

下表記錄了由于引入 Advanced Flow 而導致的 Implementation 中的一些關鍵變化。

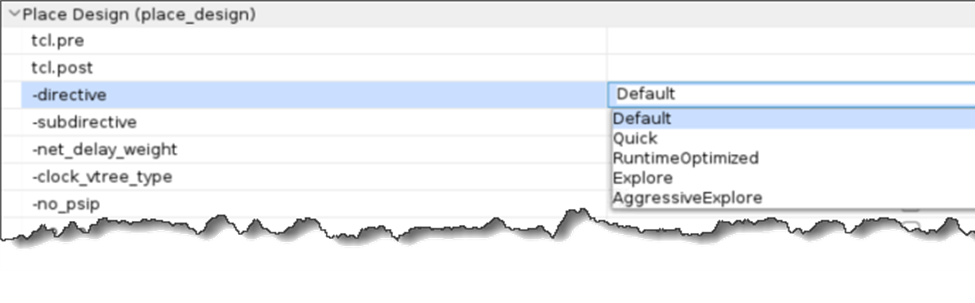

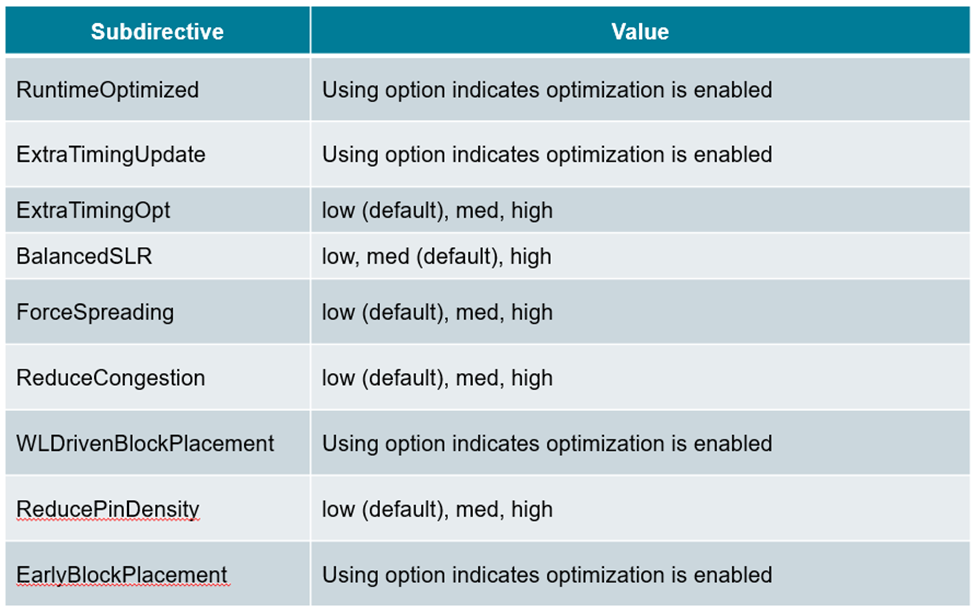

盡管整體設計流程不會發生變化,但 Placer Directive 存在顯著差異。

與先前 Vivado 版本不同,Advanced Flow 將 Directive列表簡化為下圖所示的五個:Quick、RuntimeOptimized、Default 和 Explore以及 AggressiveExplore。其中,前四個與以前一致,AggressiveExplore 為新添的 Directive。這些選項為 place_design 命令提供了不同的行為模式,并影響所有布局器階段。

Advanced Flow 對 Directive 使用與前相同的選項和語法。例如,place_design -directive AggressiveExplore 以最大的努力運行布局器以滿足時序約束,但代價是更長的運行時間。另一方面,選擇 Runtime Optimized 會犧牲一些滿足時序的努力來換取更快的編譯速度。與以前一樣,指令在工具設置菜單中可用,可用于創建Implementation 策略。

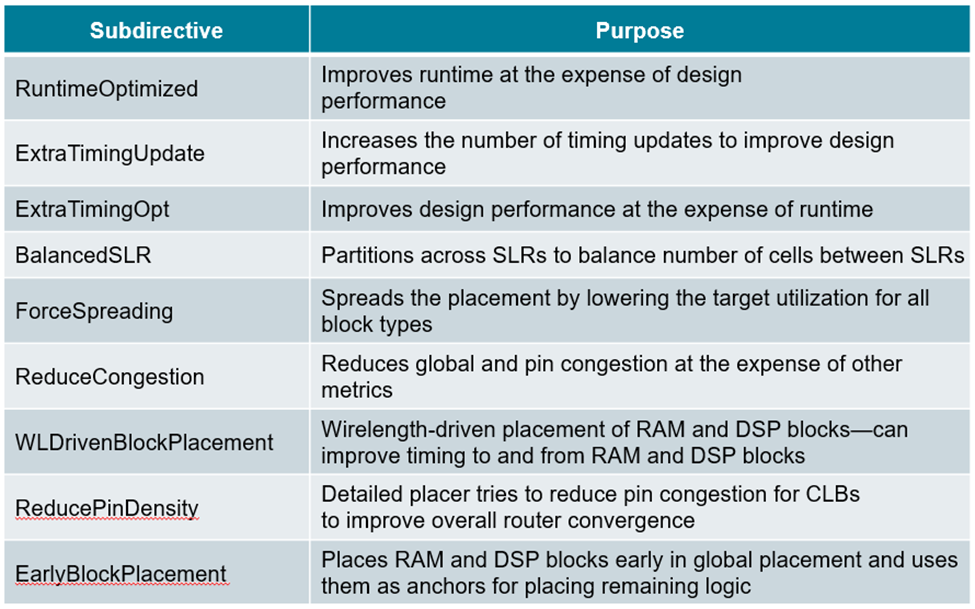

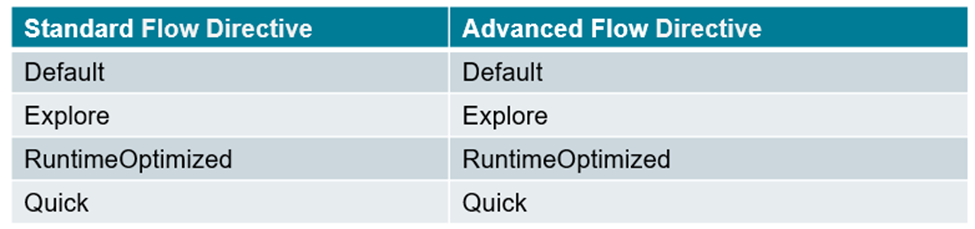

Subdirective 是 Advanced Flow 中的新布局選項。此選項提供對布局的不同階段的更細粒度控制:布局規劃(Floorplan)、全局布局(GPlace)和詳細布局(DPlace)。與 Directive 互斥使用不同,用戶可以同時應用多個Subdirective,這意味著您還可以將多個 Subdirective 與一個 Directive 選項組合起來以進行更廣泛的探索。

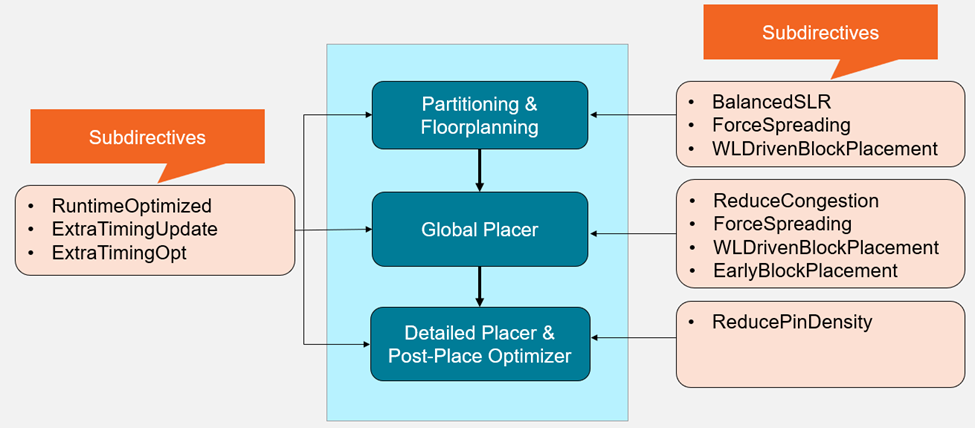

下面的表格顯示了當前支持的 Subdirective 列表及其主要用途。不同的 Subdirective 可以應用于布局的一個或多個階段。借助 Advanced Flow,這些 Subdirective 可以解鎖更多可能性,以探索不同的選項組合,從而增加極具挑戰性的設計的時序收斂可能性。這比原始單一的 Directive 選項涵蓋了更多的解決方案空間。

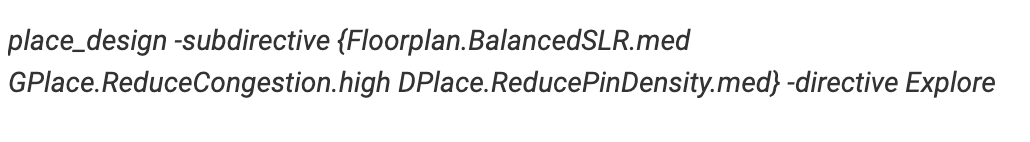

Tcl 用法示例:

每個 Subdirective 選項都以布局器階段名稱作為前綴,如果適用,后面會跟 high|med|low 的級別值。而有些只需要指定 Subdirective 表示啟用此優化,格式如下:

在此示例中,由于 -directive 選項是 Explore,布局器最初會為 Floorplan、GPlace 和 DPlace 的每個階段選擇 Explore 設置。然后,除了 Explore選 項之外,還會應用 Subdirective 選項。對于此示例,在 Floorplan 階段使用BalancedSLR 中級,在 GPlace 階段應用 ReduceCongestion 高級,在 DPlace 階段使用 ReducePinDensity 高級。

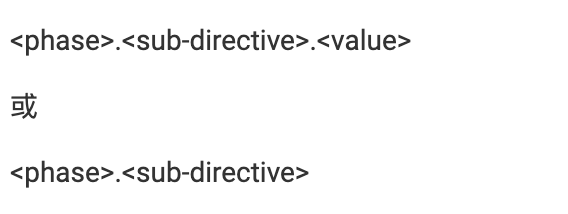

前面提到過,不同的 Subdirective 可以應用于不同的布局階段,了解每個布局階段可以應用哪些 Subdirective 非常重要。下圖將 Floorplanning,GPlace 和 DPlace 階段適用的 Subdirective 做了一個梳理:

在這里,我們看到左側的三個選項:RuntimeOptimized、ExtraTimingUpdate 和 ExtraTimingOpt 適用于所有布局階段。

在右側,我們可以看到哪些選項僅適用于某些階段。例如,BalancedSLR 只能在布局規劃階段的早期應用,因為它會影響設計的分區方式,后面的階段就太晚了。此外,像 ReducePinDensity 這樣的設置只能在 Detailed Placement 期間應用,因為它涉及在接近尾聲階段對單元布局進行微調。

對于不同 Subdirective 是否需要指定

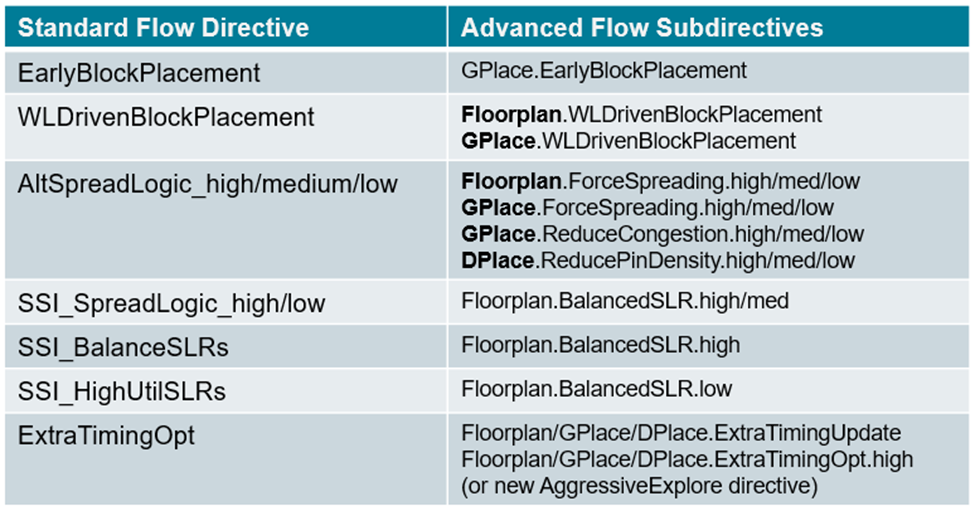

讓我們進一步看看舊流程(Standard Flow)的 Directive 如何映射到 Advanced Flow 中與其等效的 Subdirective。

如前所述,Versal 的 Advanced Flow 支持熟悉的 Default、Explore、RuntimeOptimized 和 Quick directive。

許多 Standard Flow Directive 可以使用 Subdirective 和其他布局器選項轉換為 Advanced Flow。一個簡單的例子是“EarlyBlockPlacement”,它直接映射到 Subdirective“Gplace.EarlyBlockPlacement”。

某些指令(如 Alt Spread Logic)需要更復雜的轉換,Alt Spread Logic 映射到所有布局器階段的多個子指令。

在某些情況下,Directive 被其他選項替換。Extra net delay high 和 Extra net delay low 分別被新的 Advanced Flow place_design 選項替換,該選項具有類似的名稱 net_delay_weight,取值 high 和 low。一個主要優點是,與額外的 -direcvite ExtraNetDelay 不同,-net_delay_weight可以與其他 Directive 和 Subdirective 一起使用,從而解鎖更多可能的組合。

另外,并非所有指令都可以轉換為 Advanced Flow 等效選項,如不支持的表格中所示。

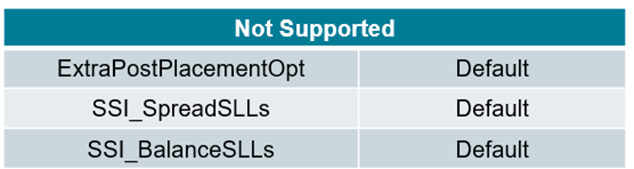

使用 Advanced Flow placer directive 實現時序收斂,請參考以下的推薦方法。

在第一組運行中,嘗試三個基本 Directive:Default、Explore 和 AggressiveExplore,看看是否有任何 Directive 符合時序要求。

如果時序要求不滿足,請使用 Run #1 中性能最佳的 directive,并與圖中所示的幾個關鍵 Subdirective 相結合。

如果第二組運行仍未產生時序收斂結果,請采用 Run #2 中性能最佳的組合,并應用如 Run #3 中所示的其他Subdirective。

這種有條不紊的方法比簡單地迭代整個 Directive 和 Subdirective 集合更有效,后者在編譯時間和計算資源方面成本極高。

請務必記住,Advanced Flow 不能替代良好的設計方法,檢查方法違規行為(report_methodology)也很重要,因為這些違規行為可能會導致時序收斂障礙。

舊版本的 AMD Versal 自適應 SoC 設計移植

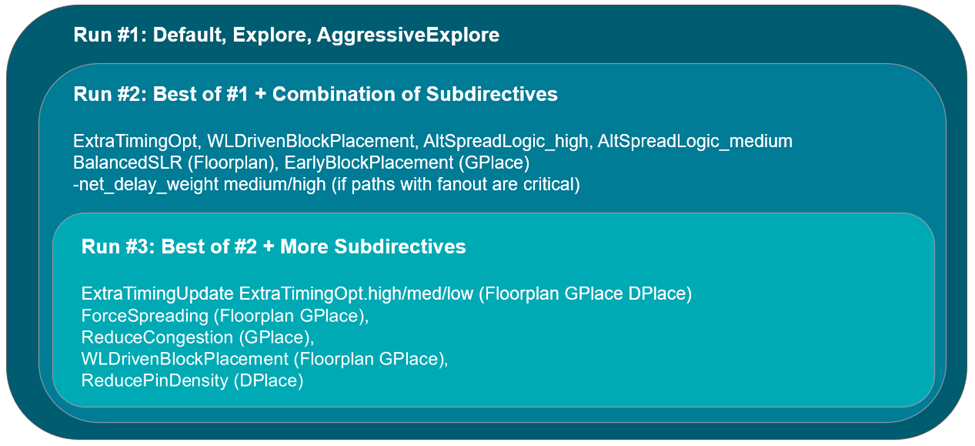

所有 AMD Versal 自適應 SoC工程升級到 2024.2 時,都需要切換到 Advanced Flow。如果您有一個 2024.1 Versal 的 AMD Vivado Design Suite 工程,在 2024.2 中打開此工程時,您將看到一個對話框,指示必須升級工程。

假設您已查看流程中的關鍵更改(例如 Intelligent Design Runs 和 Incremental compile 流程還不支持),并同意升級到 2024.2,最好先存檔您的項目或設計,因為此遷移不可逆,工具將重置所有的 Implementation run 并將選項設置為 Advanced Flow 布局和布線。

關于工程的 Implementation 策略,需要遵循一些實施指南:

為了便于項目流程遷移,大多數策略都直接在 Advanced Flow 中受支持,如前所述,布局器 Directive 映射到其等效的 Advanced Flow directive、subdirective 和布局器選項。

遇到不受支持的策略時,Vivado 會生成警告消息,并在選擇默認策略后繼續。

用戶自定義的策略無法自動轉換為其 Advanced Flow 等效策略,而是映射到默認策略。

可以使用新的布局器subdirective和選項創建新的用戶定義策略。策略編輯器完全支持 Advanced Flow。

如果使用 Tcl 命令的方式打開工程,設計將自動升級,并且消息將回顯到 Tcl 控制臺,通知您進度以及配置的選項和策略。DCP 文件 也需要升級。如果您將 place_design 之前的 DCP 添加到項目中,或者單獨打開 DCP,則 DCP 將在內存中自動讀取和升級。如果 DCP 是 place_design 完成后的,這將導致錯誤情況,因為 DCP 中保存的現有布局和布線數據庫與 Advanced Flow 不兼容。

在使用 non-project 模式的情況下,用戶可以自己管理源文件和設計過程。在執行 non-project Tcl 腳本期間,布局和布線過程中會出現一些含有“Advanced Flow”的 INFO 信息。

由于 Advanced Flow 僅適用于 Versal,因此非 Versal 項目不受此更改的影響。此外,如果您有一個 2024.1 設計,并且已經在使用 Advanced Flow 的 Early Access 版本,則應該也不會受到任何影響。

總結

本文介紹了 AMD Versal 自適應 SoC的 Advanced Flow,這是 AMD Vivado Design Suite2024.2 版本提供的一套新的布局布線功能。

Advanced Flow 采用改進的架構,可以更好地并行編譯分區,并采用新算法來減少布線擁塞,更好地處理具有大量全局時鐘的復雜設計布局。

這些改進縮短了整體設計周期,使您能夠在更短的時間內完成時序收斂,提高設計效率。

-

amd

+關注

關注

25文章

5493瀏覽量

134627 -

soc

+關注

關注

38文章

4202瀏覽量

219076 -

命令

+關注

關注

5文章

696瀏覽量

22107 -

Versal

+關注

關注

1文章

163瀏覽量

7710

原文標題:開發者分享|AMD Versal? 自適應 SoC 器件 Advanced Flow 概覽(下)

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【ALINX 技術分享】AMD Versal AI Edge 自適應計算加速平臺之 Versal 介紹(2)

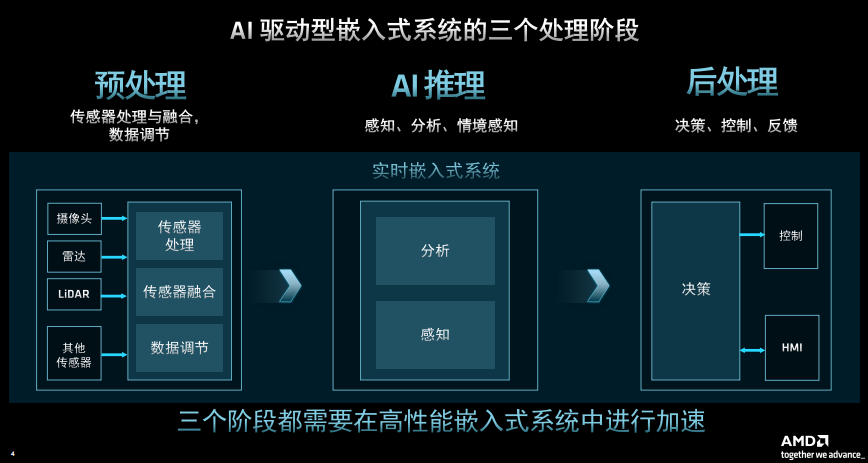

AMD Versal SoC刷新邊緣AI性能,單芯片方案驅動嵌入式系統

Versal? 自適應 SoC 助力 8K 處理 – 為 8K 做好準備(3)

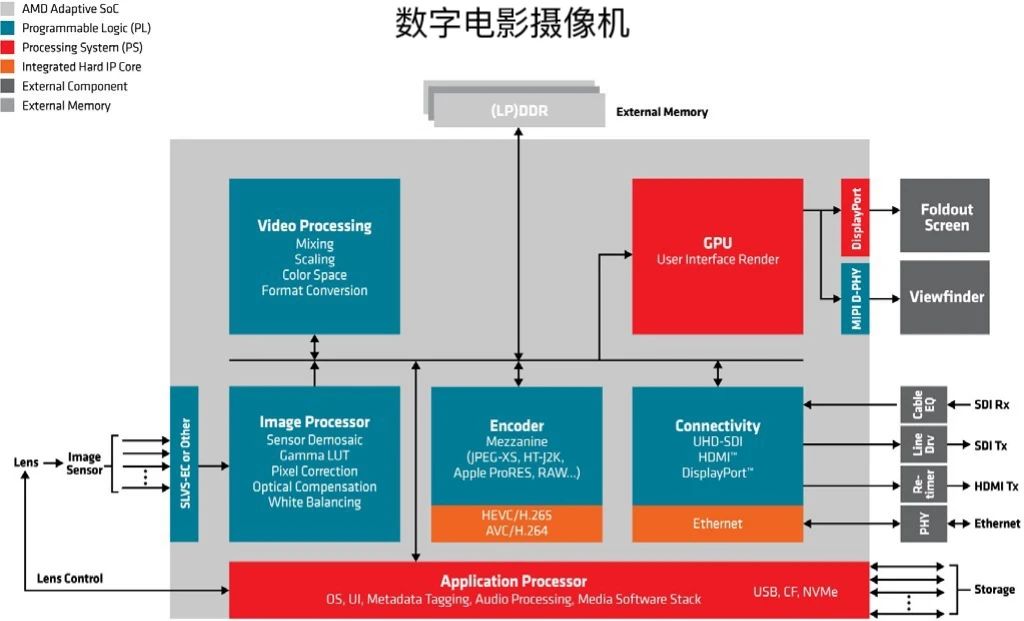

AMD率先推出符合DisplayPort? 2.1 8K視頻標準的FPGA和自適應SoC

AMD Versal SoC全新升級邊緣AI性能,單芯片方案驅動嵌入式系統

AMD發布第二代Versal自適應SoC,AI嵌入式領域再提速

第二代AMD Versal Prime系列自適應SoC的亮點

AMD Versal自適應SoC CPM5 QDMA的Tandem PCIe啟動流程介紹

AMD Versal自適應SoC DDRMC如何使用Micron仿真模型進行仿真

AMD Versal自適應SoC器件Advanced Flow概覽(上)

AMD Versal自適應SoC器件Advanced Flow概覽(下)

AMD Versal自適應SoC器件Advanced Flow概覽(下)

評論