1PlanAead引腳分配

這個例程的頂層源碼里有3個接口,即:

input ext_clk_25m, //外部輸入25MHz時鐘信號

input ext_rst_n, //外部輸入復(fù)位信號,低電平有效

output reg beep //蜂鳴器控制信號,1--響,0--不響

這3個信號都是FPGA引腳上定義和外部設(shè)備連接的信號,因此我們需要將這些信號和FPGA的引腳進(jìn)行映射。

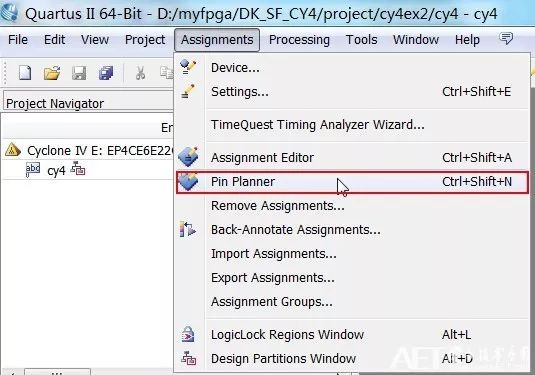

如圖7.5所示,點擊Quartus II菜單上的“Assignments à Pin Planner”選項。

圖7.5 Pin Planner菜單

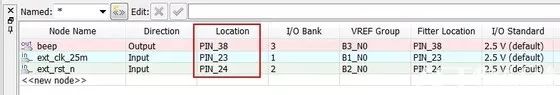

如圖7.6所示,在Pin Planner界面最下面出現(xiàn)的“Node Name”一列中,有我們的3個信號接口,這里“Location”一列可以輸入它們對應(yīng)FPGA的引腳;“I/O Standard”一列可以輸入I/O電平標(biāo)準(zhǔn),默認(rèn)雖然是2.5V,但由于我們原理圖上已經(jīng)把VCCIO連接3.3V,所以實際上輸出還是3.3V,我們不去設(shè)置它也行。

圖7.6 引腳分配

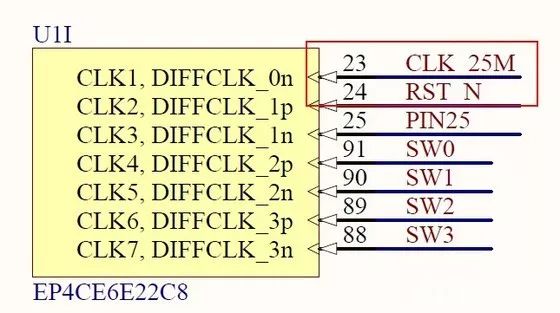

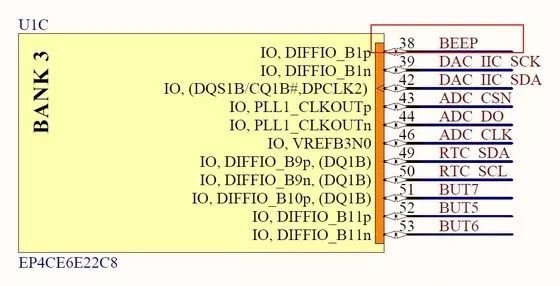

查看SF-CY4開發(fā)板的原理圖,如圖7.7和圖7.8所示,這里BEEP對應(yīng)FPGA引腳號是38,那么前面我們就在Location列輸入PIN_38;RST_N和CLK_25M分別為24和23,則輸入PIN_24和PIN_23。

圖7.7 時鐘和復(fù)位信號原理圖

圖7.8 蜂鳴器信號原理圖

2腳本直接引腳分配

Tcl(Tool Command Language),即工具命令語言。是一種好用易學(xué)的編程語言。在EDA工具中廣泛使用,幾乎所有FPGA開發(fā)工具都支持這種語言進(jìn)行輔助設(shè)計。例如這里我們就要嘗試用tcl腳本進(jìn)行FPGA的引腳分配。

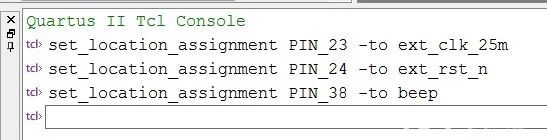

前面對ext_clk_25m的引腳分配,我們可以用如下語句實現(xiàn)。

set_location_assignment PIN_23 -to ext_clk_25m

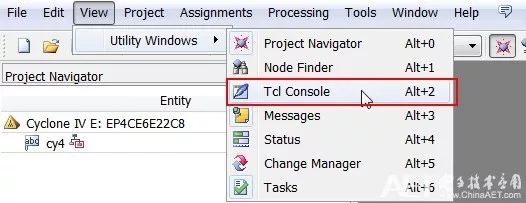

語法“set_location_assignment PIN_A –to B”是固定格式,A代表FPGA引腳號,B代表FPGA內(nèi)部的信號名稱。就這么簡單。這個腳本要寫到哪里?如圖7.9,點擊菜單欄“ViewàUtility WindowsàTcl Console”。

圖7.9 Tcl Console菜單

接著如圖7.10所示,我們在“Tcl Console”中輸入以下的3條引腳分配腳本,最后點擊“回車”。

圖7.10 tcl腳本輸入

此時,我們回到“Pin Planner”中,也可以看到所有引腳自動完成分配。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21797瀏覽量

606017 -

蜂鳴器

+關(guān)注

關(guān)注

12文章

893瀏覽量

46096

原文標(biāo)題:【精品博文】PWM蜂鳴器驅(qū)動之引腳分配

文章出處:【微信號:ChinaAET,微信公眾號:電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Xilinx FPGA無痛入門,海量教程免費下載

【OK210試用體驗】功能篇(5)Linux字符驅(qū)動之PWM蜂鳴器驅(qū)動

Xilinx FPGA入門連載12:PWM蜂鳴器驅(qū)動之引腳分配

勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載49:PWM蜂鳴器驅(qū)動之引腳分配

如何利用PWM驅(qū)動蜂鳴器

Renesas RA2L1開發(fā)板之pwm蜂鳴器設(shè)計方案分享

CH32V103基礎(chǔ)教程95-PWM驅(qū)動蜂鳴器

如何設(shè)計一款低成本的無源蜂鳴器驅(qū)動電路

無源蜂鳴器常規(guī)驅(qū)動電路設(shè)計

如何設(shè)計低成本蜂鳴器?

嵌入式PWM驅(qū)動蜂鳴器實驗

蜂鳴器

單片機(jī)編輯庫三之蜂鳴器

PWM蜂鳴器驅(qū)動之引腳分配

PWM蜂鳴器驅(qū)動之引腳分配

評論