隨著實施基于云的服務和機器到機器通信所產(chǎn)生的數(shù)據(jù)呈指數(shù)級增長,數(shù)據(jù)中心面臨重重挑戰(zhàn)。

這種增長毫無減緩態(tài)勢,有業(yè)界專家預測內(nèi)部數(shù)據(jù)中心機器對機器流量將會超出所有其他類型流量多個數(shù)量級。這種顯著增長給數(shù)據(jù)中心帶來三個主要挑戰(zhàn):

●數(shù)據(jù)速度– 接收與處理數(shù)據(jù)所需的時間增強了數(shù)據(jù)的接收和處理能力,實現(xiàn)高速傳輸。這使數(shù)據(jù)中心可支持近乎實時的性能。

●數(shù)據(jù)種類– 從圖像與視頻這樣的結(jié)構(gòu)化數(shù)據(jù)到傳感器與日志數(shù)據(jù)這樣的非結(jié)構(gòu)化數(shù)據(jù),可將不同格式的數(shù)據(jù)傳輸進來。

● 數(shù)據(jù)量– 所有用戶提供的數(shù)據(jù)量。

對于眾多應用來說,應對這些挑戰(zhàn)需要數(shù)據(jù)中心之間的直接通信。例如,提供索引、分析、數(shù)據(jù)同步、備份與恢復服務。為支持數(shù)據(jù)中心間的通信,需要使用非常大的數(shù)據(jù)管道,同時,用于在這些管道間傳輸數(shù)據(jù)的網(wǎng)絡通常稱為數(shù)據(jù)中心互連 (DCI)。

DCI 發(fā)揮著舉足輕重的作用,有助于數(shù)據(jù)中心部署規(guī)模擴展,支持更多數(shù)數(shù)據(jù)中心以在給定地理區(qū)域內(nèi)鋪開服務。當然,隨著數(shù)據(jù)中心數(shù)量的增加,它們之間的互連程度也會隨之增強。

要想在數(shù)據(jù)中心內(nèi)實現(xiàn) DCI,既可使用專用接口盒,也可使用傳統(tǒng)的傳輸裝置。使用專用接口盒能在外部數(shù)據(jù)中心(線路側(cè))與數(shù)據(jù)中心內(nèi)部網(wǎng)絡(客戶側(cè))之間提供接口。

由于數(shù)據(jù)中心內(nèi)存有敏感信息,例如財務信息、健康信息以及其他業(yè)務的關(guān)鍵信息,因而數(shù)據(jù)安全性至關(guān)重要。安全漏洞會讓數(shù)據(jù)中心所有者喪失信心與信任并造成收入損失。最糟糕的是,如果安全漏洞十分顯著,還可能造成法律或監(jiān)管后果,從而影響運營。

因此,無論是在數(shù)據(jù)中心內(nèi)部還是在數(shù)據(jù)中心間的傳輸過程中,信息安全保障都是頭等大事。這就要求 DCI 實現(xiàn)方案能在數(shù)據(jù)進出數(shù)據(jù)中心時支持對數(shù)據(jù)進行加密或解密。

當前的 DCI 實現(xiàn)方案采用以下技術(shù)之一:

●Bulk Layer 1 安全方案:利用類似于 AES256 的技術(shù)對整個內(nèi)容進行加密和認證。這是目前為止最具成本效益的方式,能為大型點對點數(shù)據(jù)管道提供安全性。

● IEEE 802.1 AE 定義的 MACsec:可對數(shù)據(jù)包進行單獨加密,也可在硬件中輕松處理。MACsec 可在 Layer 2 中提供安全性。

在 DCI 互連盒中,通常只使用兩種安全技術(shù)中的一種。然而,隨著數(shù)據(jù)中心數(shù)量的增加,找到可實現(xiàn)這兩種安全方法的解決方案十分必要,讓使用不同安全方法的數(shù)據(jù)中心間能夠靈活地進行通信。這需要 DCI 平臺具有靈活性且易于配置,可從支持一種安全解決方案到支持另一種安全解決方案。有了這種靈活性,使用不同廠商技術(shù)的數(shù)據(jù)中心之間就能進行通信。

盡管新型數(shù)據(jù)中心的數(shù)量快速增加,但現(xiàn)有數(shù)據(jù)中心在線路側(cè)與客戶側(cè)均有部署,故也采用全新的標準。DCI 互連盒必須足夠靈活才能應對多個升級周期,跨越多代網(wǎng)絡接口。升級網(wǎng)絡設備的相關(guān)成本是這種跨代升級的部分推動力,例如,100Gbps 傳輸卡的成本是與它相似的切換端口成本的 100 倍。因此,從成本角度來看,每三年更換這些設備并不劃算。該功能有助于數(shù)據(jù)中心運營商將 DCI 互連盒脫離升級周期。

DCI 互連盒架構(gòu)

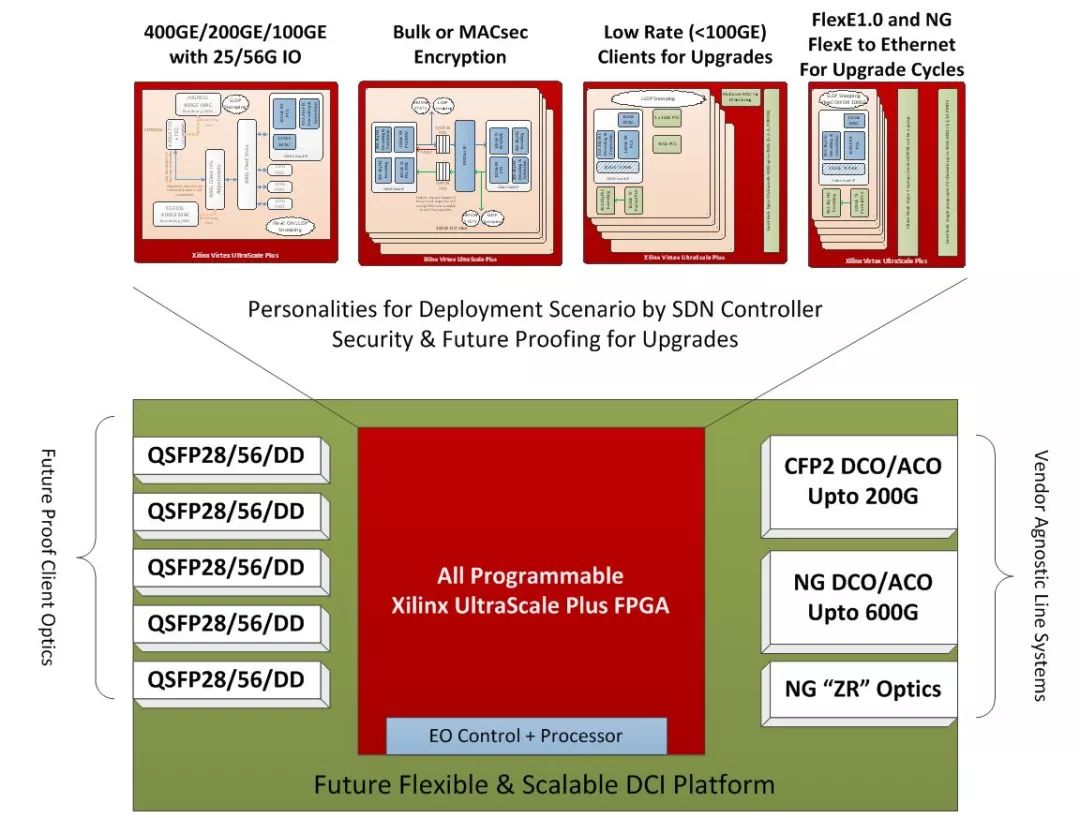

出于對不同的安全技術(shù)與常規(guī)升級周期間歇的支持,DCI 互連盒架構(gòu)需要能夠適應部署功能要求,同時根據(jù)技術(shù)與標準變化實現(xiàn)簡單演進。

圖 1 - DCI 互連盒情景圖。

要想實現(xiàn)對標準的適應性并為演進發(fā)展提供支持,就需要可支持多種數(shù)字相干光學 (DCO) 線路側(cè)接口的架構(gòu)。越來越多地將 DCO 格式部署為可插拔格式,并且能夠支持不同廠商線路側(cè)接口的特性實現(xiàn)了最大的靈活性。

客戶側(cè)接口則需要支持 10GE 至 400GE 的以太網(wǎng)速率,以及像 FlexE 的更新標準。而要將客戶側(cè)與線路側(cè)進行連接,所需的解決方案不僅要提供接口功能,還要能實現(xiàn)應用所需的安全解決方案。

諸如賽靈思 UltraScale+ FPGA 的可編程邏輯可為 DCI 互連盒設計人員提供多種優(yōu)勢。可編程邏輯 IO 的高靈活性能實現(xiàn)任意到任意系統(tǒng)間的接口功能,允許客戶側(cè)和線路側(cè)接口具備必要的 PHY 支持。

可編程邏輯的并行特性還可實現(xiàn)算法的流水線化,以獲得最優(yōu)吞吐量。得益于可編程邏輯架構(gòu)的并行特性,因為消除了傳統(tǒng)的系統(tǒng)瓶頸,該解決方案還具備更好的確定性。

此外,可編程邏輯也可實現(xiàn)現(xiàn)場升級,在采用標準時,可支持全新協(xié)議修訂版本的部署。可編程邏輯的這種可升級能力使 DCI 盒可以具備應用所需特性。該變更可通過 SDN 控制器來編排,因此,基于 FPGA 的 DCI 盒極具可塑性。在當今 SDN 控制的網(wǎng)絡環(huán)境中,這樣一種基于應用的 DCI 盒特性會形成極大優(yōu)勢。

就 FPGA 應用的開發(fā)而言,存在多種可用來加速功能性的由高級軟件定義的環(huán)境。它們包括 SDAccel?、SDNet? 與 SDSoC? 設計環(huán)境,統(tǒng)稱為 SDx。這些環(huán)境支持使用高層次綜合對 FPGA 應用進行開發(fā)。當與重配置加速棧 (Reconfigurable Acceleration Stack) 相結(jié)合時,開發(fā)人員就可以使用業(yè)界標準框架與庫集成數(shù)據(jù)中心。

圖 2 – SDx 開發(fā)環(huán)境。

總 結(jié)

數(shù)據(jù)中心正在經(jīng)歷顯著增長,并通過使用 DCI 這樣的技術(shù)使之間的互連變得越來越緊密。DCI 互連盒可提供互連功能與數(shù)據(jù)事務處理的安全保護功能,同時還可在 DCI 與數(shù)據(jù)中心功能與標準演進發(fā)展的同時支持路徑升級。FPGA,例如賽靈思 UltraScale+ 系列,可提供靈活的高性能解決方案,并可使用 SDx 工具鏈加速該解決方案的開發(fā),提供高級設計環(huán)境。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605998 -

Xilinx

+關(guān)注

關(guān)注

71文章

2171瀏覽量

122132

原文標題:使用 Xilinx 可編程邏輯實現(xiàn)數(shù)據(jù)中心互連

文章出處:【微信號:xilinx_inc,微信公眾號:賽靈思】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

用TMAG5328電阻器和電壓可編程霍爾效應開關(guān)實現(xiàn)可編程性和診斷

可編程電源如何編程

什么是現(xiàn)場可編程邏輯陣列?它有哪些特點和應用?

高性能沖擊可編程陣列邏輯電路數(shù)據(jù)表

標準高速可編程陣列邏輯電路數(shù)據(jù)表

高性能沖擊可編程陣列邏輯電路數(shù)據(jù)表

高性能Impact X可編程陣列邏輯電路TIBPAL16C數(shù)據(jù)表

可編程邏輯器件TPLD1201數(shù)據(jù)表

使用Xilinx可編程邏輯實現(xiàn)數(shù)據(jù)中心互連

使用Xilinx可編程邏輯實現(xiàn)數(shù)據(jù)中心互連

評論