近日,國際領先的定制化芯片(ASIC)設計方案提供商及DDR控制器和物理層IP供應商——燦芯半導體(上海)有限公司(以下簡稱“燦芯半導體”)對外宣布推出基于SMIC40LL工藝的第二代DDR低功耗物理層IP,該IP與第一代的低功耗DDR PHY相比面積減少20%,功耗減少37%,物理實現時間減少50%。

第二代DDR低功耗物理層IP采用先進的雙排IO結構,并采用了多項邏輯和物理的優化手段,延遲線面積減少20%,減少了每個DQ/DQS的時延誤差, 消除了之前物理實現的蛇形走線及每個DQ上不同數目的或者不同推力的緩沖器等問題,進而提高了硅利用率,提高了DDR的速度,并且減少了功耗。

第二代DDR低功耗物理層IP具有如下特性:

■ 基于SMIC 40LL工藝

■ 支持DDR3/3L/3U/LPDDR3 1333Mbps,DDR2/LPDDR2 1066Mbps

■ 支持PHY evaluation training或者 software training模式

■ 支持RD DQS下降沿training模式

“燦芯半導體具有10年的芯片設計經驗和豐富的DDR IP技術積累,燦芯的YouPHY-DDR IP覆蓋SMIC28HKMG、SMIC 40LL、SMIC 55LL、130nm等工藝, 20多顆含有燦芯DDR IP的芯片成功流片,涉及DTV、AP 、導航、SSD及NVDIMM等諸多應用領域,得到客戶的充分肯定,”燦芯半導體首席技術官莊志青說,“我們將不斷進行架構創新,提高服務質量,改進實現流程,從而為客戶提供更有競爭力的解決方案。”

據了解,燦芯半導體(上海)有限公司,是一家國際領先的定制化芯片(ASIC)設計方案提供商及DDR控制器和物理層IP供應商,定位于55nm/40nm/28nm以下的高端系統級芯片(SoC)設計服務與一站式交鑰匙(Turn-Key)服務。燦芯半導體為客戶提供從源代碼或網表到芯片成品的一站式服務,并致力于為客戶復雜的ASIC設計提供一個高性價比、低風險的完整的芯片整體解決方案。

-

半導體

+關注

關注

334文章

27705瀏覽量

222643 -

控制器

+關注

關注

112文章

16445瀏覽量

179453 -

寄存器

+關注

關注

31文章

5363瀏覽量

121164 -

燦芯半導體

+關注

關注

0文章

54瀏覽量

12657

原文標題:業界領先:燦芯半導體推出第二代DDR低功耗物理層IP

文章出處:【微信號:zjpark,微信公眾號:你好張江】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

芯原與新基訊發布第二代5G RedCap/4G LTE雙模調制解調器IP

第二代AMD Versal Premium系列器件的主要應用

第二代AMD Versal Premium系列產品亮點

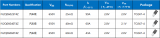

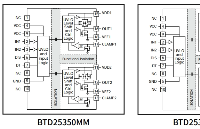

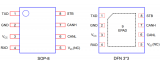

上海貝嶺推出第二代高精度基準電壓源

AMD推出第二代Versal Premium系列

一加正式發布第二代東方屏,獲全球首個DisplayMate A++認證

高通推出第二代驍龍4s移動平臺

Power Master 半導體推出第二代 1200V eSiC MOSFET

聚辰基于第二代NORD工藝平臺推出業界最小尺寸高可靠NOR Flash系列芯片

瞻芯電子推出三款第二代650V SiC MOSFET產品

瑞芯微第二代8nm高性能AIOT平臺 RK3576 詳細介紹

瞻芯電子開發的3款第二代650V SiC MOSFET通過了車規級可靠性認證

燦芯半導體推出第二代DDR低功耗物理層IP

燦芯半導體推出第二代DDR低功耗物理層IP

評論