PCI總線是一種地址和數(shù)據(jù)復(fù)用的總線,即地址和數(shù)據(jù)占用同一組信號線AD。PCI總線的所有信號都與時鐘信號同步,及所有的信號的變化都發(fā)生在時鐘的上升沿,或者在時鐘上升沿進行采樣。

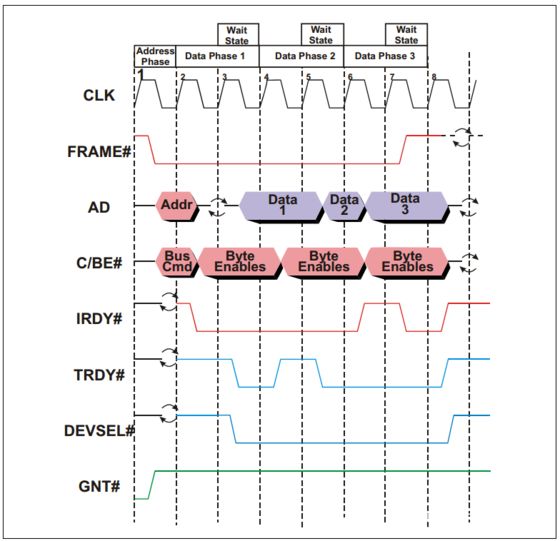

如下圖所示,除了時鐘信號CLK和數(shù)據(jù)地址復(fù)用信號AD之外,PCI總線至少還應(yīng)包括FRAME#(用于表示一次數(shù)據(jù)傳輸?shù)钠鹗迹/BE#(Command/Byte Enable)、IRDY#(Initiator Ready for data)、TRDY#(Target ready)、DESEL#(Device Selec,片選信號,用于選擇PCI設(shè)備)和GNT#(Grant)信號等。

注:完整的信號時序圖,請參考PCI Spec。信號名后面的#表示該信號低電平有效。

下面來介紹一個簡單的例子,主機接收來自特定從機的數(shù)據(jù)。

在第一個時鐘上升沿,F(xiàn)RAME#和IRDY#都為inactiv表明總線當前處于空閑狀態(tài)。與此同時,某個設(shè)備的GNT#信號處于active,表明總線總裁器已經(jīng)選定當前設(shè)備為下一個initiator(可以理解為主機)。

在第二個時鐘上升沿,F(xiàn)RAME#被initiator拉低,表明新的事務(wù)(Transaction)已經(jīng)開始。與此同時,地址和命令被依次發(fā)送到AD上,總線上面的所有其他設(shè)備(從機)都會鎖存這些信息,并檢查地址和命令是否與自己匹配。

在第三個時鐘上升沿,IRDY#處于active狀態(tài),表明主機準備就緒,可以接收數(shù)據(jù)了。AD信號上的旋轉(zhuǎn)的箭頭表示AD信號目前處于三態(tài)狀態(tài)(處于輸出和輸入的轉(zhuǎn)換狀態(tài)),即Turn‐around cycle。需要注意的是,此時的TRDY#應(yīng)當處于inactive狀態(tài),以保證Turn‐around cycle順利進行。

在第四個時鐘上升沿,PCI總線上的某個從機確認身份,并依次將DEVSEL#信號和TRDY#拉低,并將相應(yīng)的數(shù)據(jù)輸出到AD上。此時,F(xiàn)RAME#信號為active狀態(tài),表明這并不是最后一個數(shù)據(jù)。

在第五個時鐘上升沿,TRDY#處于inactive狀態(tài),表明從機尚未就緒,因此所有的操作暫緩一個時鐘周期(或者說插入了一個Wait State)。PCI總線最多允許8個這樣的Wait State。

在第六個時鐘上升沿,從機向主機發(fā)送第二個數(shù)據(jù)。此時,F(xiàn)RAME#信號依舊為active狀態(tài),表明這并不是最后一個數(shù)據(jù)。

在第七個時鐘上升沿,IRDY#處于inactive狀態(tài),表明主機尚未就緒,再次插入一個Wait State。但是此時從機依舊可以向AD上發(fā)送數(shù)據(jù)。

在第八個時鐘上升沿,AD上的第三個數(shù)據(jù)被發(fā)送至主機,由于此時FRAME#信號被拉高,即inactive,表明這是本次事務(wù)(Transaction)的最后一個數(shù)據(jù)。此后,所有的控制信號均被拉高,處于inactive狀態(tài),AD、FRAME#和C/BE#處于三態(tài)狀態(tài)。

信號時序

-

pci總線

+關(guān)注

關(guān)注

1文章

203瀏覽量

31930 -

時鐘

+關(guān)注

關(guān)注

11文章

1746瀏覽量

131801

原文標題:【博文連載】PCIe掃盲——一個典型的PCI總線周期

文章出處:【微信號:ChinaAET,微信公眾號:電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

一文看懂PCI總線與PXI總線有什么區(qū)別

PCI總線特性及信號說明

基于IP核的PCI總線接口設(shè)計與實現(xiàn)

PCI總線接口芯片9054及其應(yīng)用

基于PCI總線的CPLD實現(xiàn)

pci總線標準|pci總線規(guī)范下載

基于FPGA的PCI總線接口設(shè)計

PCI總線原理

一種DSP與PCI總線的接口設(shè)計

PCI總線與PXI總線之間的特點,性能比較

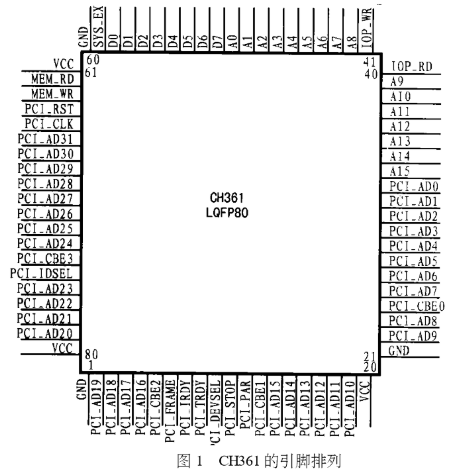

PCI總線通用接口芯片CH361的功能特點、引腳功能和典型應(yīng)用

一個典型的PCI總線周期

一個典型的PCI總線周期

評論