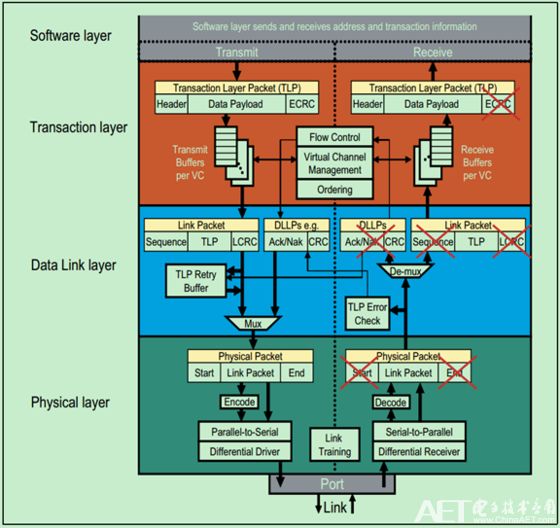

首先,回顧一下,之前看了很多遍的PCIe的Layer結(jié)構(gòu)圖:

PCIe中的物理層主要完成編解碼(8b/10b for Gen1&Gen2,128b/130b for Gen3 and later)、擾碼與解擾碼、串并轉(zhuǎn)換、差分發(fā)送與接收、鏈路訓(xùn)練等功能。其中鏈路訓(xùn)練主要通過(guò)物理層包Ordered Sets來(lái)實(shí)現(xiàn)。

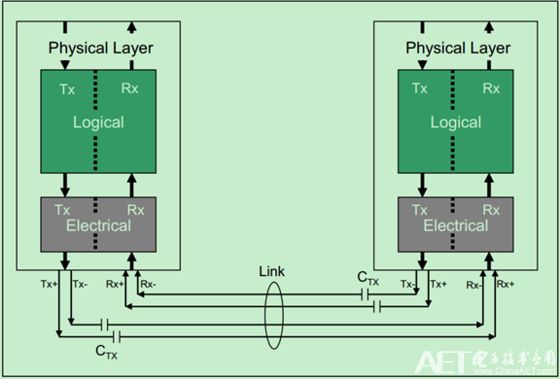

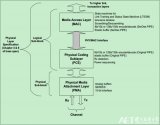

PCIe Spec將物理層分為兩個(gè)部分——邏輯子層和電氣子層,如下圖所示:

如上圖所示,PCIe物理層實(shí)現(xiàn)了一對(duì)收發(fā)差分對(duì),因此可以實(shí)現(xiàn)全雙工的通信方式。需要注意的是,PCIe Spec只是規(guī)定了物理層需要實(shí)現(xiàn)的功能、性能與參數(shù)等,置于如何實(shí)現(xiàn)這些卻并沒(méi)有明確的說(shuō)明。也就是說(shuō),廠商可以根據(jù)自己的需要和實(shí)際情況,來(lái)設(shè)計(jì)PCIe的物理層。下面將以Mindshare書中的例子來(lái)簡(jiǎn)要的介紹PCIe的物理層邏輯部分,可能會(huì)與其他的廠商的設(shè)備的物理層實(shí)現(xiàn)方式有所差異,但是設(shè)計(jì)的目標(biāo)和最終的功能是基本一致的。

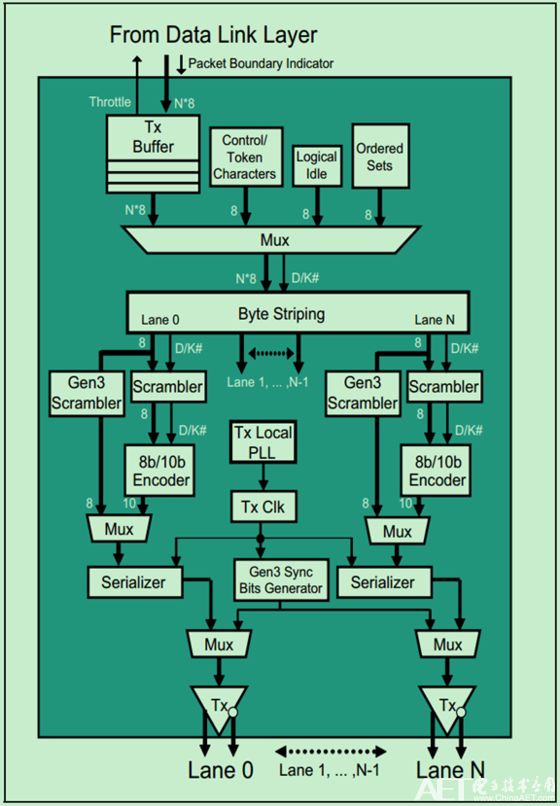

物理層邏輯子層的發(fā)送端部分的結(jié)構(gòu)圖如下圖所示:

在進(jìn)行8b/10b編碼之前,Mux會(huì)對(duì)來(lái)自數(shù)據(jù)鏈路層的數(shù)據(jù)中插入一些內(nèi)容,如用于標(biāo)記包邊界或者Ordered Sets的控制字符和數(shù)據(jù)字符。為了區(qū)分這些字符,Mux為其對(duì)應(yīng)上一個(gè)D/K#位(Data or Kontrol)。

注:圖中還包含了Gen3的一些實(shí)現(xiàn),不過(guò)這里只介紹Gen1 & Gen2,并不會(huì)介紹Gen3。如果大家感興趣的,可以去閱讀Mindshare的書籍或者參考PCIe Gen3的Spec。

Byte Striping將來(lái)自Mux的并行數(shù)據(jù)按照一定的規(guī)則(后面會(huì)詳細(xì)地說(shuō))分配到各個(gè)Lane上去。隨后進(jìn)行擾碼(Scrambler)、8b/10b編碼、串行化(Serializer),然后是差分發(fā)送對(duì)。

其中擾碼器(Scrambler)是基于偽隨機(jī)碼(Pesudo-Random)的異或邏輯(XOR),由于是偽隨機(jī)碼,所以只要發(fā)送端和接收端采用相同的算法和種子,接收端便可以輕松地恢復(fù)出數(shù)據(jù)。但是,如果發(fā)送端和接收端由于某些原因?qū)е缕涔?jié)拍不一致了,此時(shí)便會(huì)產(chǎn)生錯(cuò)誤,因此Gen1和Gen2的擾碼器(Scrambler)會(huì)周期性地被復(fù)位。

注:關(guān)于8b/10b的原理和作用,在我之前的博文中有所介紹。所以接下來(lái)的文章中不會(huì)重復(fù)介紹這些內(nèi)容,但是會(huì)簡(jiǎn)要地介紹PCIe中的8b/10b的實(shí)現(xiàn)細(xì)節(jié)和要點(diǎn)。

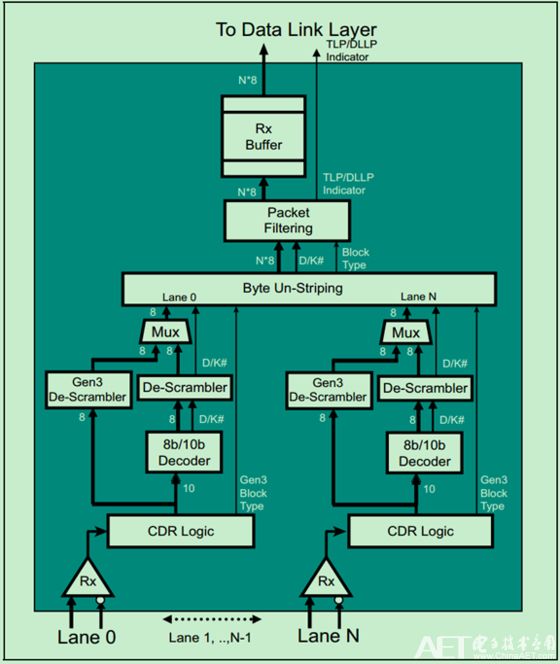

物理層邏輯子層的接收端部分的結(jié)構(gòu)圖如下圖所示:

由于PCIe采用的是一種Embeded Clock(借助8b/10b)機(jī)制,因此接收端在接收到數(shù)據(jù)流時(shí),首先要從中恢復(fù)出時(shí)鐘信號(hào),這正是通過(guò)CDR邏輯來(lái)實(shí)現(xiàn)的。如上圖所示,接收端的邏輯基本上都是與發(fā)送端相對(duì)應(yīng)的相反的操作。這里就不在詳細(xì)地介紹了。

-

全雙工

+關(guān)注

關(guān)注

0文章

44瀏覽量

10510 -

PCIe

+關(guān)注

關(guān)注

15文章

1260瀏覽量

83184 -

物理層

+關(guān)注

關(guān)注

1文章

152瀏覽量

34544

原文標(biāo)題:【博文連載】PCIe掃盲——物理層邏輯部分基礎(chǔ)(一)

文章出處:【微信號(hào):ChinaAET,微信公眾號(hào):電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

HAL庫(kù)的串口收發(fā)函數(shù),HAL的串口DMA方式下不能實(shí)現(xiàn)獨(dú)立的全雙工通信嗎?

全雙工無(wú)線系統(tǒng)的實(shí)現(xiàn)

通信基礎(chǔ)知識(shí):?jiǎn)喂ぃ?b class='flag-5'>雙工,全雙工

如何對(duì)PCIe 3.0接收機(jī)物理層進(jìn)行測(cè)試?

串口通信的物理層與協(xié)議層的相關(guān)資料推薦

用于RS485全雙工的LPUART,以半雙工方式連接時(shí)出現(xiàn)回聲怎么解決?

WiMAX物理層技術(shù)特征及其OFDM和OFDMA技術(shù)的應(yīng)用

PCIe物理層的基本概念

PCIe物理層接口定義了物理層中的,媒介層和物理編碼子層之間的統(tǒng)一接口

通信接口利用RS-485物理層實(shí)現(xiàn)飛機(jī)防雷保護(hù)

SWIPT MIMO全雙工系統(tǒng)中的物理層通信優(yōu)化綜述

ZLG致遠(yuǎn)電子新一代車載以太網(wǎng)全雙工物理層轉(zhuǎn)換器發(fā)布

如何搞定通信物理層?物理層包含哪些內(nèi)容?如何落地實(shí)現(xiàn)呢?

PCIe物理層實(shí)現(xiàn)了一對(duì)收發(fā)差分對(duì),可以實(shí)現(xiàn)全雙工的通信方式

PCIe物理層實(shí)現(xiàn)了一對(duì)收發(fā)差分對(duì),可以實(shí)現(xiàn)全雙工的通信方式

評(píng)論