設計背景:

在我們工程設計中,有時會需要到上升沿和下降沿這么一個說法,通過上升沿和下降沿來驅動一個電路,那么學習邊沿檢測就非常的重要了。

設計原理:

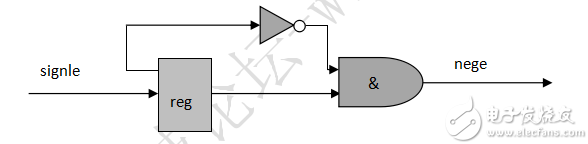

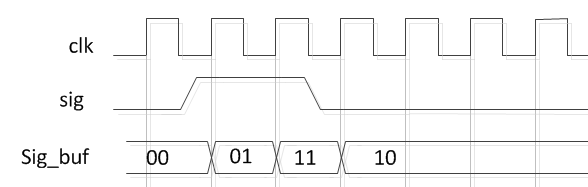

在學習邊沿檢測前我們先學習一下下面的電路,這樣方便我們學習,邊沿檢測。

這個電路的意思就是,輸入一個信號后我們經過一個寄存器,然后把這個寄存器的輸出,和下次輸出的值取反后相與,那么我們就可以這么想,如果一個高平的值經過這個寄存器后延遲一個上升沿后輸出也為高電平,那么當輸出的時候會有一個新的電平值,也就是一個電平的到來,然后通過低電平的值取反后和寄存器輸出的高電平值得與得到一個高電平的脈沖值,然后對低電平轉化為高電平也是一樣的道理,這樣我們就可以得到時鐘上升沿和下降沿的高脈沖,這樣就得到了我們設計的目的。

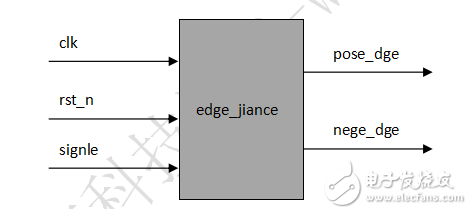

設計架構圖:

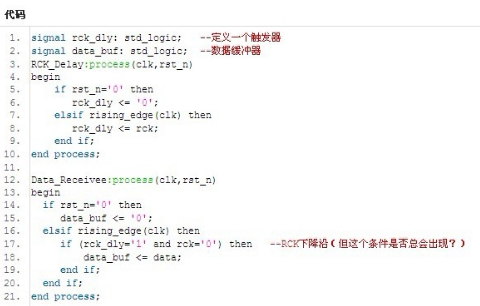

設計代碼:

設計模塊

0moduleedge_jiance(clk,rst_n,signle,nege_dge,pose_dge);

1

2 inputclk;

3 inputrst_n;

4 inputsignle;//輸入信號

5

6 outputnege_dge;//輸出下降沿的脈沖

7 outputpose_dge;//輸出上升沿的脈沖

8

9 reg[1:0]signle_s;

10 always@(posedgeclk ornegedgerst_n)

11 if(!rst_n)

12 begin

13 signle_s <=2'b11;

14 end

15 else

16 begin

17 signle_s[0]<=signle;//把輸入信號給一個寄存器

18 signle_s[1]<=signle_s[0];

19 end

20

21 assignpose_dge =signle_s[0]&&~signle_s[1];//取反相與得到上 升沿的高脈沖

22 assignnege_dge =~signle_s[0]&&signle_s[1];//取反相與得到下 降沿的高脈沖

23endmodule

測試模塊

0`timescale1ns/1ps

1

2moduleedge_tb();

3

4 regclk;

5 regrst_n;

6 regsignle;

7

8 wirenege_dge;

9 wirepose_dge;

10

11 initialbegin

12 clk =1'b1;

13 rst_n =1'b0;

14 signle <=1'b1;//復位賦值

15

16 #100.1rst_n =1'b1;

17

18 #36signle <=1'b1;//模擬下降沿

19 #36signle <=1'b0;

20

21 #100

22 #36signle <=1'b0;//模擬上升沿

23 #36signle <=1'b1;

24

25 #100

26 $stop;

27 end

28

29 always#10clk =~clk;//產生晶振時鐘

30

31 edge_jiance edge_dut(//模塊例化

32 .clk(clk),

33 .rst_n(rst_n),

34 .signle(signle),

35 .nege_dge(nege_dge),

36 .pose_dge(pose_dge)

37 );

38endmodule

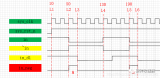

仿真圖:

我們模擬的上升沿和下降沿在仿真中可以清楚的看到,然后我們通過邊沿檢測電路,可以得出我們一個高電平的上升沿,和一個低電平的下降沿。

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606052

發布評論請先 登錄

相關推薦

FPGA設計中的邊沿檢測問題

FPGA學習系列:12. 邊沿檢測設計

FPGA學習系列:12. 邊沿檢測設計

評論