設計背景:

分頻在fpga的設計中一直都擔任著很重要的角色,而說到分頻,我相信很多人都已經想到了利用計算器來計算達到想要的時鐘頻率,但問題是僅僅利用計數(shù)器來分頻,只可以實現(xiàn)偶數(shù)分頻,而如果我需要三分頻,五分頻,七分頻等等奇數(shù)類分頻,那究竟怎么辦呢?在這里,讓我介紹一個可以實現(xiàn)任意整數(shù)分頻的方法,這個辦法也是同樣利用了計數(shù)器來計算,當是跟偶數(shù)分頻不一樣的地方是任意整數(shù)分頻利用了兩個計數(shù)器來實現(xiàn)。

設計原理:

本次設計主要是設計一個可調的分頻器,我可以設置其參數(shù),可以調節(jié)其輸出的占空比,占空比的意思就是高電平所占周期的多少。我們通知計算高電平的時間和低電平的時間來實現(xiàn),其實就是我們用兩個計數(shù)器來控制的。

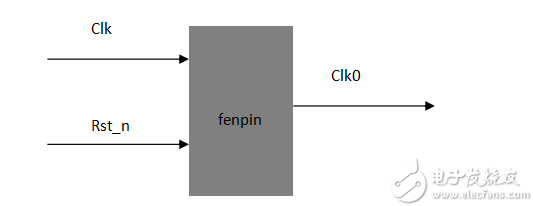

設計架構圖:

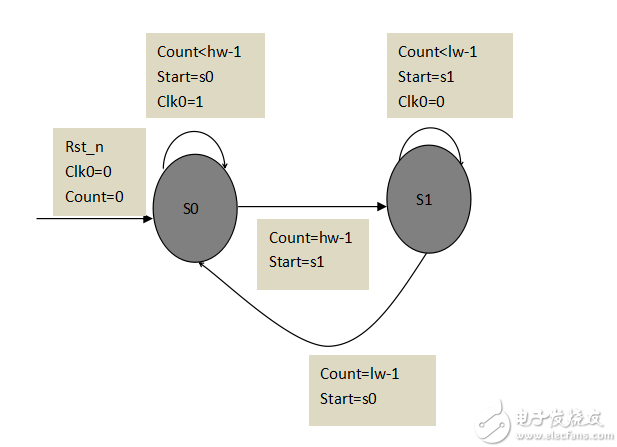

狀態(tài)轉移圖

通過對兩個計數(shù)器的計數(shù),一個計算到了跳轉下一個狀態(tài),等下一計數(shù)器計數(shù)到了又調回第一個狀態(tài),從而完成任意分頻器的設計。

設計代碼:

設計模塊

0modulefenpinqi(clk,rst_n,clk0);

1 inputclk;

2 inputrst_n;

3

4 outputregclk0;

5

6 parameterHW =7;//分一個高位7

7 parameterLW =3; //低電平為3 也就是5M的時鐘

8

9 localparams0 =1'b0;//定義兩個狀態(tài)

10 localparams1 =1'b1;

11

12 regstate;

13 reg[2:0]count;

14

15 always@(posedgeclk ornegedgerst_n)

16 if(!rst_n)

17 begin

18 state <=1'b0;

19 count <=3'b0;

20 clk0 <=1'b0;

21 end

22 else

23 begin

24 case(state)

25 s0:begin

26

27 if(HW +1>1) //判斷是否HW為0

28 if(count <HW -1)//計數(shù)器計數(shù)高電平

29 begin

30 clk0 <=1'b1;//產生高電平

31 count <=count +1'b1;

32 end

33 else

34 begin

35 count <=1'b0;

36 state <=1;

37 end

38 end

39 s1:begin

40 if(LW +1>1)//判斷是否LWW為0

41 if(count <LW -1) //計數(shù)器計數(shù)低電平

42 begin

43 clk0 <=1'b0;//產生低電平

44 count <=count +1'b1;

45 end

46 else

47 begin

48 count <=1'b0;

49 state <=0;

50 end

51 end

52 default:state <=0;

53 endcase

54 end

55endmodule

測試模塊

0`timescale1ns/1ps

1 modulefenpinqi_tb();

2

3 regclk;

4 regrst_n;

5

6 wireclk0;//定義輸出為wire型

7

8 parameterHW =5;

9 parameterLW =1;

10

11 initialbegin

12 clk =1'b1;

13 rst_n =1'b0;

14

15 #200.1rst_n =1'b1;

16 #2000$stop;

17 end

18 always#10clk =~clk;//產生50M時鐘

19

20 fenpinqi #(.HW(HW),.LW(LW))//例化,我們可以在這里改變占空比, 和頻率

21 fenpinqi_dut(

22 .clk(clk),

23 .rst_n(rst_n),

24 .clk0(clk0)

25 );

26 endmodule

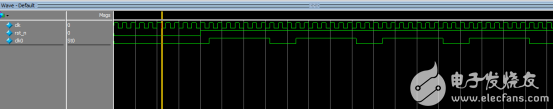

仿真圖:

圖中我們通過數(shù)上升沿的個數(shù)可以看到輸出clk0的輸出為高7,低3,符合我們的設計。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605999

發(fā)布評論請先 登錄

相關推薦

基于FPGA的通用數(shù)控分頻器設計方案

基于FPGA的任意數(shù)值分頻器的設計

基于FPGA的任意分頻器設計

50%占空比任意分頻器verilog實現(xiàn)方法

基于FPGA 的等占空比任意整數(shù)分頻器的設計

基于CPLD/FPGA的多功能分頻器的設計與實現(xiàn)

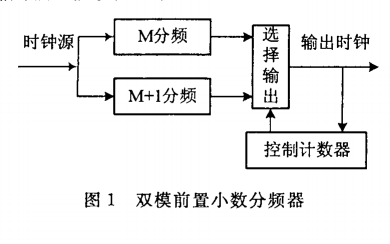

FPGA實現(xiàn)小數(shù)分頻器

用Verilog實現(xiàn)基于FPGA的通用分頻器的設計

如何使用FPGA進行任意小數(shù)分頻器的設計

FPGA分頻器的設計方法

FPGA學習-分頻器設計

FPGA學習系列:13. 任意分頻器設計

FPGA學習系列:13. 任意分頻器設計

評論