半加器

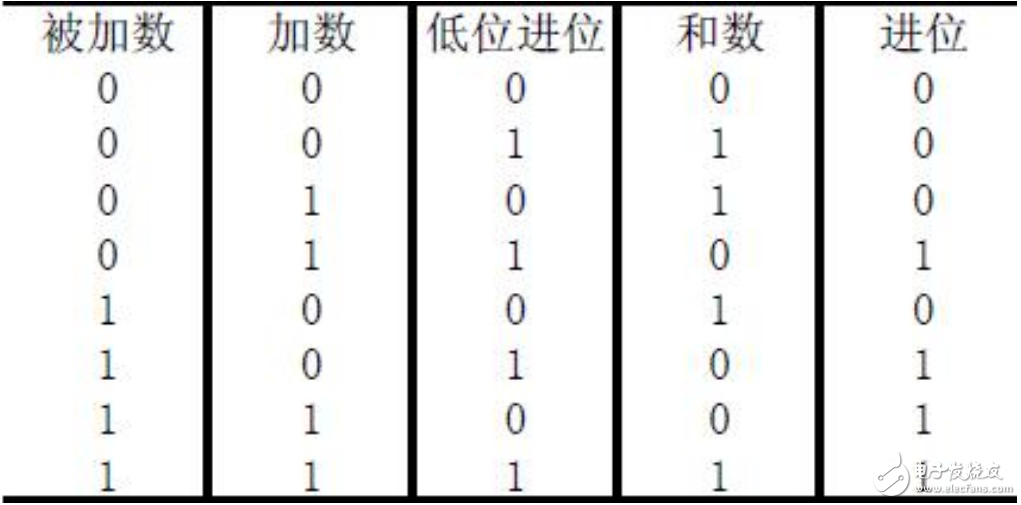

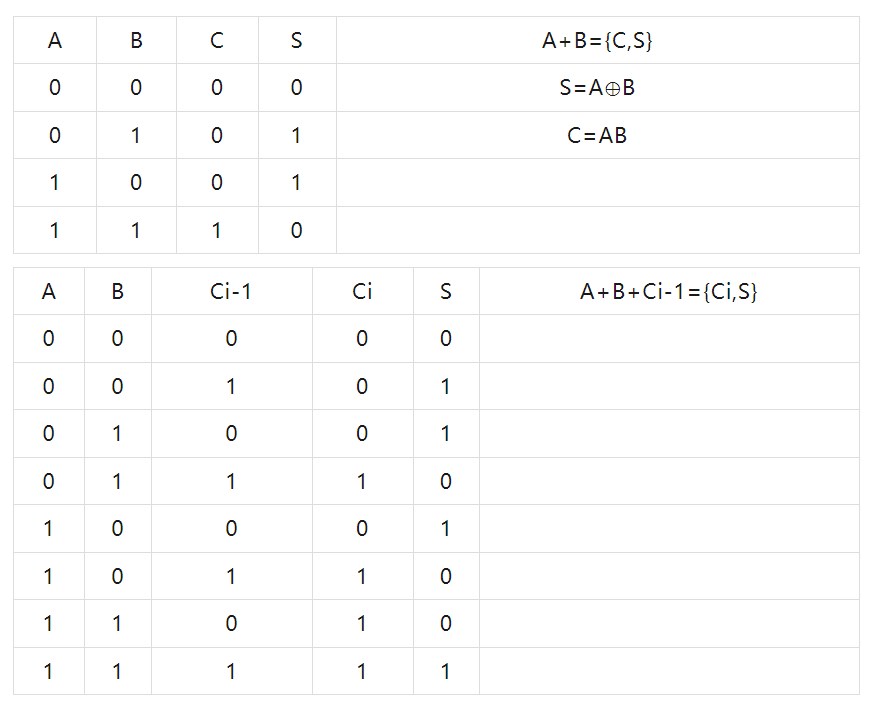

半加器+半加法和全加法是算術運算電路中的基本單元,它們是完成1位二進制相加的一種組合邏輯電路。一位加法器的真值表見表1.1;由表中可以看見,這種加法沒有考慮低位來的進位,所以稱為半加。半加器就是實現表1.1中邏輯關系的電路。被加數A加數B和數S進位C0000011010101101

表1.1一位半加法器真值表

全加器

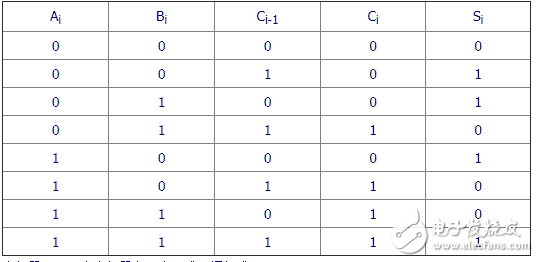

全加器能進行加數、被加數和低位來的進位信號相加,并根據求和結果給出該位的進位信號。根據它的功能,可以列出它的真值表,如表1.2所示。

半加器和全加器的區別

1、半加器

在數學系統中,二進制加法器是它的基本部件之一。

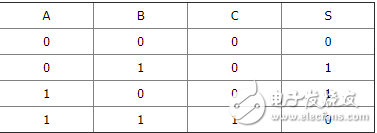

半加器(半加就是只求本位的和,暫不管低位送來的進位數)的邏輯狀態表

其中,A和B是相加的兩個數,S是半加和數,C是進位數。

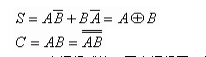

由邏輯狀態表可寫出邏輯式:

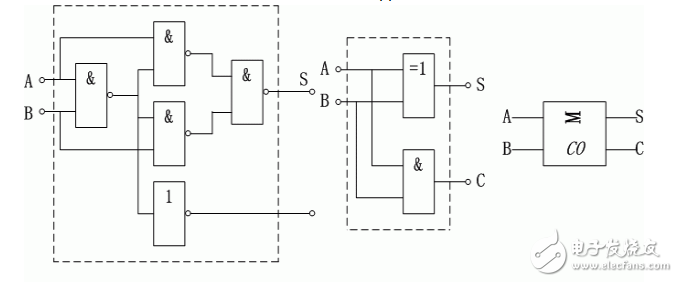

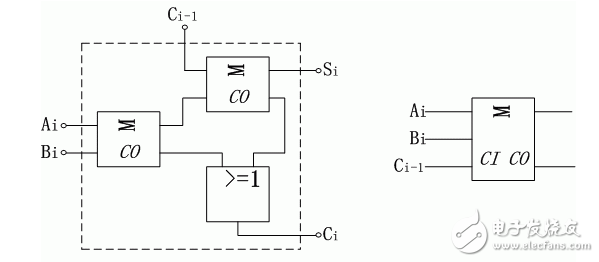

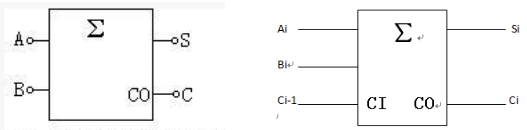

由邏輯式就可畫出邏輯圖,如下圖(a)和(b)所示,由一個“異或“門和一個”與“門組成。半加器是一種組合邏輯電路,其圖形符號如下圖(c)所示。

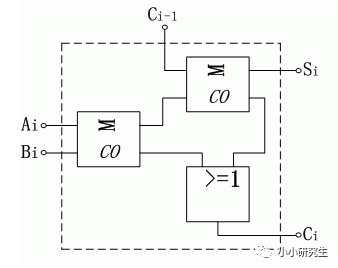

2、全加器

當多位數相加時,半加器可用于最低位求和,并給出進位數。第二位的相加有兩個待加數和,還有一個來自前面低位送來的進位數。這三個數相加,得出本位和數(全加和數)和進位數。這種就是“全加“,下表為全加器的邏輯狀態表。

全加器可用兩個半加器和一個“或“門組成。

如上圖(a)所示。和在第一個半加器中相加,得出的結果再和在第二個半加器中相加,即得出全加和。兩個半加器的進位數通過”或“門輸出作為本位的進位數。全加器也是一種組合邏輯電路,其圖形符號如上圖(b)所示。

-

全加器

+關注

關注

10文章

62瀏覽量

28562 -

半加器

+關注

關注

1文章

29瀏覽量

8824

發布評論請先 登錄

相關推薦

半加器和全加器的原理及區別(結構和功能)

半加器和全加器的原理及區別(結構和功能)

評論