摘要:雙精度浮點乘法部件是高性能CPU的核心運算部件之一。描述了使用Cadence Stratus HLS工具設計和實現雙精度浮點乘法部件,探索新設計方法學在關鍵路徑延時調整、數據路徑優化以及低功耗優化等問題的解決方法,并探討如何將新的設計流程結合到原有項目開發中等問題。最終,高階綜合設計的RTL,在28 nm工藝下綜合實現頻率為2.5 GHz、面積為28 211 μm2,基本滿足高性能微處理器的開發要求,增強了在項目中更加廣泛地使用新設計方法學的信心。

0 引言

數字多媒體的廣泛應用、互聯網的高速發展、人工智能等新興領域的蓬勃興起,對通用處理器的計算能力要求越來越高。采用更加復雜的算法設計、探索效率更高的架構有助于提升通用處理器的性能。然而在傳統的寄存器傳輸級(Register Transfer level,RTL)設計流程中,設計人員完成運算功能設計時需消耗大量時間在狀態機設計、流水棧劃分和調整、端口協議、存儲設計等復雜、難以驗證和優化的部分。而且由于RTL抽象層次較低,需要大量的時間和資源驗證RTL的功能,最后導致較長的設計周期。Stratus高階綜合工具(High-level Synthesis,HLS)基于高階綜合設計方法學,將設計層次抽象到算法級,將設計的低值且復雜的領域交給工具自動完成,設計人員能夠將更多的時間應用在算法設計、優化、架構探索等高價值領域,提高設計效率,專注產品質量的提升。本文基于Cadence公司的高階綜合工具Stratus設計和實現高頻低功耗的雙精度浮點乘法模塊,并在此過程中探討高階綜合完成產品前端設計、驗證、優化、性能評估的方法和流程。

1 HLS應用流程

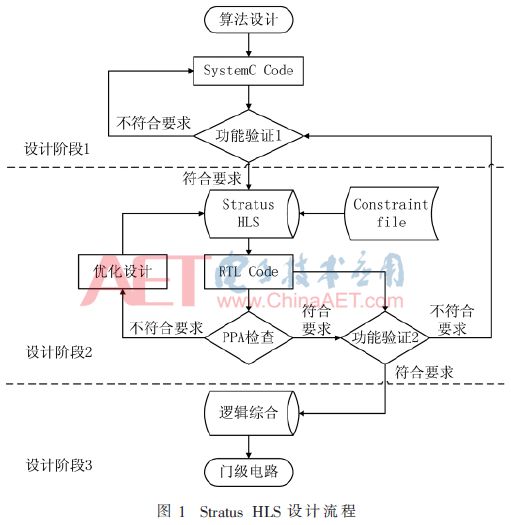

Stratus HLS將設計抽象到算法級,對算法做硬件微架構實現的構想后,使用高級語言SystemC/C/C++描述設計,并在高級語言層對設計做充分的非時序功能驗證,如圖1中設計階段1所示。在設計階段2,首先需根據設計目標設置高階綜合的約束文件及工藝庫。然后將設計階段1完成的SystemC代碼和約束文件灌入Stratus HLS工具,由工具完成狀態機、寄存器插入、流水線級數設置等控制電路,生成符合時序、面積、性能要求的RTL代碼。最后對RTL代碼做PPA檢查,選擇使用邏輯綜合工具再一次對HLS生成的RTL代碼做性能評估,如果符合要求,則開始做RTL的完整功能驗證。如果PPA檢查不能達到目標要求,則需要對關鍵路徑進行分析、優化,此時可以充分利用HLS工具自帶的優化功能加速優化設計迭代的完成過程。功能驗證正確后,則可以進入設計階段3,邏輯綜合后,設計交由后端做邏輯實現。

2 Fmul64 SystemC設計

雙精度浮點乘法運算部件是通用CPU內最基本運算部件之一,其應用要求高階綜合獲得RTL設計滿足2.5 GHz的高頻率,三站流水,并且其面積和功耗較小。此部分將介紹Fmul64的主要結構和SystemC設計方法。

2.1 Fmul64_hls總體結構

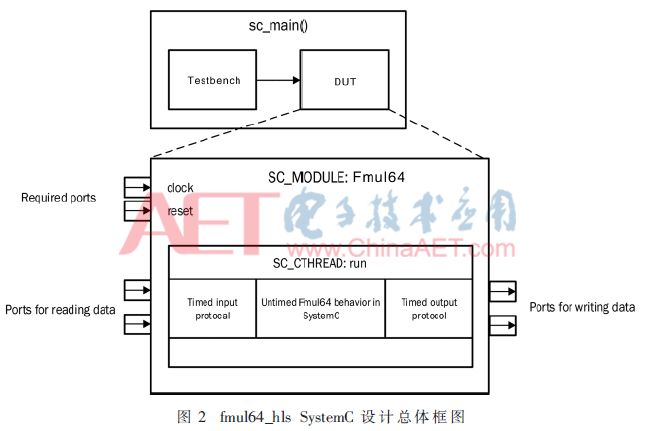

Fmul64的SC設計總體框圖如圖2所示,sc_main()是SystemC設計的top文件,連接測試環境Testbench和待測設計DUT。DUT即Fmul64,用SystemC語言中的SC_MODULE類實現,作為此次設計的頂層模塊,同時在此模塊內定義模塊的端口、時鐘信號、復位信號、輸入端口、輸出端口等,作為設計的頭文件,并包含在其他文件內使用。SystemC語言提供兩個方法用于設計功能的描述:SC_METHOD和SC_CTHREAD。其中SC_METHOD用于組合邏輯電路實現,內部不能包括wait()語句,而要實現的Fmul64是流水線設計,所以使用SC_CTHREAD用于乘法運算功能的實現,函數命名為run。

2.2 SC_CTHREAD方法實現

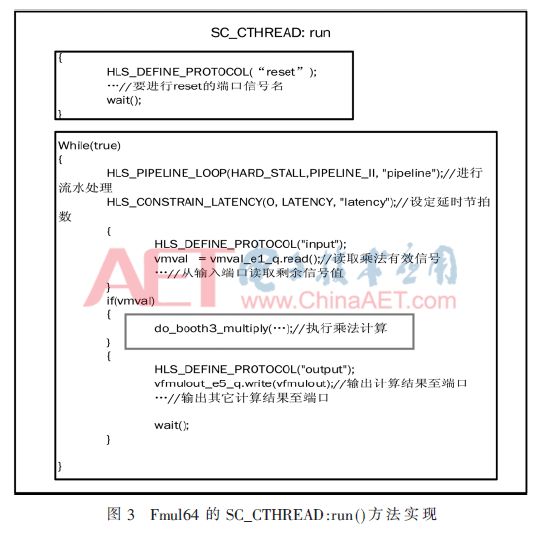

SC_CTHREAD進程實現如圖3所示,首先設置需要復位的信號和復位值,然后是定義無限循環語句,并在內部調用輸入輸出信號的讀寫函數和含3階波茲編碼的乘法運算函數do_booth3_multply。這里用HLS命令HLS_PIPELINE_LOOP設置設計類型,即吞吐率參數PIPELINE_Ⅱ設為1,即將Fmul64_hls設置為流水線型設計,并用HLS_CONSTRAINT_LATENCY設定流水線拍數LATENCY為3。Stratus HLS允許將吞吐率和延遲使用宏定義的形式,便于架構探索時更改參數。

2.3 Fmul64行為級實現

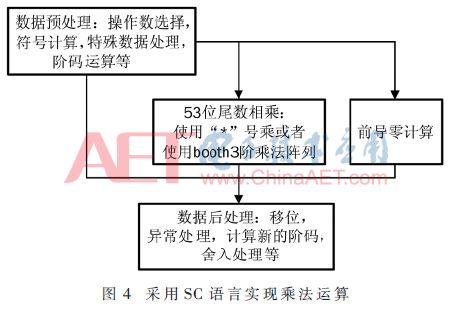

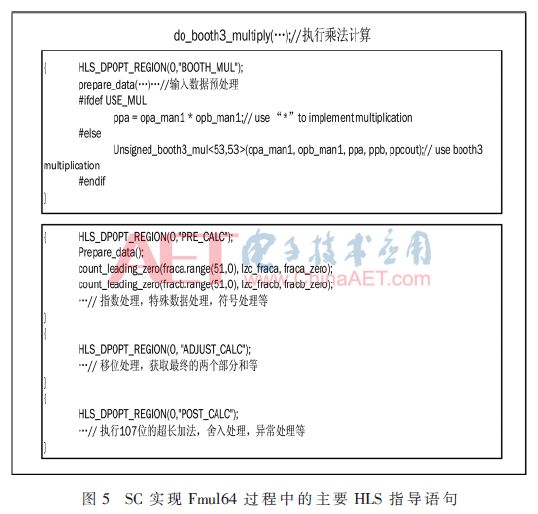

雙精度浮點乘法運算過程如圖4所示。首先對輸入乘法操作數做數據的預處理,然后做尾數相乘的乘法運算,在這里,本文做了架構探索,一種架構是使用3階波茲編碼算法實現雙精度浮點尾數乘法運算;另一種是使用乘號“*”直接完成浮點尾數相乘運算,讓工具來完成乘法運算的具體實現。兩種架構的驗證環境、優化流程是相同的,所以后續設計將以Fmul64波茲編碼設計為例進行介紹,最后會介紹兩者邏輯綜合結果。設計中使用到的高階綜合指導語句(主要是HLS_DPOPT_REGION)如圖5所示。

至此,SC代碼設計已完成,并且按照設計目標的要求使用高階綜合指導語句設置了流水線和時序要求,可以開始后續的驗證和高階綜合處理。雖然設計是使用高級語言SystemC描述,但是其微架構仍然是符合硬件設計和實現規則的,所以需要注意保持良好的SystemC代碼風格非常重要。

3 功能驗證

Stratus HLS工具提供統一的驗證平臺,所以在SC級的測試用例可以同樣用于RTL代碼的驗證。但是,SC設計是不包含時序信息的,所以包含時序的RTL驗證也是必需的,除了在Stratus內回歸測試SC代碼的用例,還將使用已有的UVM平臺,對RTL和SC設計同時驗證,一方面驗證RTL的功能并收集RTL覆蓋率,另一方面一定程度上驗證SC設計和RTL代碼的一致性。所以HLS設計的驗證分為2個方面:

(1)基于Stratus HLS的驗證

①SC行為級模型驗證(SystemC behavioral model)

②綜合的SC RTL模型驗證(Synthesized SystemC RTL model)

(2)基于UVM的SystemC&RTL的驗證

Verilog RTL實現驗證(Verilog RTL implementation)

3.1 基于Stratus HLS的驗證

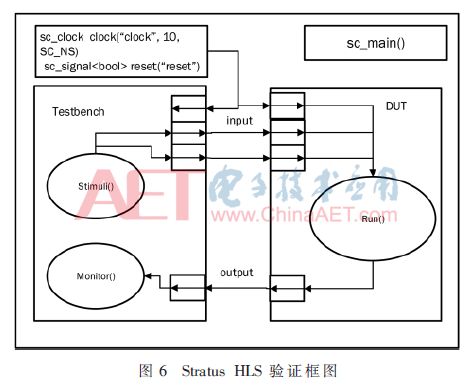

基于Stratus HLS環境,本文使用SystemC建立設計的Testbench環境,其結構框圖如圖6所示。時鐘和復位信號的定義是在主函數內,并連接到測試模塊和待測設計模塊。Testbench中共實現兩個進程,Stimuli和Monitor。Stimuli進程里調用SystemC語言提供的隨機數據生成函數,生成測試的隨機數據。Monitor進程實現簡單的雙精度乘法運算模型,用于待測設計的參考模型,并在此處監測DUT的結果輸出,獲得DUT結果并與參考模型結果做比對,判斷結果的正確性。Stratus HLS工具內可以自動實現對SC設計和RTL設計使用同一個Testbench驗證,只要在project.tcl中定義不同的define_sim_config時,指定為RTL_C是對SC設計驗證或者指定RTL_V是測試高階綜合生成的RTL模型。

3.2 基于UVM的SystemC&RTL驗證

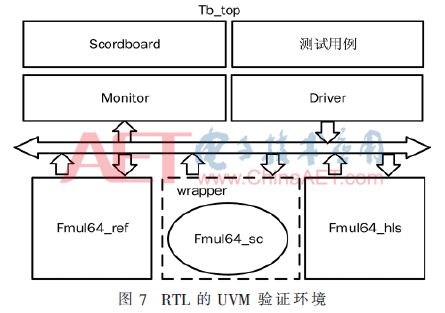

UVM驗證環境是既有的乘法運算驗證環境,如圖7所示,可以對Fmul64_hls設計做完整的功能驗證、覆蓋率收集、斷言監測,同時將SC設計也放到了驗證環境里,但是需要對其外包一個殼,可以由Stratus工具自動生成。此部分功能驗證即如圖1 Stratus HLS設計流程的設計階段2中的功能驗證2,因為高階綜合生成RTL代碼的可讀性較差,所以如果測試用例結果不一致,尤其SC設計的結果也報錯的話,則需要將測試用例轉到Stratus HLS環境下進行調試。

4 性能評估

4.1 優化設計

Stratus HLS在將SC設計轉化為RTL代碼時,由于評估的謹慎性,會給出更加悲觀的結果,因此本文選擇使用邏輯綜合工具評估HLS設計的PPA檢查,邏輯綜合約束參考設計實際實現要求,所以比HLS工具中的邏輯綜合約束設置得更加細致,最后根據邏輯綜合結果來決定是否做設計優化的迭代。

在時序較為緊張的時候,Stratus通常需要很長的時間來做高階綜合優化和調度,這就使設計優化迭代的時間非常長,是違背使用高階綜合工具提高設計效率初衷的。但是Stratus提供多種有效的數據路徑優化方法,可以有效地改善路徑延遲,提高高階綜合效率。比如在設計優化迭代過程中添加DPOPT,如圖5 SC實現Fmul64過程中的主要HLS指導語句所示。DPOPT會調用內部集成的邏輯綜合工具優化這部分設計,而且DPOPT通常會使Stratus綜合一版RTL用時大為縮短,從而大幅提高優化設計的效率。

4.2 低功耗優化

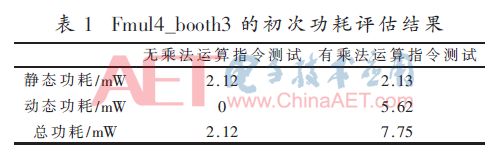

Stratus工具自帶低功耗優化選項,可以自動完成寄存器門控時鐘的插入、時鐘樹優化、狀態機優化等。本文的設計是運算功能模塊,要求在沒有此模塊運算指令的情況下,模塊完全關閉,動態功耗為零;有乘法運算指令的情況下,動態功耗和靜態功耗能夠盡可能小。Fmul4_booth3的初次功耗評估結果如表1所示。

通過上述數據,可以了解到Fmul64_HLS設計在無乘法運算時,滿足動態功耗為零的要求,但是在有乘法運算指令時的功耗卻比較大,不滿足功耗要求,需要對功耗做進一步的優化。分析設計發現DPOPT功耗和資源共享都會引起功耗的增加,所以在project增加以下選項優化功耗:

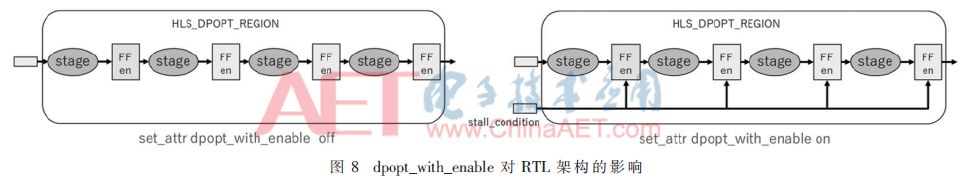

(1)set_attr dpopt_with_enable on

(2)set_attr sharing_effort_parts low

dpopt_with_enable對RTL架構的影響如圖8所示。

顯然dpopt_with_enable=on的RTL架構是對靜態功耗的優化大有幫助的。

sharing_effort_parts =low 會停止演算器的共享。經分析,這個選項可以減少不必要的演算器的共享從而可優化動態功耗以及時序。優化之后的Fmul64_booth3功耗如表2所示。

可以看到通過設置優化選項,靜態功耗和動態功耗均有所優化,其中靜態功耗約優化了5%,動態功耗優化了約39%。寄存器門控比率達到100%,完全由工具完成寄存器門控時鐘的插入和低功耗優化,提高設計效率。

4.3 邏輯綜合結果

高階綜合設計的RTL功能驗證正確后,則設計可以做邏輯綜合。對兩種Fmul64架構分別作了邏輯綜合,在28 nm工藝下,邏輯綜合結果如表3所示。

Stratus HLS給出的面積評估結果與邏輯綜合工具的結果有所不同,經分析,Stratus HLS綜合約束并不嚴格,所以面積、延遲的評估數據存在誤差。而對比兩種架構綜合結果,可以看到Fmul64用乘號代替波茲編碼算法的設計面積上更優化,而時序結果相對較差,但是,其在設計時間的節省是非常顯著的。

5 結論

Stratus HLS工具改變了設計的抽象層次,所以其在工程中的應用流程與傳統RTL設計是有區別的,驗證環境、調試流程、驗證收斂的依據、邏輯綜合優化的時間等問題的解決提前到了算法級,而且可以將微架構的探索加入到設計流程,不變的是設計人員仍然需要從硬件的角度考慮SC代碼的微架構設計。Stratus HLS工具強大的狀態機自動化設計、資源自動調度和共享、低功耗優化等功能,使設計人員能夠將更多的時間用于架構探索或者算法優化,極大的縮短設計周期,拓展設計人員可控制設計規模上限,滿足工程項目的時間進度要求,也增強了我們在工程項目中推廣使用高階綜合工具的信心和決心。

-

cpu

+關注

關注

68文章

10904瀏覽量

213027 -

微處理器

+關注

關注

11文章

2274瀏覽量

82777 -

人工智能

+關注

關注

1796文章

47682瀏覽量

240300

原文標題:【學術論文】Stratus HLS工具在高性能雙精度浮點乘法設計中的應用流程

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

GSM和大家聊聊使用ISE進行綜合與優化一點事情(完成)

移動通信天線性能測試問題的探討及優化

Linux和Android系統故障和優化性能的方法和流程探討

差動放大器的性能優化方法

芯片設計流程及工具

HLS高階綜合的定義與解決辦法

TD-SCDMA網絡性能評估與優化

芯片驗證分析及測試流程優化技術

探討高階綜合完成產品前端設計、驗證、優化、性能評估的方法和流程

探討高階綜合完成產品前端設計、驗證、優化、性能評估的方法和流程

評論