跳頻通信技術是一種擴頻技術,也是最常用的一種擴頻抗干擾技術,通過載波頻率在一定的范圍內按某種序列進行跳變,使信號頻譜得以擴展,以抑制信道中的干擾。跳頻頻率合成器是實現跳頻通信的核心部件,它直接關系到跳頻通信的性能,其主要指標有相位噪聲、鎖定時間、跳頻帶寬、頻率數目等,其中又以相位噪聲和鎖定時間最重要,他們直接關系到跳頻系統通信質量和抗干擾能力。

1 鎖相環頻合器相位噪聲的分析

1.1 鎖相環(PLL)頻合器各功能部件相位噪聲的估算

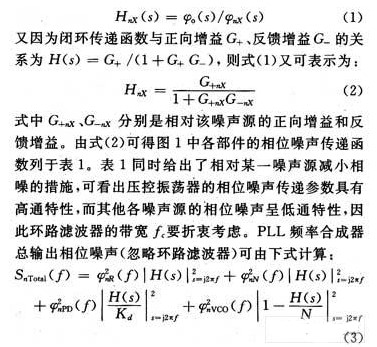

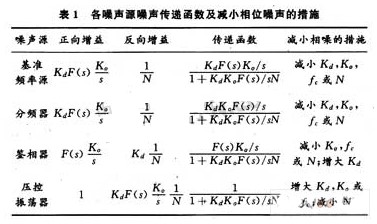

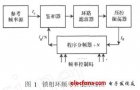

PLL頻合器各功能部件對相位噪聲均有貢獻。分析和估算各部件對總相位噪聲影響的方法是利用鎖相環線性時不變模型,把各個功能塊看成無噪聲,并將噪聲信號加到PLL各功能塊的求和節點,如圖1所示。假定各噪聲源是獨立的,先求出每一部件在輸出端的相位噪聲,再利用疊加法確定PLL頻合器輸出端總的相位噪聲,且在求某一噪聲源影響時,令其他噪聲源輸出為零。各部件在輸出端相位噪聲是通過各自的傳遞函數來求得的。如設某一相位噪聲源為φnX,輸出相位噪聲為φo(s),則φnX到輸出端的傳遞函數為:

1.2 PLL頻合器相位噪聲仿真

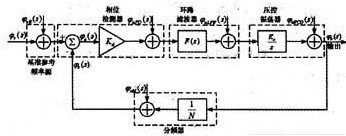

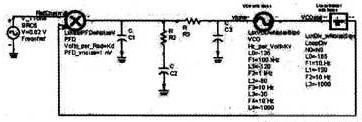

我們利用ADS仿真軟件,驗證上述分析得出的結論。采用電荷泵三階無源環路濾波器,設定電路的原始參數為環路帶寬10 kHz,Kd=1/10π,Ko=1 MHz/V,分頻比為1 000。為了分析環路參數變化對輸出相位噪聲的影響,首先根據原始數據進行仿真,然后分別改變其中的某一參數,仿真變參數后對系統輸出的影響。

仿真電路如圖2所示,仿真結果見圖3,圖中設頻標m1~m7,分別對應頻率1 Hz,100 Hz,1 kHz,100 kHz,1 MHz和10 MHz。

仿真結果中變參數數據與原始數據比較:在環路帶寬內(頻標m1~m3),N的增加增大了相位噪聲,Kd的增加減少了m2~m3處的相噪,而Ko的增加對帶內的相噪影響不大;在環路帶寬外,Ko的增加增大了m4~m6處的相噪,Kd和N的增加對相位噪聲沒什么影響(m4~m7處);環路帶寬fc增加一倍,則增加了m4~m7的相噪,而fc減少一倍,則減少了m4~m6處的相噪。

2 鎖相環頻合器鎖定時間的分析

鎖定時間與環路帶寬成反比,帶寬越大,鎖定時間越短,系統跟蹤性能越好。分析鎖定時間,首先要得出環路濾波器的傳遞函數。對于圖2中電荷泵三階無源環路濾波器,其傳遞函數形式為:

3 S波段寬帶快速跳頻頻合器的實現

3.1 技術指標及方案選擇

跳頻頻合器主要技術指標:輸出頻段S波段,頻帶范圍500 MHz;頻率轉換時間<120μs;相位噪聲在偏離載波1 kHz,10 kHz,100 kHz處分別小于-70 dBc/Hz,-80 dBc/Hz,-90 dBc/Hz。

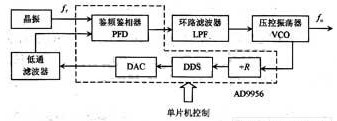

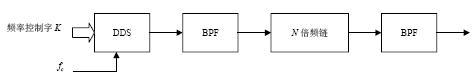

我們采用了DDS分頻的PLL組合頻率合成器技術方案,選用ADI公司的AD9956芯片,該芯片集成了DDS與PLL兩部分,DDS作為頻合器中的分頻器,內部時鐘頻率可達400 MSPS,14位的D/A轉換器,48位的頻率調制字,PLL RF分頻器輸入頻率范圍1~2700 MHz,設計方案見圖4。

3.2 頻合器相位噪聲及鎖定時間可行性論證

3.2.1 輸出總相位噪聲可行性的分析

由PLL頻合器基本工作原理可知,頻合器環路帶寬內相位噪聲與基準頻率源、鑒頻鑒相器噪聲基底、分頻器輸出信號有關,而帶外的相噪與VCO有關。

AD9956芯片的相位噪聲來自鑒頻鑒相器噪聲基底和DAC輸出的相位噪聲,這里DAC輸出信號為PLL頻合器分頻器的輸出信號。AD9956的鑒頻鑒相器噪聲基底在工作頻率為50 kHz,2 MHz,100 MHz,200 MHz時分別為-149 dBc/Hz,-133 dBc/Hz,-116 dBc/Hz,-113 dBc/Hz;AD9956中DAC輸出頻率為51.84 MHz時,偏離載波10 Hz,100 Hz,1 kHz,100 kHz,>1 MHz處的相位噪聲分別為-119 dBc/Hz,-125 dBc/Hz,-132 dBc/Hz,-142 dBc/Hz,-150 dBc/Hz,-155 dBc/Hz。由于DAC具有低相位噪聲性能,基準頻率源通常又采用穩定度高、相位噪聲低的晶振,所以頻合器帶內相位噪聲主要取決于AD9956中鑒頻鑒相器的噪聲基底,其理論計算值由下式得到:

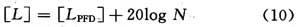

式中[?]表示對數值,N為系統的分頻比,[LPFD]為所使用鑒相頻率噪聲基底的分貝數。設鑒相頻率為25 MHz,可推算噪聲基底-122 dBc/Hz,設N=92,因此由式(10)得帶內相位噪聲為:

根據理論計算值,如選擇合適的環路帶寬是能滿足指標要求的,但由于頻率高、頻帶寬,且要考慮獲得快速鎖定的大環路帶寬,因此滿足指標的相位噪聲富裕量不大,在器件選擇、PCB設計時要周密考慮,盡量達到理論計算值。

3.2.2 跳頻鎖定時間可行性分析

跳頻鎖定時間的估算包括DDS的頻率轉換時間、PLL轉換時間以及控制電路的轉換時間。DDS的頻率跳變時間與PLL轉換時間和控制電路轉換時間比起來要小得多,因此可以忽略。

PLL頻率轉換時間與環路狀態有關。采用電荷泵三階無源環路濾波器,設環路帶寬fc=100 kHz、頻率容忍度ε=500 kHz,利用式(9)可得跳頻間隔500 MHz時的頻率轉換時間為28μs。

AD9956的狀態和頻率控制字采用串行方式輸入,要對32 b功能控制寄存器CFR1、40 b功能控制寄存器CFR2、64 b頻率控制寄存器PCR0和各自的8 b地址信息,總共寫入160 b的有用信息。為了減小系統復雜度,使用單片機產生的時鐘,在每次對AD9956寫入1 b有用信息時,需要三個周期的時鐘控制,160 b有用信息就需480個時鐘周期,計算頻率控制字和單片機控制需要40個時鐘周期,合起來一次跳頻控制需要520個時鐘周期。如單片機采用8 MHz晶振作為時鐘,控制電路的轉換時間為:

如果提高時鐘頻率,可進一步減小控制電路的轉換時間。因此合理的選擇環路中有關參數,鎖定時間是能達到指標要求的。

3.3 測試結果

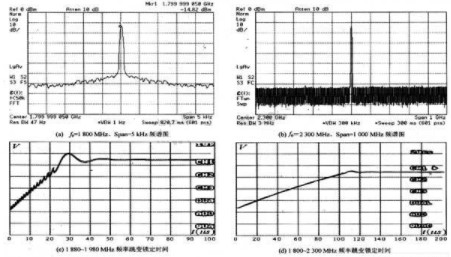

相位噪聲的測試結果:在工作頻率范圍內,偏離載波1 kHz,10 kHz,100 kHz時的相位噪聲分別小于-73 dBc/Hz,-81dBc/Hz和-93 dBc/Hz,且整個輸出頻帶內雜散輸出均小于-70 dBc。圖5(a),圖5(b)分別示出了f0=1 800 MHz,f0=2 300 MHz時的相位噪聲測試頻譜圖,從圖5(b)可看出在1 000 MHz的頻率范圍內對雜散的抑制很好。

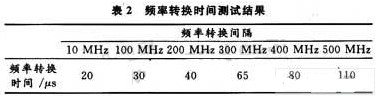

頻率鎖定時間測試結果:工作頻率范圍內最大的頻率跳變(500 MHz)鎖定時間為110 μs,表2示出了測試結果。圖5(c),圖5(d)分別示出了頻率跳變范圍為1 880~1 980 MHz,1 800~2 300 MHz VCO測量電壓的變化曲線。

4 結語

跳頻頻率合成器設計和制作的重點之一是要解決頻率捷變快速鎖定的問題,文章對鎖相環頻合器的相位噪聲和鎖定時間進行了分析,并進行了仿真;采用基于DDS分數分頻的鎖相環頻合器方案,實現了S波段寬帶跳頻頻合器。試驗結果表明,采用該方案的頻率合成器頻率轉換速度快、相噪低、頻譜純度高,同時滿足低功耗、小型化要求,驗證了該方案的合理性和實用性。

-

噪聲

+關注

關注

13文章

1126瀏覽量

47517 -

仿真

+關注

關注

50文章

4124瀏覽量

134005 -

pll

+關注

關注

6文章

781瀏覽量

135333

發布評論請先 登錄

相關推薦

PXI 3010艾法斯頻率合成器

基于鎖相環CD4046的跳頻頻率合成器設計

鎖相環頻率合成器關鍵指標和優化方法

跳頻頻率合成器的性能指標及仿真分析

跳頻頻率合成器的性能指標及仿真分析

評論