1 、引言

現(xiàn)代 IC(Integrated Circuit)設計的主導思想之一就是設計同步化,即對所有時鐘控制器件(如觸發(fā)器、RAM等)都采用同一個時鐘來控制。但由于現(xiàn)代IC芯片的規(guī)模越來越大,包含極其豐富的觸發(fā)器,不同電路的時鐘驅動源存在頻率和相位的差異,在實際的設計中實現(xiàn)完全同步化的設計非常困難,很多情況下不可避免地要完成數(shù)據(jù)在不同時鐘域間的傳遞(如高速模塊和低速模塊之間的數(shù)據(jù)交換)。這時,亞穩(wěn)態(tài)問題是異步數(shù)據(jù)傳輸過程面臨的主要問題,如何避免亞穩(wěn)態(tài)的產(chǎn)生,保持系統(tǒng)的穩(wěn)定,順利完成數(shù)據(jù)的傳輸就成為一個重要的問題,這也是異步電路設計中最為棘手的問題。異步FIFO(First In First Out)是解決這個問題一種簡便、快捷的解決方案。

2、 異步FIFO介紹

異步FIFO廣泛應用于計算機網(wǎng)絡工業(yè)中進行異步數(shù)據(jù)傳送,這里的異步是指發(fā)送用一種速率而接收用另一速率,因此異步FIFO有兩個不同的時鐘,一個為讀同步時鐘,一個為寫同步時鐘。

當數(shù)據(jù)從一個時鐘驅動的模塊進入另一個時鐘驅動的模塊時,問題就有可能出現(xiàn)了。例如當寫時鐘比讀時鐘快時,未讀走的數(shù)據(jù)有可能被新數(shù)據(jù)覆蓋,因而導至數(shù)據(jù)丟失。為此,必須增加一些控制信號和狀態(tài)信號,控制信號如push、pop,狀態(tài)信號如empty,almost-empty,full,almost-full等。

典型的異步FIFO由異步雙端口RAM和控制邏輯構成,后者包含讀指針和寫指針,如圖1。當FIFO中有數(shù)據(jù)而非空時,POP信號用于控制數(shù)據(jù)的讀出,所讀數(shù)據(jù)來自讀指針所指的dualportRAM中的存儲單元,并且讀指針加1。當讀指針趕上寫指針時,F(xiàn)IFO為空并且用empty信號來指示這種情況。當FIFO中有空間而非滿時,PUSH信號用于控制數(shù)據(jù)的寫入,所寫數(shù)據(jù)寫入寫指針所指的雙端口RAM中的存儲單元,并且寫指針加1。當寫指針趕上讀指針時,F(xiàn)IFO為滿并且用full信號來指示這種情況。

3、 亞穩(wěn)態(tài)問題

在數(shù)字集成電路中,觸發(fā)器要滿足setup/hold的時間要求。當一個信號被寄存器鎖存時,如果信號和時鐘之間不滿足這個要求,Q端的值是不確定的,并且在未知的時刻會固定到高電平或低電平。這個過程稱為亞穩(wěn)態(tài)(Metastability)。

當數(shù)據(jù)信號通過兩個時鐘域的交界處時,將會分別由這兩個時鐘來控制信號的值。此時如果兩時鐘信號的敏感沿非常接近并超過了允許的額度,則將出現(xiàn)數(shù)據(jù)信號的不穩(wěn)定,即電路陷入亞穩(wěn)態(tài),也稱為同步失敗。亞穩(wěn)態(tài)是在兩時鐘敏感沿靠得很近、第二級時鐘敏感沿到來時其輸入數(shù)據(jù)不穩(wěn)時發(fā)生,可將其視為僅僅是第二級觸發(fā)器輸入信號不穩(wěn)定所導致的結果。只要使輸入信號穩(wěn)定,就能解決亞穩(wěn)態(tài)問題。不同時鐘域間數(shù)據(jù)傳遞的最重要問題就是亞穩(wěn)態(tài)問題。下面從觸發(fā)器的物理特性方面對亞穩(wěn)態(tài)進行描述。

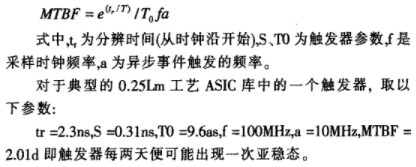

觸發(fā)器進入亞穩(wěn)態(tài)的時間可以用參數(shù)MTBF(mean time between failures)來描述,MTBF即觸發(fā)器采樣失敗的時間間隔,其計算公式為:

由上面的推導可知,一個信號(a_clk)在過渡到另一個時鐘域(b_clk)時,如果僅僅用一個觸發(fā)器將其鎖存,那么用b_clk進行采樣的結果將可能是亞穩(wěn)態(tài)。這也是信號在跨時鐘域時應該注意的問題。

4 、亞穩(wěn)態(tài)問題的解決

雖然亞穩(wěn)態(tài)是不可避免的,但是,下面的設計改進可以將其發(fā)生的概率降低到一個可以接受的程度。

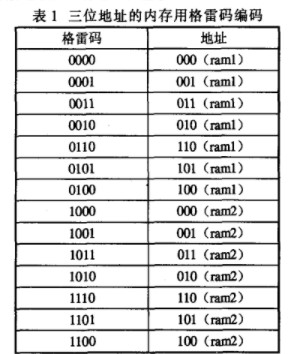

a、對寫地址/讀地址采用格雷碼。由實踐可知,同步多個異步輸入信號出現(xiàn)亞穩(wěn)態(tài)的概率遠遠大于同步一個異步信號的概率。對多個觸發(fā)器的輸出所組成的寫地址/讀地址可以采用格雷碼如表一,其中4位格雷碼的最高位可以用來標示對那個ram進行操作,而實際的操作地址由4位格雷碼的最高兩位異或再加上后兩位得到。由于格雷碼每次只變化一位,采用格雷碼可以有效地減少亞穩(wěn)態(tài)的產(chǎn)生。

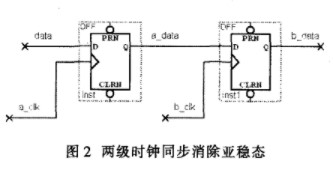

b、采用觸發(fā)器來同步異步輸入信號,如圖2中的兩極觸發(fā)器可以將出現(xiàn)亞穩(wěn)態(tài)的幾率降低到一個很小的程度。但是,正如圖2所示,這種方法同時帶來了對輸入信號的一級延時,需要在設計時鐘的時候加以注意。另外,雖然采用兩級時鐘同步可以在一定程度消除亞問題,但如果在信號從快時鐘域向慢時鐘域過渡的時候,如果信號變化太快,慢時鐘將可能無法對信號進行采樣。所以,在使用兩級時鐘同步的時候,應該使原始信號保持足夠長的時間,以便另一個時鐘域的鎖存器可以正確的對其進行采樣。

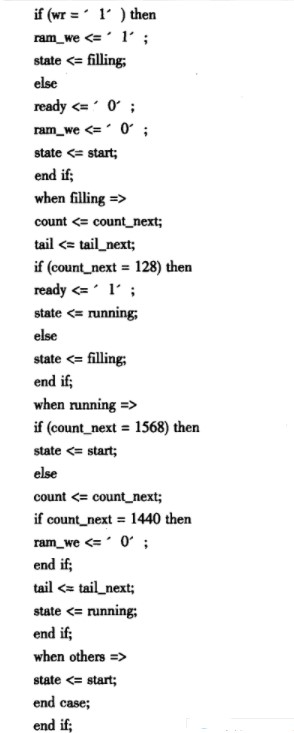

5 、異步FIFO的VHDL實現(xiàn)

VHDL是硬件描述語言的一種,用于數(shù)字電子系統(tǒng)設計。設計者可用它進行各種級別的邏輯設計,可用它進行數(shù)字邏輯系統(tǒng)的仿真驗證、時序分析、邏輯綜合。它是目前應用最廣泛的一種硬件描述語言。目前VHDL語言已經(jīng)得到多種EDA工具的支持,并且已經(jīng)成為IEEE標準,因此利用VHDL語言進行電路設計可以節(jié)約開發(fā)成本和周期。下面以視頻轉換系統(tǒng)中的異步FIFO為例,用VHDL實現(xiàn)如下(假設存儲器的深度為128個像素,即256個字節(jié)):

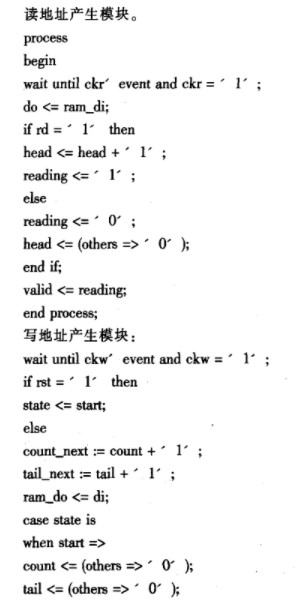

讀地址產(chǎn)生模塊:

6 、結論

本文討論了在ASIC設計中數(shù)據(jù)在不同時鐘之間傳遞數(shù)據(jù)所產(chǎn)生的亞穩(wěn)態(tài)問題,并提出了一種新的異步FIFO的設計方法,并用VHDL語言進行描述,利用Altera公司的Cyclone系列的EP1C6進行硬件實現(xiàn),該電路軟件仿真和硬件實現(xiàn)已經(jīng)通過驗證,并應用到各種電路中。實踐證明它可以解決由于異步產(chǎn)生的錯誤,同時增加了應用的靈活性。

-

控制器

+關注

關注

112文章

16445瀏覽量

179444 -

asic

+關注

關注

34文章

1206瀏覽量

120755 -

觸發(fā)器

+關注

關注

14文章

2003瀏覽量

61347

發(fā)布評論請先 登錄

相關推薦

用FPGA芯片實現(xiàn)高速異步FIFO的一種方法

請問一下異步FIFO的VHDL實現(xiàn)方法

如何利用FPGA和VHDL語言實現(xiàn)PCM碼的解調?

高速異步FIFO的設計與實現(xiàn)

異步FIFO的VHDL設計

Camera Link接口的異步FIFO設計與實現(xiàn)

用VHDL語言實現(xiàn)3分頻電路

用VHDL語言實現(xiàn)3分頻電路(占空比為2比1)

使用Quartus和VHDL語言實現(xiàn)的LPC時序的工程文件

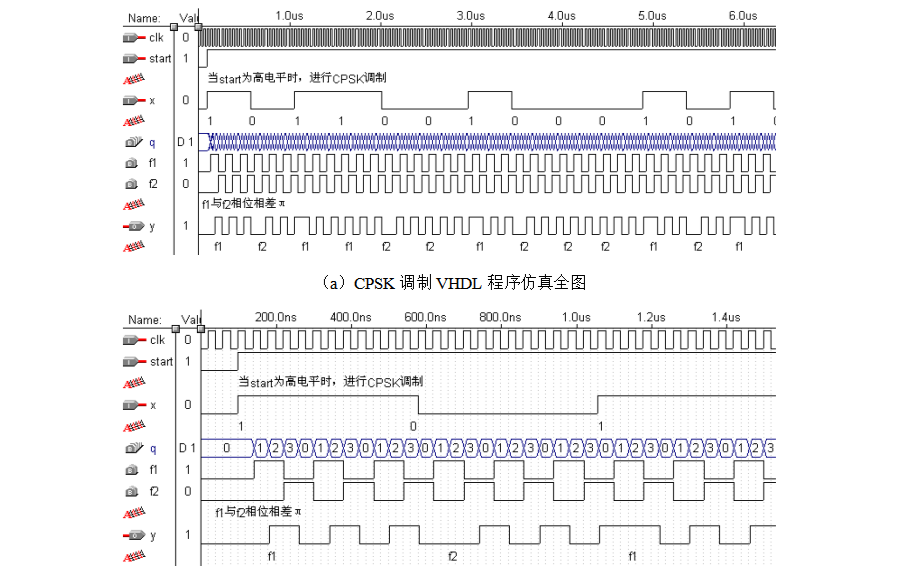

基于VHDL硬件描述語言實現(xiàn)CPSK調制的程序及仿真

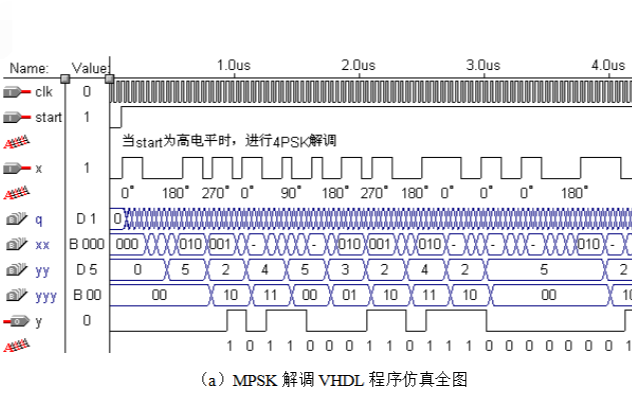

如何使用VHDL硬件描述語言實現(xiàn)基帶信號的MPSK調制

基于VHDL語言實現(xiàn)遠程防盜報警設計

在ASIC中采用VHDL語言實現(xiàn)異步FIFO的設計

在ASIC中采用VHDL語言實現(xiàn)異步FIFO的設計

評論