由于獲取圖像的工具或手段的影響,使獲取圖像無法完全體現原始圖像的全部信息。因此,對圖像進行預處理就顯得非常重要。預處理的目的是改善圖像數據,抑制不需要的變形或者增強某些對于后續處理來說比較重要的圖像特征。

通常根據預處理目的的不同,把預處理技術歸為圖像增強技術和圖像分割技術兩類。圖像對比度處理是空間域圖像增強的一種方法。由于圖像灰度范圍狹窄會使圖像的對比度不理想,可用對比度增強技術來調整圖像灰度值的動態范圍。

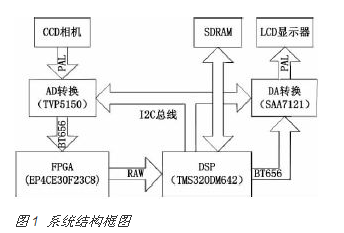

圖像處理通常采用軟件或者DSP(數字信號處理器)來實現。如果利用軟件實現,運行時會耗費較多的PC資源,而且算法越復雜時耗費的資源就越多,對于需要高速處理的情況就不適用了;而如果采用DSP來實現,提高并行性的同時指令執行速度必然會提高,較高的指令速度可能導致系統設計復雜化,并增加功耗和成本。新一代的FPGA集成了CPU或DSP內核,可以在一片FPGA上進行軟硬件協同設計,為實現SOPC提供了強大的硬件支持。本文介紹的是利用FPGA并行處理和計算能力,以Altera FPGA Stratix EP1S40為系統控制的核心實現的SOPC。

系統硬件平臺

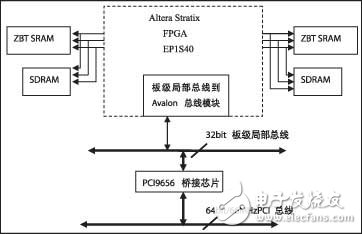

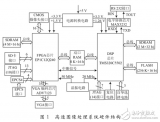

采用基于PCI總線的FPGA開發平臺,結構如圖1所示。板上主要硬件資源有:PCI橋、FPGA、SRAM和SDRAM等其他外設。

PCI橋采用PCI9656橋接芯片實現,用來連接PCI總線與32位/50MHz的板級局部總線;FPGA包括41 250個邏輯單元,14個DSP模塊,112個嵌入式乘法器,4個增強型PLL(鎖相環)和4個快速型PLL等邏輯資源;SDRAM用來存儲圖像數據。Avalon總線模塊完成整個片上可編程系統組件之間的互連。Avalon總線是SOPC設計中連接片上處理器和其他IP模塊的一種簡單總線協議,規定了主、從構件之間的端口連接以及通信時序關系,SOPC Builder來完成整個系統(包括Avalon)模塊的生成和集成。豐富的板級資源可以滿足圖像的高速預處理需求。

系統工作原理

設計采用DMA方式快速傳輸圖像數據,這樣數據的傳輸和處理可以并行起來,使得系統的運行效率大為提高。PC與PCI板卡之間建立軟件環境,在該環境下利用DMA通道把圖像數據從主機通過PCI總線、PCI橋、板級局部總線和Avalon總線傳到SDRAM存儲起來,然后送入算法邏輯模塊進行處理,處理完成后再把圖像數據存儲到SDRAM中,最后再用DMA通道把圖像處理結果傳送回主機。

圖1 基于PCI總線的FPGA開發平臺

建立片上系統中的關鍵模塊

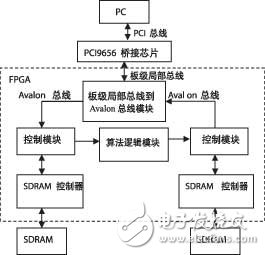

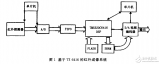

本文設計的圖像對比度增強系統是建立在Stratix EP1S40基礎上的SOPC。該設計在Quartus II 5.0中利用SOPC Builder將系統的工作頻率設為50MHz,器件系列設為Stratix,調用已經建立的IP模塊和算法邏輯模塊,并設置各個模塊的時鐘和基地址,配置生成片上系統。根據任務要求,SOPC結構框圖如圖2所示。

圖2 SOPC結構框圖

圖2中,Avalon總線接口分為主(Master)和從(Slave)兩類,前者具有相接的Avalon總線的控制權,后者是被動的。自定制的Avalon從外設根據對Avalon總線操作方式的不同分為兩類:一類是Avalon從(Slave)外設,只是作為Avalon總線的一個從元件來處理;另一類是Avalon流模式從(Streaming Slave)外設,需要使用Avalon總線的流傳輸模式,外設的設計更復雜。

● 板級局部總線與Avalon總線橋之間的通信模塊

在板級局部總線與FPGA內部Avalon總線橋之間建立通信模塊。由于SOPC內部各模塊之間的邏輯連接是由Avalon總線完成的,所以可以從主機通過PCI總線和板級局部總線訪問SOPC組件。該模塊作為Avalon總線的一個主控接口,對其他Avalon從外設和Avalon流模式從外設進行訪問和控制。

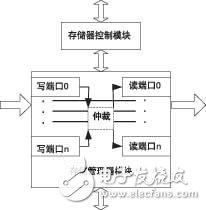

● 控制模塊

控制模塊的工作時鐘獨立于系統時鐘,如圖3所示。包括兩個模塊的設計:(1)用于對SDRAM存儲資源做合理分配的流模式存儲管理器模塊,它作為Avalon流模式從外設,讀寫端口的數量可配置,這些讀寫端口可以以流傳輸模式把圖像數據讀出或寫入SDRAM。(2)存儲器控制模塊,它作為Avalon總線的另一主控接口,對作為Avalon總線從控接口的SDRAM控制器進行控制。

圖3 控制模塊

● 圖像對比度增強算法及VHDL實現

在圖像對比度處理方法中,可以設計出不同的轉換函數。本系統是針對鋸齒形函數轉換設計的,鋸齒形轉換可以把幾段較窄灰度區間拉伸到較寬的灰度范圍內,這種處理可以把灰度變化較平緩的區域也較鮮明地顯示出來,從而增強圖像中感興趣的特征。

該設計對一幀3008×2000像素、數據寬度為8位的灰度圖像進行處理,圖像共有2000行、3008列像素點,行和列均從0開始計起。在系統時鐘上升沿、行有效信號與數據有效信號均有效時,把圖像數據讀入進來,對其做相應處理。每個系統時鐘上升沿讀入一個圖像數據,在第N行像素點處理完后,第N+1行有效信號與數據有效信號必須同時有效才能繼續處理,在對第1999行、3007列像素點處理完畢后,行有效信號與數據有效信號置為無效,此時整幀圖像處理完畢。算法邏輯模塊中需要幀有效計數器和行有效計數器各一個,分別用來對幀和行進行計數,還需要一個像素計數器對某行像素做計數統計。由于該算法邏輯模塊是基于SOPC技術,能夠在SOPC Builder工具中作為自定制模塊調用,需設置兩個寄存器,分別是幀有效計數寄存器和行有效計數寄存器,它們根據Avalon總線地址的不同,同時作為Avalon總線的讀或寫寄存器,從而使自定義模塊可以和Avalon總線進行通信。每輸入一個像素點判斷其灰度值滿足設置的哪個區間范圍并做相應轉換,從而實現一幀圖像的對比度增強處理。根據算法需求,采用VHDL語言對算法邏輯建模,并以Avalon總線從外設的方式在SOPC Builder 中調用。VHDL實現如下。

entity enhancement is

port (iLVAL : in std_logic;

iDVAL : in std_logic;

iFVAL : in std_logic := ‘1’;

iCLK : in std_logic;

iDATA : in std_logic_vector(7 downto 0);

oLVAL : out std_logic; oDVAL : out std_logic;

oFVAL : out std_logic;

oDATA : out std_logic_vector (7 downto 0)

);

end enhancement;

這里iFVAL被置為“1”,說明是對一幀圖像進行處理;iDATA與oDATA是圖像輸入、輸出二進制數據,寬度為8位。

圖像預處理系統的實現

用標準化硬件描述語言VHDL建立FPGA模塊實現。按照自頂向下的設計方法生成各設計階層,將設計任務分解為不同的功能元件,每個元件具有專門定義的輸入輸出端口并執行各自的邏輯功能。該SOPC設計通過以下步驟實現。

(1)利用SOPC Builder工具編譯生成用戶自定制模塊,調用已建立的IP模塊并設置參數,配置生成片上系統;

(2)在頂層VHDL文件中調用模塊并示例化,進行信號連接;

(3)對整個系統進行管腳等約束設置,全編譯并進行行為和時序驗證;

(4)下載和硬件調試完成。

結束語

該系統對實驗室在光線較弱情況下所拍的一幀3008×2000灰度圖像進行對比度增強處理,處理前后如圖4、5所示。在SOPC系統時鐘為50MHz時,對于輸入大小為3008×2000像素點的灰度圖像,每一幀的處理時間為T=(1/(50×106))×3008×2000=0.120 32s。

圖4 原圖像

圖5 處理后圖像

而在3GHz Pentium 4、256MB內存的PC上通過Matlab用代碼實現則需0.9850s。該設計采用FPGA實現圖像預處理系統,與利用軟件處理圖像的方法比較起來,可以更快速地實現對圖像的預處理。同時系統構成靈活,設計中模塊的可重復開發性降低了生產成本、縮短了生產周期,提高了工作效率。

-

dsp

+關注

關注

554文章

8059瀏覽量

350415 -

FPGA

+關注

關注

1630文章

21796瀏覽量

605998 -

總線

+關注

關注

10文章

2903瀏覽量

88390

發布評論請先 登錄

相關推薦

基于FPGA+DSP的三維圖像信息處理系統設計

基于FPGA的高速圖像預處理系統設計

一種基于DSP+FPGA視頻圖像采集處理系統的設計與實現

如何使用FPGA進行圖像實時處理系統的設計

利用FPGA并行處理和計算能力實現圖像預處理系統的設計

利用FPGA并行處理和計算能力實現圖像預處理系統的設計

評論